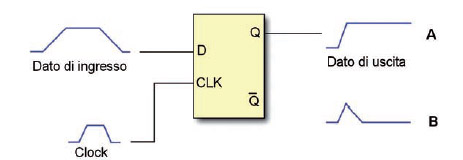

Osservando il flip flop tipo D in figura 1, tutti noi ci aspettiamo che, in corrispondenza del fronte attivo del clock, il livello logico presente sull’ingresso dato, sia trasferito in uscita ed ivi mantenuto stabile.

Figura 1: un FF pilotato in modo non corretto può dare origine

al fenomeno della metastabilità.

Almeno in un caso, purtroppo, le cose possono andare diversamente e riscontrare in uscita al flip flop una transizione instabile di durata incerta, che non viene consolidata in uno stato logico valido. Questa condizione si presenta in generale quando il segnale non rimane costante nelle immediate vicinanze del fronte attivo del clock, causando una violazione dei tempi di setup oppure di hold time.

Ricordiamo che il tempo di setup è il minimo intervallo di tempo in cui il segnale sull’ingresso dato deve rimanere stabile prima del fronte attivo di clock, il tempo di hold è il tempo minimo per cui il segnale di ingresso deve rimanere stabile dopo la transizione del clock. Normalmente in una rete sincrona queste violazioni vengono prevenute da una corretta metodologia di progettazione e successiva verifica dei margini temporali delle reti realizzate. Quando invece si vuole usare un flip flop D per acquisire e sincronizzare un segnale di ingresso asincrono rispetto al clock della nostra rete logica, non abbiamo modo a priori di garantire la robustezza del nostro circuito verso violazioni di setup/hold time e possiamo appunto incorrere in fenomeni di transizioni incomplete, dette metastabilità. Senza entrare nei dettagli matematici, si intuisce come il fenomeno sia casuale e trattabile in termini statistici.

In altre parole, possiamo lavorare per ridurre al minimo l’incidenza del fenomeno, ad esempio scegliendo componenti capaci di lavorare con fronti clock ripidi, ma non possiamo eliminarlo completamente.

Un caso particolarmente interessante di sincronizzazione si trova nei circuiti di acquisizione del segnale di ‘Fail’ nelle macchine di test automatico (ATE). In caso di fallimento logico del test digitale in esecuzione (dato ricevuto diverso ato atteso), questo segnale diattivo (es. livello alto) e tale rimane no o più periodi di clock. Una izione di metastabilità in tale catena di misura comporterebbe problemi nella ripetibilità del test con conseguenti difficoltà di debug e danni economici per lo scarto di dispositivi sotto test in realtà potenzialmente buoni o ancora peggio, il mancato scarto di componenti non perfettamente funzionanti con possibile fallimento degli stessi nell’applicazione finale.

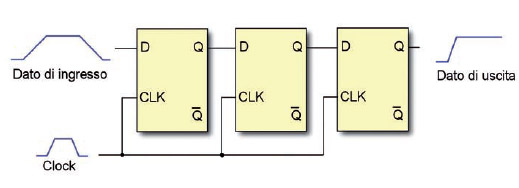

Lo scenario è complicato ulteriormente dalla possibile dipendenza dell’insorgere del fenomeno da condizioni ambientali quale temperatura e rumore di fondo. L’aggiunta di un Flip Flop in cascata riduce a livelli minimi la probabilità di un evento metastabile. Tale probabilità è praticamente ridotta a zero nell’applicazione ATE grazie all’adozione di un circuito di sincronizzazione a tre stadi, figura 2.

Figura 2: circuito di sincronizzazione a tre stadi.

Il prezzo da pagare per tale irrobustimento è il tempo di latenza nell’acquisire lo stato di ingresso, dovuto alla propagazione tra i tre stadi, accettabile in questa applicazione, ma da verificare caso per caso in altre situazioni.

Vi segnalo questo link come approfondimento http://it.emcelettronica.com/il-problema-del-cdc-clock-domain-crossing-negli-fpga