Sul blog di Elettronica Open Source puoi leggere non solo tutti gli articoli Premium riservati agli abbonati Platinum 2.0 e inseriti nella rivista Firmware 2.0 (insieme ad articoli tecnici, progetti, approfondimenti sulle tecnologie emergenti, news, tutorial a puntate, e molto altro) ma anche gli articoli della Rubrica Firmware Reload. In questa Rubrica del blog abbiamo raccolto gli articoli tecnici della vecchia rivista cartacea Firmware, che contengono argomenti e temi evergreen per Professionisti, Makers, Hobbisti e Appassionati di elettronica. I convertitori AD rappresentano una pietra miliare dell’elettronica moderna senza la quale l’elaborazione numerica e la trasmissione digitale dei segnali non sarebbero nemmeno pensabili. In questo articolo ne discuteremo le architetture. Particolare enfasi sarà data ad una serie di considerazioni sui convertitori AD più diffusi nell’elettronica applicata: gli ADC ad approssimazioni successive (SAR).

PRINCIPALI PARAMETRI CARATTERISTICI DI UN ADC

Gli ADC sono caratterizzati da tempi di conversione che variano da qualche nanosecondo alle centinaia di millisecondi in funzione dell’architettura e della tecnologia implementativa. A prescindere da ciò, i principali parametri che ne delineano il comportamento e le prestazioni sono:

Caratteristica di trasferimento: è la tipica curva a gradinata che esprime la relazione fra i campioni della tensione analogica di ingresso (asse orizzontale) e i codici binari di uscita (asse verticale). La curva interpolatrice della caratteristica, cioè della gradinata, passante per i punti medi dei tratti orizzontali è teoricamente una retta.

Valore di fondo-scala VFS (Full Scale Value): generalmente viene fissato dall’esterno mediante un apposito terminale e individua il massimo valore convertibile del segnale.

Tempo di conversione: è il tempo che intercorre fra l’istante in cui il convertitore preleva un campione del segnale (tensione analogica di ingresso) e l’istante in cui presenta sulle linee di uscita il codice binario frutto della conversione del campione. Si tratta di un tempo che deve necessariamente essere minore del periodo di campionamento, il cui valore dipende dalla realizzazione architetturale del convertitore, dalla tecnologia implementativa della circuiteria dell’ADC e dalla frequenza di clock che, applicata al convertitore, ne scandisce i passi di conversione (e che non va confusa con la frequenza di campionamento). Minore è il tempo di conversione e maggiore è la frequenza dei segnali che il convertitore è in grado di convertire.

Risoluzione: è la minima variazione di segnale in grado di determinare la variazione dell’LSB, cioè del bit meno significativo del codice di uscita. L’LSB corrisponde al passo di quantizzazione, per cui la risoluzione coincide con il passo di quantizzazione. Vista dal punto di vista del segnale digitalizzato è il numero n di bit di codifica. Al crescere del numero di bit decresce il passo Q di quantizzazione per cui, elevato numero di bit significa LSB più piccolo e quindi maggiore risoluzione.

Esempio:

- Dinamica compresa tra 0 e 20 volt;

- Risoluzione dell’ADC 12 bit è 212 = 4096 livelli di quantizzazione;

- La differenza di potenziale tra due livelli adiacenti è 20V / 4096 = 4,88 mV

Nella pratica, l’elevata risoluzione da sola non può consentire di recuperare problematiche derivanti da un cattivo rapporto segnale/rumore. Questo perché i bit meno significativi del codice di uscita risulteranno comunque determinati dal rumore piuttosto che dal segnale, soprattutto se si tratta di convertitori veloci che non potranno beneficiare di effetti di integrazione.

Formato dei dati in uscita: il codice di uscita può essere presentato in formato parallelo o seriale, può essere inoltre di tipo binario puro, BCD (codifica utile quando l’uscita del convertitore deve essere visualizzata in forma decimale), GRAY (adatto soprattutto a convertitori molto veloci poiché la transizione da un valore al successivo comporta la variazione di un solo bit) o di altro tipo. Importanti risultano anche alcuni parametri elettrici come l’impedenza di ingresso (tipicamente compresa tra qualche kohm e centinaia di Mohm) e soprattutto l’accuratezza della conversione inficiata non solo dall’errore di quantizzazione ma anche da errori di linearità, di offset e di guadagno oltre che la sensibilità alla temperatura, il rapporto segnale/rumore (SNR) ed il cosiddetto ENOB (numero effettivo di bit).

PRINCIPALI ARCHITETTURE DEI CONVERTITORI A/D

Di seguito discutiamo le caratteristiche principali delle diverse architetture di ADC dando maggiore enfasi all’ADC SAR che è il più diffuso in assoluto in campo applicativo per i motivi che esporremo.

CONVERTITORI A/D A VALORE ISTANTANEO (A/D PARALLELO O “FLASH”)

Adottano alla lettera il concetto di caratteristica di trasferimento. Infatti, lo schema di principio è abbastanza semplice: se si deve convertire un valore di tensione in un certo numero N di bit è sufficiente:

- discriminare 2 elevato alla N diversi livelli di tensione;

- codificarli;

- verificare in quale dei passi di quantizzazione cade il valore da convertire;

- assegnargli il codice corrispondente.

La cosa più logica da fare è allora quella di utilizzare un sufficiente numero di comparatori e di utilizzare le uscite di questi come ingressi di un encoder che trasformi i livelli risultanti dalle comparazioni in codice numerico binario ad n bit. Si ottiene così l’architettura di Figura 1.

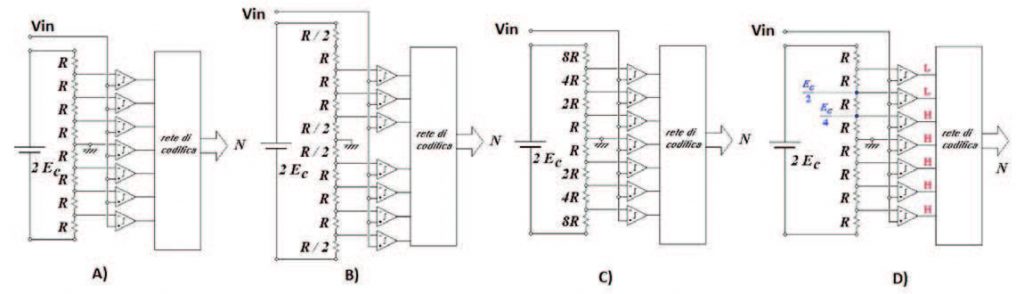

Figura 1: ADC Flash con quantizzazione uniforme non silenziata (A); con quantizzazione uniforme silenziata (B); con quantizzazione non uniforme (C); Esempio di conversione per Vin compresa tra Ec/2 ed Ec/4 (D)

In sintesi, il partitore resistivo genera le tensioni di riferimento, la serie di comparatori individua l’intervallo di quantizzazione cui appartiene il campione e la rete combinatoria esegue la codifica in formato binario (puro, con offset, complementato a due, GRAY, BCD o di altro tipo a seconda delle applicazioni). Il numero di comparatori necessari cresce esponenzialmente con il numero di bit, motivo per cui raramente questi ADC presentano più di 8 bit di risoluzione. La rete che genera i valori di riferimento viene dimensionata differentemente in funzione del numero di bit di codifica, del fatto che si adotti quantizzazione uniforme o meno e del fatto che la caratteristica di trasferimento richiesta sia silenziata o meno (Figura 1). All’incertezza di quantizzazione si aggiungono quelle provocate dall’instabilità della tensione Ec, dalla non linearità del partitore resistivo e dall’offset dei comparatori (che determina uno spostamento delle soglie). Le variazioni di resistenza prodotte dalle escursioni di temperatura invece influiscono poco, dal momento che non vi è motivo per cui i resistori abbiano differenti coefficienti di temperatura. Il limite è rappresentato dal fatto che per realizzare un convertitore ad n bit, sono necessari ben 2n resistori, (2n-1) comparatori ed una rete combinatoria di codifica con (2n-1) ingressi ed n uscite. La circuiteria è quindi molto dispendiosa ma l’architettura assicura tempi di conversione ridottissimi da cui la possibilità di campionare a frequenze molto elevate (ordine dei GSa/s) e quindi di convertire segnali ad alta frequenza. E’ il caso della digitalizzazione di immagini video (f≈5MHz). Ovviamente, non solo i costi ma anche i consumi di potenza aumentano esponenzialmente con il numero di bit. Un numero elevato di comparatori parallelati, inoltre, non soltanto aumenta l’area occupata dal circuito sul die ma ne restringe anche la banda passante dal momento che ogni comparatore presenta una certa capacità di ingresso che risulta in questo caso moltiplicata per gli n (effetto di filtraggio passa-basso). Per questo motivo, i convertitori flash difficilmente superano 8 o 10 bit di risoluzione e vengono impiegati solo nelle applicazioni in cui è richiesta elevata velocità di conversione con contenuto numero di bit di codifica. Restano in ogni caso i convertitori più veloci tra quelli presenti sul mercato grazie al fatto che tutti i comparatori eseguono il confronto nello stesso istante (cioè in modo parallelo), riducendo il processo di quantizzazione ad un solo colpo di clock.