La struttura hardware, la logica dei segnali e il funzionamento base del più comune bus industriale: il bus VME (Standard IEEE 1014-1987).

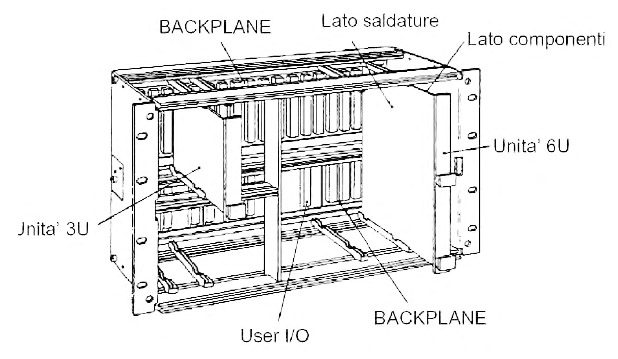

Un crate VME standard può essere rappresentato dalla figura 1 dove vengono visualizzate le principali unità.

L’altezza di un bus VME è espresso in “U”: 1 U = 43.60 mm. La lunghezza, invece, è espressa in mm. Lo spessore, infine, è espresso in “T” o “HP”: 1 HP = 5.08 mm. Possibili misure del bus VME sono:

- 3U * 160 mm (Size A)

- 6U * 160 mm (Size B)

- 6U * 340 mm (Size C)

- 9U * 340 mm (Size D)

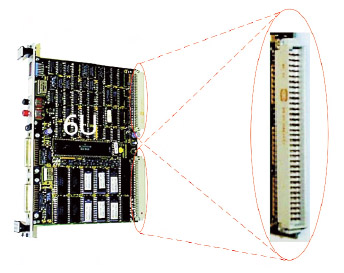

Le schede elettroniche VME (vedi figura 2, 3 e 4) presentano le seguenti caratteristiche:

- formati 3U (100 mm * 160 mm) “Euromechanics” e connettori DIN (P1);

- formati 6U (233.5 mm * 160 mm) “Euromechanics” e connettori DIN (P1 e P2).

LA LOGICA DEI SEGNALI SUL BUS VME

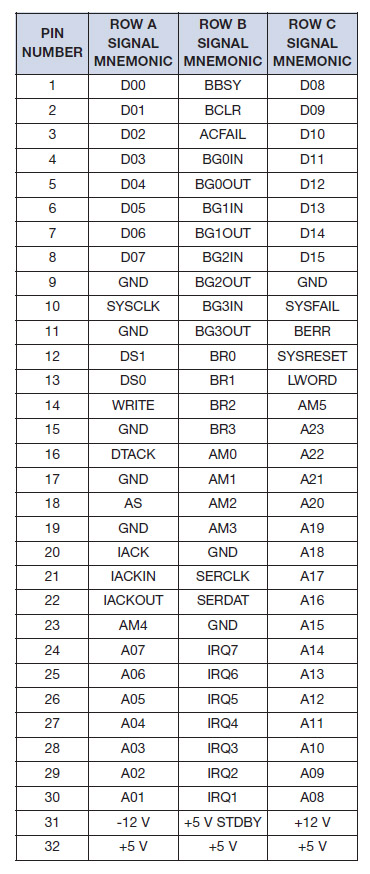

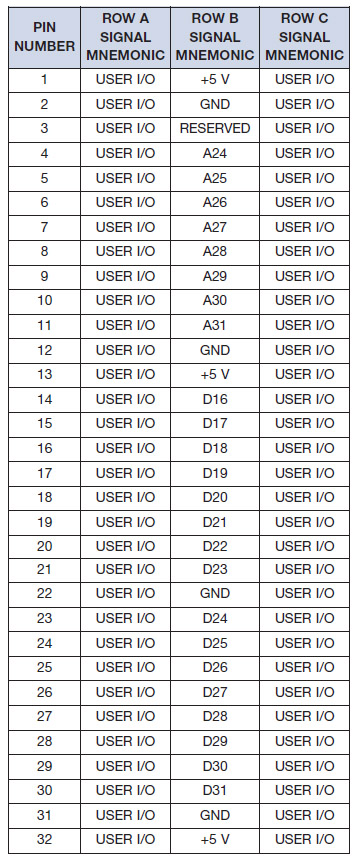

La prima versione del VME (D16/A24) prevedeva schede Europcard di altezza 3U (100 mm) o 6U (233 mm) con un connettore DIN 41612 a 96 pin su tre colonne: a,b e c. Il connettore, che nel formato 6U era montato in alto alla scheda (P1), prevedeva 16 bit per i dati e 24 bit per gli indirizzi. La versione successiva (A32/D32) ha imposto il formato 6U utilizzando 32 pin del connettore DIN 41612 a 96 pin in posizione P2, lasciando per l’utente i rimanenti 64 pin. Uno sviluppo del bus VME è stata introdotta negli anni successivi con una estensione del bus a 64 bit. Nelle tabelle 1 e 2 sono visualizzate le assegnazioni dei pin nei due connettori previsti sulla scheda 6U (A32/E32).

L’assegnazione delle linee ai 4 sottobus nel VME A32/D32 è descritta di seguito.

- Data Transfer Bus

Utilizza tre diversi tipi di linee:

- Indirizzamento (A01-A31, AM0-AM5, DS0, DS1, LWORD);

- Dati (D00-D31);

- Controlli (AS, DS0, DS1, BERR, DTACK, WRITE).

Le altre linee utilizzate sono:

- AS: linea di controllo degli indirizzi.

- LWORD, DS0 e DS1: indicano la misura del tipo di dato (in bit: 8, 16, 32 bit).

- WRITE: indica il tipo di direzione del bus (0 se l’operazione è read, 1 se l’operazione è write)

- DTACK: indica un successo del trasferimento di informazioni sul data bus.

- BERR: indica un errore nel bus durante il tra sferimento di informazioni nel data bus.

- Priority Interrupt Bus

Utilizza le seguenti linee:

- IRQ1-IRQ7, IACK, IACKIN, IACKOUT, nonché quelle A01-A03, AS, DS0, DS1, LWORD e D00-D31, DTACK.

- IRQ1-IRQ7: informazioni sulla richiesta di interrupt.

- D00-D31: informazioni sullo status.

- DATCK: indica che il segnale di status è pronto per poter essere ricevuto.

- A01-A03: indica il livello di interrupt.

- IACK: Un segnale di interrupt è stato ricevuto (IACKIN) ed è pronto a ricevere un segnale di status per procedere ad eseguire le operazioni (IACKOUT).

- Data Transfer arbitration bus

Utilizza le linee:

- BR0-BR3, BG0IN-BG3IN, BG0OUT-BG3OUT, BBSY, BCLR. Le operazioni relative a questo bus vengono svolte dal crate manager posto nello slot 1.

- BR0-BR3: indica il tipo di priorità.

- BCLR: indica che una informazione di maggio re priorità per un sistema è stata richiesta.

- Utility bus

Utilizza le seguenti linee:

- SYSCLK, SYSRESET, SYSFAIL ed ACFAIL.

- ACFAIL: livello di tensione (Volt) basso.

- SYSCLK: il sistema lavora con il suo clock interno di 16 MHz.

- SYSRESET: reset del sistema.

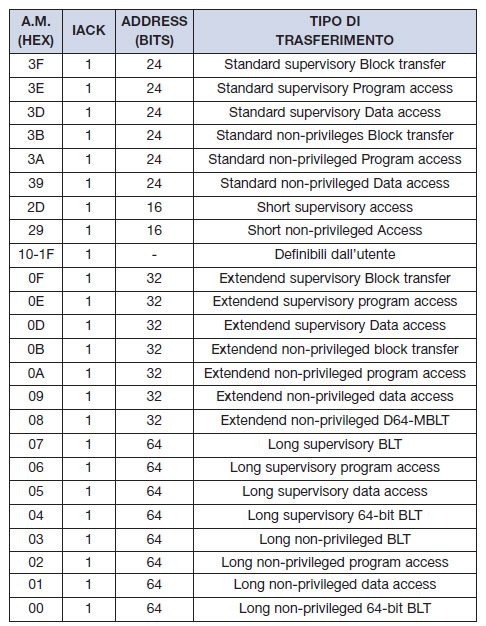

In realtà esiste un quinto bus speciale detto VMSbus che può essere utilizzato per scambiare brevi messaggi urgenti tra moduli o sistemi VME. Questo di solito non viene utilizzato. I segnali che utilizza sono: SERCLK e SERDAT. Il bus VME prevede una linea di errore (BERR) per il riconoscimento di situazioni impreviste ed ha un limite teorico di trasferimento dati di 40 Mbytes/sec. Il bus ha 7 livelli di priorità per le interruzioni. Le potenzialità del sistema di arbitraggio gli consentono di gestire anche un crate di tutte le schede processori ed ha una linea che consente la diagnostica dei guasti, SYSFAIL. Una caratteristica particolare del bus VME sono le 6 linee di “address modifier code”, AM0-AM5 che sono alla base della duttilità di indirizzamento e di gestione dati nel sistema. Ad essi è affidata l’informazione sulla modalità del trasferimento che, può essere “supervisory” e “non-privileged”. In tabella 3 è visualizzata l’assegnazione dei codici degli address modifier.

IL FUNZIONAMENTO DEL BUS VME

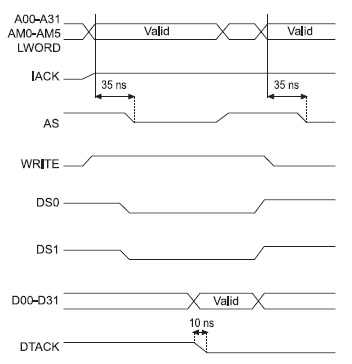

Vediamo da un punto di vista dei segnali il funzionamento del bus VME. In figura 5 è mostrato il diagramma delle temporizzazioni delle singole operazioni sulle varie linee fatte da un master e da uno slave durante un tipico ciclo di lettura dati.

Il trasferimento dati può essere a 8, 16, 24, o 32 bit, asincrono. I cicli di trasferimento dati possono essere:

- single cycle: l’indirizzo viene inviato assieme ad ogni trasferimento dati

- block transfer: un solo indirizzo è inviato per un trasferimento dati multiplo

Considerato che AS* deve rimanere asserito 40 ns per ciascun ciclo e almeno 40 ns fra due cicli, tenuto conto dei ritardi, due cicli di scrittura distano circa 100ns con un rate di circa 10MHz: 4 byte a 10 MHz danno una data rate teorica di 40MBps. La successione delle operazioni nell’ambito del ciclo di lettura è la seguente:

- Il master attiva le linee A01-A32, AM0-AM5, IACK ed LWORD (consideriamo un trasferimento di 32 bit). La linea WRITE deve essere negata trattandosi di un read.

- Il master convalida le linee indirizzi con la transizione verso il basso della linea AS e mette basso la linea DS0 e/o quella DS1.

- Lo slave decodifica l’indirizzo, abilita in uscita il suo registro dati (mette i dati nel bus) e ne da comunicazione al master con la linea DTACK.

- Quando il master ha registrato i dati nel suo latch lo comunica allo slave negando la linea o le linee di data strobe (DS).

- Lo slave risponde togliendo il dato nel bus e negando la linea DTACK.

In figura 6 è visualizzatao il diagramma temporale del ciclo di scrittura nel bus VME.

L’ARBITRAGGIO

Il trasferimento dati da parte del master deve avvenire dopo che è avvenuta la richiesta del bus. Questo avviene asserendo una di quattro linee di richiesta bus. Le linee BR0/BR3 possono essere usate per “prioritizzare” richiesta in sistemi multi-master (figura 7).

L’arbitro, in slot 1, controlla se il bus è occupato tramite la linea BBSY. Una volta libero asserisce una delle 4 linee BGOUT. Se il master riconosce un 1 nella linea BGIN corrispondente al suo BR, asserisce BBSY, altrimenti lo passa a BGOUT per chiudere la catena. Gli arbitri possono usare diversi schemi di arbitraggio:

- PRI: basato sulla priorità

- RRS: Round robin

Se due master usano la stessa linea di richiesta, quello più vicino alla slot 1 ha la priorità, perché riceve per primo il BGIN. Sistemi più moderni permettono un arbitraggio “fair”, cioè ritardano la richiesta se altri master richiedono il bus sullo stesso livello.

IL MECCANISMO DI INTERRUPT

Il modulo di gestione (interrupt handler) tiene sotto osservazione le linee di richiesta (IRQX) e, quando rileva una linea attivata, chiede il controllo del bus. Dopo averlo ottenuto, in risposta al segnale, genera un interrupt acknowledge cycle (figura 8).

Quando il modulo che ha richiesto l’interrupt riceve dal modulo che lo precede lungo il bus il segnale IACKIN, presenta sulle linee dati il vettore STATUS/ID e termina il ciclo asserendo bassa la linea DTACK. Il “vettore” STATUS/ID è un numero che permette di riconoscere quale routine di servizio attivare in presenza di più unità sullo stesso livello di interruzione.

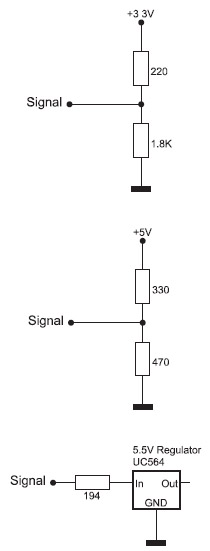

LE TERMINAZIONI

Le terminazioni utilizzate (figura 9) possono essere sia passive, con l’utilizzo di resistori, sia attive con l’utilizzo di componenti elettronici opportuni per stabilizzare la tensione.

Il voltaggio di ogni terminazione presenta una tensione di 2.94 V ± 10%.