I mixed signal controller MSP430 della Texas Instruments si basano su un'architettura RISC a 16 bit. Sono dispositivi a bassissimo consumo adatti per apparecchiature portatili alimentate a batteria. Possono includere le più comuni periferiche digitali e diversi moduli analogici quali ADC, DAC e comparatori. Nell'articolo si esaminerà in particolare la configurazione e l'utilizzo della periferica di conversione A/D a 10bit.

Il core A/D del micro MSP430 di Texas Instruments è un convertitore SAR a 10bit e si trova nelle famiglie MSP430x11x2 e MSP430x12x2. Il multiplexer all’ingresso del convertitore permette di selezionare 8 ingressi analogici single ended oppure quattro segnali interni al microcontrollore e cioè la tensione di alimentazione, il sensore di temperatura incluso nel dispositivo, le tensioni Vref+ e Vref-. In questa periferica si trovano inoltre un riferimento di tensione, un oscillatore dedicato in grado di fornire un clock indipendente al convertitore SAR e l’interfaccia DTC (Data Transfer Controller) per trasferire i dati acquisiti direttamente nella memoria RAM del microcontrollore senza l’intervento della CPU. Il convertitore può essere configurato per acquisizione di un singolo ingresso o sequenziale su più ingressi e può eseguire letture singole o letture periodiche in modo completamente automatico senza l’intervento della CPU riducendo così i consumi totali del sistema. Il primo parametro da definire nella configurazione del convertitore è la tensione di riferimento Vref da utilizzare per le misure. Il riferimento di tensione interno alla periferica può fornire due tensioni 1.25V e 2.5V selezionabili da software. ADC10 utilizza due ingressi di riferimento indicati con Vref+ e Vref. L’ingresso Vref+ definisce il limite superiore della scala analogica associato al valore 0x03FF. Per questo ingresso si può selezionare il riferimento di tensione interno oppure la tensione di alimentazione oppure una tensione di riferimento esterna. L’ingresso Vref- definisce il limite inferiore della scala analogica associato al valore 0x0000. Normalmente questo ingresso è collegato alla massa analogica ma può essere collegato anche a una tensione positiva, inferiore a Vref+, per spostare il limite inferiore della scala e ridurre così l’intervallo di misura. La formula di conversione dell’ADC10 risulta:

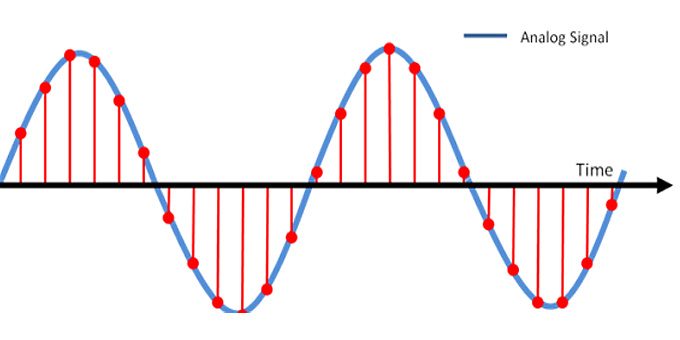

Un altro parametro importante da tenere in considerazione soprattutto se si vuole

![]()

utilizzare il convertitore alla massima frequenza possibile è il sample time Tsample. Tra il canale d’ingresso e il convertitore è infatti interposto un circuito di sample and hold S&H. La capacità del circuito S&H viene inizialmente collegata al circuito d’ingresso e si carica alla tensione analogica presente sull’ingresso attraverso un circuito RC. Successivamente si scollega il segnale in ingresso e si effettua la misura della tensione costante ai capi del condensatore. Le caratteristiche del circuito RC dipendono dalla struttura del canale e dalla resistenza del circuito analogico collegato all’ingresso. Per una misura accurata che sfrutti tutta la risoluzione del convertitore è necessario che la tensione sul condensatore differisca al massimo di 1/2LSB dalla tensione d’ingresso. Questo determina la durata minima della fase di campionamento che dipende dalla costante di tempo RC:

![]()

Il termine K rappresenta il tempo di assestamento del riferimento interno nelle diverse modalità di funzionamento e varia da 800ns a 2.5ms il tempo totale di conversione è definito dalla somma di tre intervalli di tempo:

➤ Il tempo Tsync tra la richiesta di conversione e l’effettivo inizio della conversione. La richiesta di inizio conversione è asincrona e si deve attendere il successivo fronte di clock interno prima di iniziare la nuova conversione.

➤ Il tempo Tsample di acquisizione del circuito di Sample and Hold che dev’essere maggiore del valore calcolato con la formula precedente. Nell’ADC10 il Tsample viene configurato come sottomultiplo del clock della periferica tramite un prescaler dedicato.

➤ Il tempo Tconvert è il tempo di conversione della misura che in questo caso è pari a 13Tclock dove Tclock è il periodo del clock fornito al convertitore. Anche il segnale di clock del convertitore viene configurato come sottomultiplo del clock della periferica tramite un prescaler dedicato.

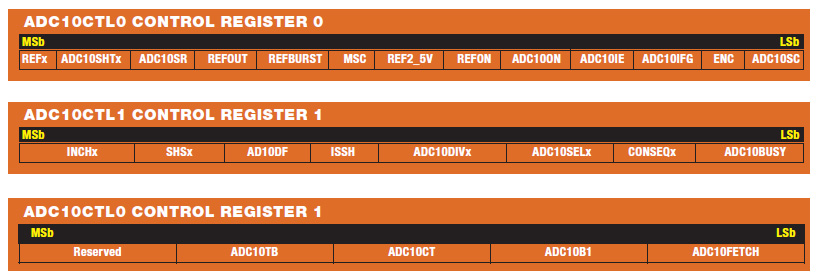

I registri di configurazione della periferica sono ADC10CTL0 e ADC10CTL1 e sono descritti in dettaglio nella tabella1. Per modificare la configurazione si deve innanzitutto porre a zero il bit ENC che disabilita il segnale di trigger di start conversione e attendere la fine della conversione in corso controllando il valore del bit ADC10BUSY. La modalità operativa della periferica è definita dalla coppia di bit CONSEQx, è possibile effettuare acquisizioni in 4 modi differenti:

- Singolo canale

- Acquisizioni ripetute su singolo canale

- Acquisizione su più canali

- Acquisizione ripetuta su più canali

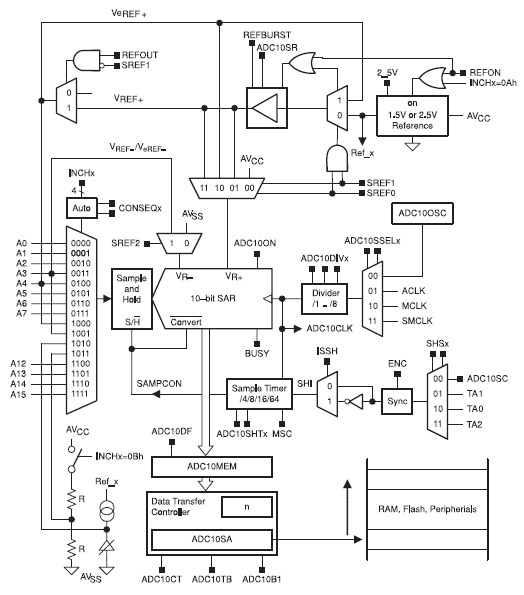

Figura 1: la struttura della periferica di conversione A/D a 10bit del micro MSP430. La periferica è formata da un convertitore SAR a 10bit, un riferimento di tensione selezionabile a 1.25V o 2.5V, un oscillatore indipendente ADC10OSC a 5MHz e una periferica DTC per il trasferimento dei dati direttamente in memoria RAM senza l’intervento della CPU.

Lo start alla conversione può essere dato da software in modo asincrono ponendo a 1 il bit ADC10SC oppure automaticamente utilizzando l’uscita di una delle unità del Timer0 qualora si desideri effettuare delle acquisizioni periodiche. Il risultato di ogni conversione viene memorizzato nel registro ADC10MEM ed è valido quando il bit ADC10BUSY è a zero. La periferica segnala al fine della sequenza di acquisizione impostata ponendo a 1 il bit di interurpt flag ADC10IFG e se abilitato attiva anche il vettore di interrupt associato. Il campo INCHx del registro ADC10CTL1 configura il multiplexer analogico in ingresso e stabilisce quale sia il canale in acquisizione. Se il convertitore è configurato per acquisizioni multiple su più canali, il valore di INCHx viene automaticamente decrementato ad ogni start conversione per consentire l’acquisizione multipla in sequenza dei canali analogici. Quando INCHx raggiunge il valore zero la sequenza di acquisizione termina. Per aumentare la velocità di lettura di una sequenza di ingressi analogici si deve porre a 1 il bit MSC. In questo caso è sufficiente un solo segnale di inizio conversione, la periferica acquisisce automaticamente gli ingressi analogici alla massima velocità senza attendere al termine di una conversione, un nuovo segnale di trigger. Quando si utilizza il convertitore per acquisizioni multiple si deve necessariamente configurare anche l’interfaccia DTC per trasferire il risultato di ogni misura dal registro ADC10MEM alla memoria RAM del microcontrollore.

Tabella 1: i registri della periferica ADC10 e il dettaglio della struttura dei registri di configurazione

L’interfaccia DTC

Il DTC (Data Transfer Controller) trasferisce automaticamente il risultato della conversione A/D contenuto nel registro ADC10MEM nella memoria RAM del dispositivo senza l’intervento della CPU. I registri di configurazione di questa interfaccia sono ADC10DTC0 e ADC10DTC1. Per attivare la periferica DTC è necessario scrivere un valore diverso da zero nel registro ADC10DTC1. Il registro ADC10SA contiene il primo indirizzo della memoria RAM in cui verrà memorizzato il risultato della prima conversione. Durante il trasferimento l’interfaccia DTC blocca la CPU per evitare conflitti sull’accesso al bus del micro ed esegue il trasferimento in un ciclo del clock di sistema MCLK. Al termine del trasferimento il registro ADC10SA viene incrementato di 2 e perciò contiene l’indirizzo della locazione di RAM in cui memorizzare la prossima acquisizione, mentre il registro ADC10DTC1 viene decrementato di uno. Finché il valore di ADC10DTC1 è diverso da zero l’interfaccia DTC dopo ogni nuova acquisizione ripete la sequenza descritta e trasferisce il valore contenuto in ADC10MEM nella locazione di memoria RAM indirizzata dal registro ADC10SA. Quando il valore nel registro ADC10DTC1 è zero la periferica pone a 1 il bit ADC10IFG che segnala la fine della sequenza di acquisizione/memorizzazione e, se abilitato, genera un interrupt che può essere utilizzato come sorgente di wakeup della CPU. Il funzionamento dell’interfaccia DTC può essere modificato configurando due bit del registro ADC10DCT0: Il bit ADC10TB che con sente di ripetere la sequenza di acquisizione automaticamente per due volte memorizzando le sequenze in due blocchi contigui di memoria RAM. Il bit ADC10CT che abilita l’esecuzione della sequenza di acquisizione e trasferimento impostata in modo continuo senza nessuna interruzione. Al termine della prima sequenza di lettura/memorizzazione inizia automaticamente una nuova sequenza che aggiorna le locazioni di RAM interessate dal trasferimento dell’interfaccia DTC trattandole come un buffer circolare. Al termine di ogni ciclo di acquisizione il flag ADC10IFG viene sempre impostato a 1.

Stavo cercando qualche idea per realizzare un volmetro digitale con più input, e mi son imbattuto in questo articolo, scoprendo questo componente a me nuovo, che ritengo molto potente. E pur vero che ci sono microcontrollori con ADC interni, ma il punto forte, sta proprio nella soluzione che il risultato va immagazzinaggio direttamente in memoria pronto per essere elaborato, con tanto di interrupt. Inoltre possibile leggere la V. di alimentazione, temperatura e le V. ref. Direi un ottimo componente.