Negli scorsi anni, con il crescere della densità e della complessità dei dispositivi FPGA si è avvertita l’esigenza di integrare periferiche adatte a gestire in maniera flessibile e precisa i segnali di clock all’interno ed all’esterno del dispositivo. I primi dispositivi di Xilinx integravano soltanto blocchi chiamati “Delay Locked Loop” (DLL), capaci di correggere i ritardi generati nella distribuzione del clock in diverse aree del dispositivo, o anche fuori da esso. I DLL sono capaci di generare ritardi variabili, e quindi se sono controllati da un segnale di retroazione, possono essere utilizzati per ottenere il deskew (allineamento) dei clock, e per la generazione di segnali agganciati in fase ad uno preso come riferimento, o con un sfasamento prefissato e costante.

Introduzione

I DLL impiegati da Xilinx (al seguente link un approfondimento) permettono anche di ottenere un segnale a frequenza doppia rispetto a quello in ingresso. Successivamente sono stati dotati di un’evoluzione del DLL: il Digital Clock Manager (DCM). Questi componenti realizzano le stesse funzioni dei DLL, introducendo alcune interessanti funzionalità aggiuntive. I DCM infatti possono essere usati per condizionare il clock (producendo un segnale con duty cycle al 50%), per sfasare un segnale di clock rispetto ad un altro di intervalli fissi o variabili, eseguire il deskew, e moltiplicare e dividere la frequenza del segnale in ingresso per due coefficienti in modo da ottenere una frequenza arbitraria in uscita. Queste funzioni sono utilizzabili anche congiuntamente. L’introduzione del DCM ha permesso una significativa semplificazione nella progettazione e realizzazione di circuiti complessi, rendendo possibile l’adozione di strategie di clocking avanzate (sintesi di frequenza, allineamento dinamico, interfacciamento di tipo DDR, etc.). Lo schema funzionale di un DCM è mostrato in Figura 1.

Come si può vedere i suoi componenti principali sono una linea di ritardo programmabile (Delay Taps / Phase Shifter) che realizza in pratica un DLL, un sintetizzatore di frequenza (DFS), e la logica di controllo. Gli ingressi di clock sono quelli relativi segnale principale (CLKIN) e quello per il segnale di feedback (CLKFB). Va notato che nonostante i DCM siano in grado di sintetizzare e sincronizzare segnali di clock, essi non hanno nessun effetto sul jitter dei segnali d’ingresso, e possono sintetizzare frequenze soltanto in un insieme di valori piuttosto limitato. Questo è dovuto al fatto che i DCM non contengono un oscillatore, ma si limitano a condizionare il segnale ricevuto. Per superare queste limitazioni, nei dispositivi Virtex-5, Xilinx venne introdotto un PLL vero e proprio, che verrà descritto dettagliatamente di seguito.

IL CLOCK MANAGEMENT TILE

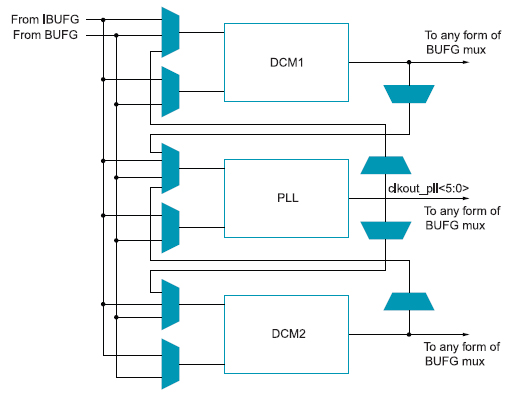

Con i dispositivi Virtex-5, Xilinx ha introdotto un nuovo blocco funzionale dedicato alla gestione dei clock: il Clock Management Tile (CMT). Ciascun blocco CMT è costituito da due DCM, da un PLL e dalle risorse d’interconnessione locale tra questi dispositivi, come mostrato in Figura 2.

I tre dispositivi possono essere utilizzati indipendentemente, o collegati in modo che il PLL fornisca il clock ad uno o ad entrambi i DCM, o viceversa. Il PLL viene utilizzato principalmente come sintetizzatore di frequenza che può coprire un intervallo di frequenze molto amplio. Se si considera il fatto che sia l’ingresso che l’uscita del PLL possono provenire o essere diretti ai DCM si comprende l’enorme flessibilità offerta da questa configurazione (la frequenza sintetizzata può essere moltiplicata, divisa, allineata o sfasata usando separatamente i DCM). Inoltre, dal momento che il PLL genera interamente la frequenza di interesse, piuttosto che condizionare il segnale presente in ingresso, esso permette di ridurre considerevolmente il jitter di un segnale di clock. Nei dispositivi Virtex-5 sono presenti fino a 8 blocchi CMT indipendenti.

IL PLL

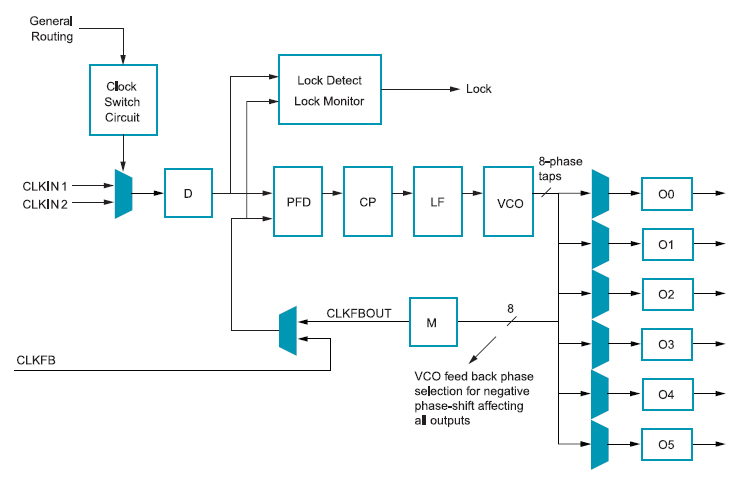

Lo schema del PLL presente nel blocco CMT è mostrato in Figura 3.

La sua struttura è piuttosto classica, esso infatti comprende un contatore programmabile D, un comparatore di fase/frequenza (FPD) che confronta il segnale d’ingresso con quello del percorso di ritorno, una pompa di carica analogica (CP), il filtro d’anello (LF) che livella la tensione all’uscita dalla pompa di carica e determina la banda passante del PLL (quindi la sua velocità di reazione e la sua stabilità), e l’oscillatore controllato in tensione (VCO) che produce la frequenza in uscita. L’uscita del VCO in realtà è costituita da 8 segnali alla stessa frequenza ma stasati tra loro di 45°. Sei fasi vengono utilizzate per incrementare 6 diversi contatori (da O0 ad O5), che possono essere programmati indipendentemente per dividere la frequenza in uscita, ottenendo così molte combinazioni di frequenze e fasi sincrone tra loro. È presente un ulteriore contatore M che serve per dividere la frequenza utilizzata come feedback, e quindi per moltiplicare quella del VCO. La frequenza del VCO e delle uscite può essere calcolata con le seguenti espressioni:

FVCO = FCLKIN x M / D

FOUT = FCLKIN x M / DxO

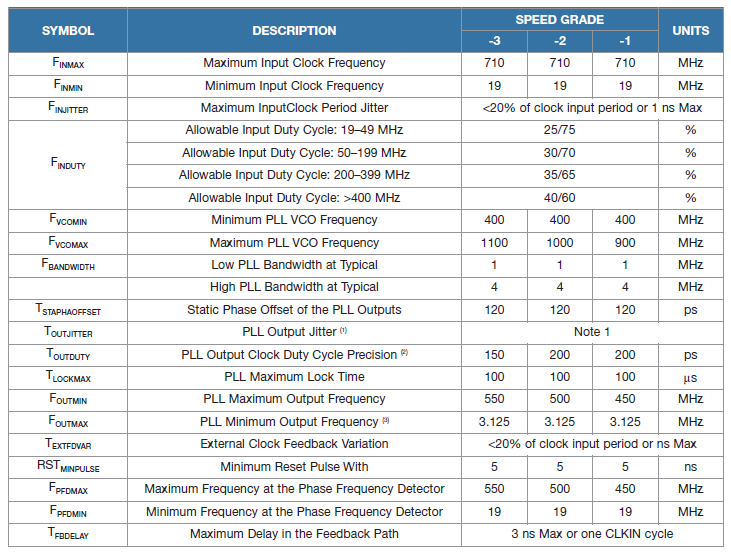

in cui M, D ed O sono i contatori descritti prima, che possono assumere valori compresi tra 1 e 64, 128 e 52 rispettivamente, specificati in fase di progetto tramite gli appositi attributi. Considerando le frequenze massime e minime di lavoro delle varie parti (in particolare del VCO), visibili in Tabella 1, è possibile determinare le combinazioni valide per i parametri ed i segnali d’ingresso al PLL.

ESEMPI DI APPLICAZIONE

Per mostrare le diverse possibilità di utilizzo del PLL verranno di seguito mostrati alcuni esempi di applicazioni comuni, che possono trarre vantaggio dall’applicazione del componente.

Deskew dei clock

Quando si implementano circuiti di grandi dimensioni oppure occorre interfacciarsi con circuiti esterni utilizzando clock molto veloci è necessario assicurarsi che i ritardi che si verificano nella rete di distribuzione del clock non siano tali da causare problemi (ad esempio violazione dei tempi di setup e hold). In questi casi è possibile impiegare vantaggiosamente il PLL per neutralizzare i ritardi di propagazione. Il funzionamento ed il modo d’impiego è simile a quello usato per i DLL: si fornisce il clock al circuito “distante” utilizzando un’uscita del PLL (tipicamente O0) connessa ad un buffer BUFG. L’uscita del buffer deve essere utilizzata come feedback. Il PLL provvederà ad anticipare i fronti in modo da compensare il ritardo, e quindi allineare l’uscita con il riferimento locale.

Correzione del jitter

Il PLL può essere utilizzato per ridurre il jitter presente nel segnale di clock usato come riferimento. Questo è possibile dal momento che il PLL può generare internamente un clock più stabile, che viene sincronizzato al riferimento. In questo tipo di applicazione quindi il PLL viene usato praticamente come “buffer”, restituendo una frequenza uguale a quella presente in ingresso. Per ottenere la riduzione del jitter è necessario selezionare il percorso di feedback interno ed impostare l’attributo BANDWIDTH a Low. Questo agisce sul filtro d’anello del PLL, limitando le variazione in frequenza e quindi il jitter.

Sintesi di frequenza

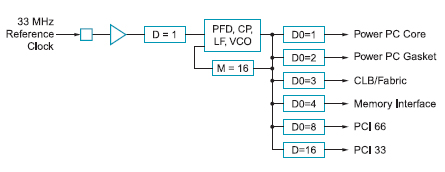

Se, come nella modalità precedente, viene utilizzato il segnale di retroazione interno del PLL, è possibile impiegare il componente per sintetizzare frequenze in un intervallo piuttosto ampio. Grazie ai contatori presenti su ciascuna delle uscite è possibile generare contemporaneamente fino a 6 frequenze diverse, sincronizzate tra loro con precise relazioni di fase e frequenza, impiegando un solo componente. La Figura 4 mostra un esempio di questo tipo di funzionamento, applicato alla generazione dei clock per un sistema complesso costituito da un core PowerPC, la sua logica di interfacciamento, la memoria, ed il bus PCI.

Utilizzando un clock di ingresso con una frequenza di 33.33MHz (proveniente dall’esterno o da un altro PLL/DCM), con un fattore di divisione D pari a 1, si è ottenuta una frequenza di 533MHz dal VCO grazie ad un valore pari a 16 per il contatore M (16x33.33MHz=533MHz). Questa frequenza è prelevata direttamente dall’uscita O0, che ha un divisore pari a 1, e può essere utilizzata come clock per il PowerPC. L’uscita O1, ha un divisore pari a 2 (266MHz), ed è impiegata per generare il clock per la logica d’interfacciamento (il “gasket”). Le altre uscite, le cui frequenze sono rispettivamente 178MHz, 133MHz, 66MHz e 33MHz, sono utilizzate per alimentare la logica implementata sull’FPGA, la memoria SDRAM esterna ed il bus PCI.

Collegamento tra PLL e DCM

I DCM sono i componenti più adatti quando occorre generare sfasamenti precisi tra segnali di clock. D’altro canto i PLL permettono di ridurre il jitter del segnale d’ingresso o di sintetizzare frequenze in modo più flessibile rispetto ai DCM. Per questo motivo i due dispositivi sono stati accoppiati nei blocchi CMT, in modo da potere essere utilizzati congiuntamente. Le principali modalità di utilizzo sono due, e sono mostrate nella Figura 5: in un caso il PLL viene usato per alimentare il DCM, nell’altro il DCM è posto a monte, e alimenta il PLL.

La prima configurazione è utilizzabile per pulire un segnale di clock proveniente dall’esterno ed eventualmente per moltiplicarlo in frequenza (si noti la reazione locale). In questo modo il DCM potrà eseguire la correzione dei ritardi e gli sfasamenti richiesti, operando su un segnale stabile e pulito. È possibile anche prelevare più uscite dal PLL, ed alimentare separatamente più DCM. Tutte le uscite dei DCM saranno caratterizzate dal basso jtter ottenuto grazie al PLL. La seconda configurazione invece permette al PLL di operare su un segnale che è stato preventivamente agganciato in fase in modo da correggere lo skew relativo ad una parte del circuito. La retroazione del DCM infatti è esterna. In questo caso il PLL è utilizzato per pulire e moltiplicare/dividere la frequenza del segnale così ottenuto.

Il blocco funzionale Clock Management Tile (CMT) presente sulle FPGA Virtex-5 di Xilinx offre una gestione molto flessibile e performante dei segnali di clock. E’ infatti in grado di compensare i ritardi sulla distribuzione del clock, eseguire la moltiplicazione/divisione del segnale di clock, ed eseguire un filtraggio sul jittering del clock.

Ottimo articolo, un po’ avanzato per me che sono ing.inf. e sto cominciando a dare un’occhiata ai vostri articoli sul VHDL https://it.emcelettronica.com/?s=VHDL

Sarebbe interessante anche fare un confronto tra le soluzioni PLL dei vari costruttori di FPGA/PLD.

Grazie Davide per aver ricordato alla commuity il corso VHDL appena uscito 😉 https://it.emcelettronica.com/vhdl-for-beginners-entita-e-architetture … OK per la proposta 🙂

L’articolo è interessante seppur molto specialistico. L’architettura della gestione dei clock DCM coadiuvata dalla tecnica PLL dei dispositivi Xilinx è molto complessa. Sarebbe interessante analizzare una appljcazione pratica per valutarne le peculiarità.

È chiaro che articoli come questo, sono rivolti ad esperti di livello, È molto interessante e complesso nei contenuti tuttavia ciò che forse ne aumenta la difficoltà nel seguirlo sono l’uso eccessivo di acronimi non esplicitati e il taglio troppo teorico. Concordo con un precedente commento sulla necessita in futuro di unire qualche applicazione pratica (anche elemtare) ad elementi teorici come questo per aumentare la curiosità è la possibilità di maggiore diffusione della cultura tecnica …anche a livello più alto!!

However Well done! 🙂

Massimo Spiezia