La CPU MCS8140 è un processore a 32-bit RISC basato su un core ARM92EJ-S a 170 MHz e la sua prestazione può raggiungere i 1.1 MIPS per MHz. È un classico dispositivo network USB processor orientato alle reti, ma la sua caratteristica che lo rende veramente interessante, da un punto di vista progettuale, è certamente la capacità di fornire soluzioni di tipo IPSec integrate.

Il dispositivo MCS8140 è un componente orientato alle applicazioni di rete. Il componente ha diversi blocchi funzionali: CPU Subsystem, Ethernet Interface, USB Host, PCI Host, Memory Controller, TOE and Security Engine, and General Interface Blocks. Il componente può essere utilizzato per applicazioni di tipo network USB host controller, e permette la connessione fino a quattro porte USB per accedere a collegamenti Ethernet. L’interfaccia PCI Host, a 32-bit con 33 MHz, risponde alle specifiche previste dallo standard PCI 2.2. Il PCI controller può ricoprire il ruolo di master sul bus e, grazie all’arbitro interno, è possibile supportare fino a due dispositivi PCI. Inoltre, fornisce la possibilità di connettere una varietà di dispositivi PCI come il chip 802.11x, controllers Audio, SATA o IDE. La parte Ethernet Controller è costituita da un MAC (Media Access Controller) e un PHY (Physical Layer): la configurazione Ethernet è controllata attraverso l’uso di una serie di pin di boostrap. Inoltre, il componente ha integrato un I2S controller che è in multiplexer con le linee GPIO.

DESCRIZIONE ARCHITETTURALE

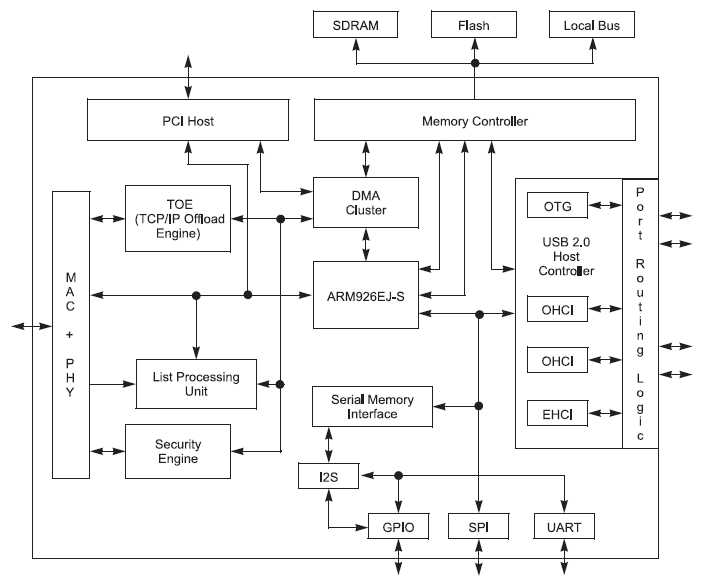

La figura 1 mostra il diagramma dell’architettura interna del componente.

È possibile dividere il diagramma a blocchi in una serie di macrofunzioni:

- CPU Subsystem

- Ethernet Interface

- USB Host

- PCI Host

- Memory Controller

- TOE and Security Engine

- General Interface Blocks.

Le caratteristiche più importanti del dispositivo, a prescindere dalle sue potenzialità in ambito di rete (USB, TOE, Ethernet MAC), è la prerogativa di utilizzare una security engine. Il componente può essere utilizzato in diversi ambiti, questi spaziano da applicazioni WAP (Wireless Access Point) a Secure NAS (Network Attached Storage). Il componente dispone poi di una interfaccia Ethernet con MAC e PHY integrate: cosa che ci permette di costruire applicazioni di rete con relativa facilità. Inoltre, per garantire una certa flessibilità di progetto il componente può essere utilizzato senza il PHY interno. La cosa più interessante comunque è la presenza del cosiddetto Security Engine, in questo modo è possibile gestire le funzioni IPSec utilizzando gli algoritmi DES, 3DES, AES, MD5, SHA-1 e SHA-256. Inoltre, trova anche posto un I2S controller audio che, attraverso le porte messe a disposizione dal blocco GPIO, può essere utilizzato per controllare un esterno I2S codec. Esiste anche la possibilità di caricare differenti tabelle di configurazione mediante un’interfaccia SPI e questo consente una flessibilità notevole poiché in questo modo è possibile modificare il set-up del componente.

Memory controller

La funzionalità di memory controller ha il compito di condividere l’accesso ai dispositivi esterni e di gestire l’eventuale protocollo utilizzato per le altre unità interne, quali DMA. La CPU MCS8140 consente l’accesso fino a 32 Mbytes di memorie Ram dinamiche e fino a 8 Mbyte di memoria non volatile, tecnologia flash. Il parallelismo utilizzato per accedere alle flash è di 8 bits, mentre l’accesso alla Ram dinamica è a 16 e 32 bit.

Interfaccia Gpio

Il componente dispone fino a 20 pin GPIO utilizzati per controllare funzionalità del componente stesso e per la connessione verso dispositivi esterni. Ogni pin poi può essere programmato come ingresso o uscita o anche essere utilizzato come sorgente per eventi asincroni (interrupt). Il blocco funzionale GPIO è controllato direttamente dal processore core (ARM) presente nel sistema. Le linee GPIO sono in multiplexer con i blocchi funzionali MII, JTAG e l’interfaccia I2S.

UART

Il componente supporta l’uso di una interfaccia seriale standard (compatibile a livello di registro alla seriale 16550) di tipo asincrona da una velocità di 1200 bps a 115200 bps programmabile dall’utente. Questa seriale garantisce la gestione delle linee transmit (TX), receive (RX), Request to Send (RTS), Clear to Send (CTS), Data Set Ready (DSR), Data Terminal Ready (DTR), Data Carrier Detect (DCD), and Ring Indicator (RI).

Audio

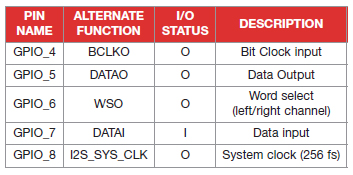

L’interfaccia audio, I2S, è una connessione seriale che permette di trasmettere segnali audio stereo tra il dispositivo e un sistema esterno. Il bus I2S è in multiplexer con le linee di I/O: queste linee vengono configurate in fase di boostrap. I pin di I/O che sono messi in multiplexer sono evidenziati in tabella 1.

Fase di boostrap

Durante la fase di boostrap è possibile definire, mediante opportuni segnali, la configurazione di lavoro del componente. I valori della configurazione sono caricati poi nel registro di boostrap e utilizzabile dal programmatore. I valori dei segnali, da un valore di default, possono assumere significati differenti applicando ai pins degli opportuni valori. Internamente al dispositivo le linee sono posti in pull-downs, infatti basta mettere una resistenza di pull-ups esterna del valore di 4.7 KΩ per cambiarne il significato.

Il security engine (IPSec Unit) e l’ipsec

Il modulo security engine è necessario per poter trasferire i dati, via Ethernet, in modalità cifrata. La IPSec Unit raggruppa alcune funzionalità che sono utilizzati per il trattamento dei dati, queste sono identificate come Operator Block, I/O Block e il canale per il DMA. La parte che gestisce la gestione della crittografia e dell’autenticazione è l’Operator Block. Sono utilizzati gli algoritmi DES, 3DES e AES per la crittografia, mentre MD5, SHA-1 e SHA-256 per l’autenticazione. Il blocco di I/O sovrintende alle operazioni di trasferimento e di ricezione dei dati al modulo IPSec. Il canale DMA è utilizzato unicamente per rendere i trasferimenti più rapidi ed eliminare il carico sulla CPU.

IPSec

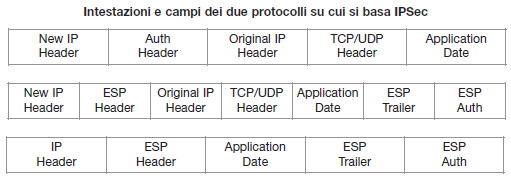

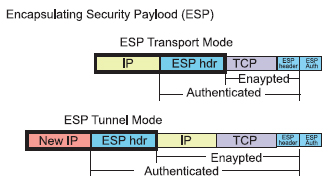

Il transito dei dati su reti TCP/IP utilizzati in ambienti embedded a volte ha esigenze di protezio ne. IPSec certamente risponde a questa esigenza creando una modalità di trasferimento sicura. La figura 2 motra i possibili protocolli nella configurazione IPSec.

L’IPSec è basato sul diversi RFC, tra cui il 2402, ed è costituito da due protocolli. In questo contesto si parla di AH o ESP, ma quali sono i suoi significati? Quali sono le loro differenze?

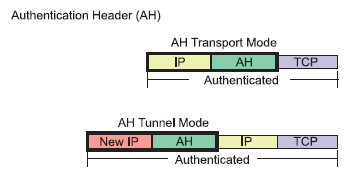

Uno dei protocolli è identificato come l’IP Authentication Header (AH). La base dell’AH è l’autenticazione, l’impossibilità della risposta e l’integrità dei dati senza la cifratura dei dati stessi. Il punto forte del componente è quello di assicurare l’integrità dei dati attraverso un metodo. Per integrità si intende l’incapacità da parte di un terzo di modificare i pacchetti in transito perché vengono contrassegnati da una firma digitale. La firma viene assicurata dal componente mediante l’uso degli algoritmi MD5 o SHA-1 (Secure Hash Algorithm 1): grazie a questa chiave utilizzata da entrambi i sistemi di comunicazione si garantisce la sicurezza del trasferimento. La firma così ottenuta si chiama anche MIC (Message Integrity Code). In un approccio di questo tipo quello che viene cifrato è la parte header e non i dati. Nella struttura dell’intestazione di AH dallo standard si desume che è in realtà composto da sei campi. Il primo blocco (8 bits) mette in evidenza il tipo dell’intestazione successiva, se vengono messi i valori di 6 o 17, allora si vuole definire le intestazioni relativi ai protocolli TCP o UDP. Proseguendo nella descrizione, se il campo dell’intestazione successiva contiene il valore 50, allora siamo alla presenza di una codifica ESP sul pacchetto. La descrizione dell’intestazione AH prosegue fino al sesto campo, questo contiene l’integrity check value (ICV): in questo modo si definisce il checksum per ogni intestazione e i dati contenuti nei pacchetti. La figura 2 mette in evidenza l’IP AH nelle due accezioni: Transport e Tunnel Mode. L’altro protocollo utilizzato con IPSec è IP ESP, vale a dire IP Encapsulating Security Payload (IP ESP), questo, a differenza del precedente, si occupa di crittografare i dati contenuti nei pacchetti oltre ad assicurare l’integrità e l’impossibilità di risposta. La figura 3 mostra invece l’IP ESP sempre nelle due accezioni.

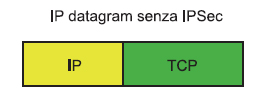

ESP integra nella propria struttura i dati creando un ulteriore livello di protezione, la differenza con AH è che in questo caso non aggiunge solo intestazioni al pacchetto. IPSec offre un alto grado di cifratura e non può essere sottoposto a spoofing sul protocollo IP. In generale la modalità di trasporto è utilizzata per collegamenti sicuri tra comunicazioni definiti come end-to-end, mentre il meccanismo definito come tunnel è utilizzato per connessioni tra due networks. In modalità trasporto IPSec AH protegge il payload e il campo IP header, inserendo un nuovo header tra l’originale IP header e il payload. In tunnel mode l’intero pacchetto IP è incapsulato in un AH e un nuovo IP header. Differente è la gestione con ESP: in questo caso, in modalità tunnel e in trasporto, è cifrato il campo dati e l’IP. Quando non è applicato il protocollo IPSec la trama di rete è mostrata nella figura 6, da questo si nota subito l’enorme semplicità della connessione. Purtroppo quando invece parliamo di connessioni sicure non è possibile proporre la stessa configurazione perché la sicurezza sicuramente aumenta overhead dei processi di comunicazione.

Ethernet MAC

L’interfaccia Ethernet del componente coinvolge i blocchi DMA, TLI, MAC e PHY. IL ruolo del DMA è quello di liberare la CPU del carico del trasferimento dei dati. Il TLI si preoccupa di fornire un bridge tra il DMA e il 10/100 Ethernet MAC. La politica utilizzata per la ricezione e trasmissione del TLI è di tipo FIFO. L’interfaccia Ethernet MAC è conforme allo standard 802.3 e fornisce una interfaccia tra l’host subsystem il MII (Media Indipendent Interface). La connessione Ethernet può lavorare a 10Mbps/100Mbps in full duplex e in half duplex, il clock per il suo funzionamento è fornito dall’interfaccia MII. Le principali caratteristiche del blocco funzionale MAC che il componente gestisce e considera sono:

- Trasmissione e ricezione di messaggi secondo la trama prevista.

- È prevista, come da standard, l’aderenza al cosiddetto Framing. In questo contesto rientrano le definizioni della sincronizzazione, della trama e la gestione del boundary

- Error detection. In questo contesto il componente prevede la gestione degli errori sul frame.

- Media Access Management Il componete si preoccupa di gestire correttamente le collisioni.

- Flow Control during full duplex mode Il componente implementa particolari politiche di controllo, quali per esempio la gestione della trama in riferimento al sincronismo o la sospensione della trasmissione.

Inoltre, il componente MCS8140 si preoccupa di controllare gli errori sulla trama o implementa un meccanismo per il controllo degli indirizzi. Durante l’accensione i 48-bit del MAC address sono caricati in un buffer interno al componente, il MAC address buffer. Inoltre, il componente dispone di un PHY integrato connesso al MAC interno. Il costruttore assicura:

- Affidabilità dei trasferimenti fino a 100 metri;

- L’auto-negoziazione per permettere il trasferimento su linee a 10 o 100 Mbps;

- La scelta tra due diverse connessioni: half e full duplex;

- La possibilità di utilizzare una connessione loopback per facilitare le operazioni di testing;

- Il costruttore garantisce, infine, un rapporto 1:1 dell’Ethernet transformer.

È possibile anche non utilizzare il PHY interno, in questo caso il modulo MII è disponibile direttamente sui pin del GPIO. Il GPIO rende disponibile 16 pins per la funzionalità di MII impedendone l’uso per altri scopi. Questa modalità di funzionamento deve essere decisa in fase di boostrap mediante la tabella di configurazione.

DMA

Il blocco funzionale DMA controller si occupa del trasferimento di un certo numero di bytes tra due zone, chiamate sorgente e destinazione. Per fare questo è necessario inizializzare tre registri: src contiene l’indirizzo dei dati da trasferire, dest, contiene, al contrario, l’indirizzo dei dati di destinazione (dove saranno messi) e Btc contiene la quantità di bytes che dovranno essere trasferiti. Il DMA è utilizzato per qualunque trasferimento sui diversi blocci funzionali. È possibile anche attivare dei trasferimenti sicuri con il DMA, questa funzionalità è supportata mediante un checksum sui dati da trasferire. Inoltre, mediante opportune inizializzazioni è possibile abilitare un interrupt al termine di ciascun trasferimento.

Serial eeprom interface (SPI)

Questa interfaccia permette di connettere una EEPROM seriale attraverso la modalità SPI. L’uso prevalente che se ne può fare è quella di caricare dei dati di configurazione da una memoria esterna. I possibili usi, comunque, dipendono poi dalle singole implementazioni.

Boot rom

All’interno del chip trovano posto, in circa 32 Kbyte, delle particolari routine che permettono di sovrintendere ad una serie di operazioni: da un BIT iniziale alla configurazione interna del componente. Questa memoria è a sola lettura (ROM) e non può essere modificata dall’utente, ma viene fornita direttamente dal costruttore. Attraverso il boot rom è possibile, quindi, caricare differenti configurazioni. In questo modo, l’utente è in grado di avere diverse configurazioni per differenti applicazioni. Il limite della tabella di configurazione è di circa 500 bytes. Esistono poi due modalità di funzionamento del boot loader: quiet (per default) e debug mode. Quando si sceglie il debug mode, sulla porta seriale sono visualizzati dei messaggi in modo da indicare all’utente le azioni intraprese. Le modalità di funzionamento sono in relazione con dei pin dedicati. All’accensione, il componente verifica prima lo stato dei pin di boostrap e, dopo un test preliminare, consente l’inizializzazione della CPU. La documentazione, a corredo della CPU, rende evidente i possibili usi della tabella di configurazione e sulle sue modalità di funzionamento.

CONCLUSIONE

In questo articolo si è cercato di dare una esposizione chiara e sintetica del dispositivo MCS8140. La parte più interessante è certamente la possibilità di avere una interfaccia IPSec per consentire delle comunicazioni sicure tra due sistemi. È senza dubbio un dispositivo che risponde a diverse esigenze: da soluzioni Ethernet basate su USB a quelle applicazioni che possono richiedere connessioni sicure.