Il processore ARM Cortex-A9 si distingue per un livello di prestazioni e di efficienza energetica senza precedenti, proponendosi come la soluzione ideale per tutte le applicazioni in cui sono richieste elevate performance, bassi assorbimenti e bassi valori di dissipazione termica.

La famiglia di processori ARM Cortex offre una vasta gamma di soluzioni adatte a soddisfare anche le richieste più esigenti in termini di funzionalità e di prestazioni. La famiglia ARM Cortex comprende al suo interno tre serie di processori, tutti basati sull’architettura ARMv7 e sull’implementazione del set di istruzioni Thumb-2. La tecnologia Thumb-2 si basa su un innovativo set di istruzioni in grado di realizzare un codice ad elevata densità: essa utilizza, infatti, il 31% di memoria in meno e fornisce il 38% di prestazioni in più rispetto ai set di istruzioni per codici ad alta densità esistenti.

Ne deriva un prodotto in grado di coprire specifiche applicazioni di mercato, con prestazioni elevate e costi competitivi. Le tre serie di processori Cortex sono A, R e M (insieme formano la parola ARM):

- serie ARM Cortex-A: comprende dei processori destinati ad applicazioni con elevato grado di complessità, tipicamente applicazioni multi-utente con sistemi operativi articolati e complessi;

- serie ARM Cortex-R: include processori progettati espressamente per applicazioni di tipo embedded, con requisiti stringenti a livello di prestazioni e comportamento real-time;

- serie ARM Cortex-M: rappresenta di fatto l’entry-level della gamma Cortex, con processori per applicazioni embedded spinte, quindi in prevalenza microcontrollori e Questa serie è anche contraddistinta da costi ridotti al minimo.

ARM CORTEX-A9

Il processore ARM Cortex-A9, appartenente alla fascia alta della serie Cortex, è a sua volta disponibile in due versioni:

- Il processore ARM Cortex-A9, appartenente alla fascia alta della serie Cortex, è a sua volta disponibile in due versioni: processore ARM Cortex-A9 MPCore:si tratta di un processore multi-core in grado di fornire un’elevata scalabilità delle prestazioni e pieno controllo sugli assorbimenti di potenza. Rappresenta la soluzione ideale a basso consumo nel campo delle applicazioni di networking, infotainment (settore automotive), e per le applicazioni nel campo della telefonia mobile;

- processore ARM Cortex-A9: è un processore con architettura tradizionale single-core, particolarmente indicato per applicazioni sensibili ai costi come cellulari, smartphone, tablet ed altri dispositivi embedded portatili.

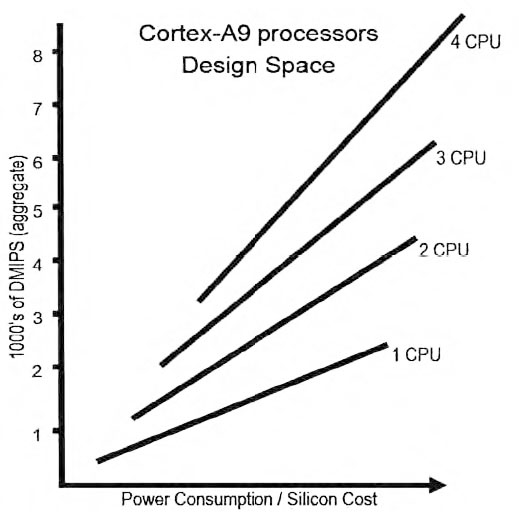

I processori richiesti dalle applicazioni dei nostri giorni non solo devono essere in grado di raggiungere un elevato livello di prestazioni, ma devono anche, e soprattutto, presentare un assorbimento di potenza ridotto al minimo. Il motivo è molto semplice: al giorno d’oggi si assiste ad una domanda sempre più crescente di applicazioni “portatili” quali cellulari, smartphone, laptop, netbook, tablet, PDA, lettori multimediali, consolle per videogiochi, ecc. Il fattore chiave è che tali dispositivi sono alimentati a batteria ed è perciò necessario incrementare l’efficienza di tali dispositivi per allungare il più possibile la durata delle batterie. Una soluzione in grado di soddisfare egregiamente questo requisito è proprio l’architettura multi-core, capace sia di garantire elevati livelli di prestazioni (velocità e capacità di elaborazione real-time), che di mantenere ridotti i consumi. MPCore, la soluzione multi-core del Cortex-A9, è caratterizzata da una scalabilità del livello di prestazioni basata proprio sul numero di core. Si faccia riferimento alla figura 1, nella quale sull’asse orizzontale è riportato l’assorbimento/costo mentre sull’asse verticale il livello di performance ottenuto (misurato in migliaia di DMIPS aggregati). Sono indicati gli andamenti relativi ai casi di 1, 2, 3 o 4 core.

Figura 1: performance vs. numero di core.

Si noti come quest’ultima soluzione, come è lecito attendersi, sia quella in grado di assicurare le migliori prestazioni. Si noti anche come, a parità di DMIPS aggregati, la soluzione che offre il migliore assorbimento/costo sia quella, tra quelle disponibili, che presenta il numero più elevato di core. L’ARM Cortex-A9 single-core fornisce livelli di performance ed efficienza nei consumi senza precedenti, rendendola la soluzione ideale per applicazioni sensibili ai costi. Il processore include un’interfaccia duale a bassa latenza di tipo Harvard a 64 bit per eseguire transazioni indipendenti sui dati e sulle istruzioni ed è in grado di eseguire quattro scritture double-word ogni cinque cicli del processore durante la copia dei dati su una regione di memoria cache.

APPLICAZIONI DEL CORTEX-A9

I processori Cortex-A9 rappresentano la soluzione adatta per una vasta gamma di applicazioni accomunate da requisiti di prestazioni di assoluto rilievo combinate ad un’elevata efficienza nella gestione dell’alimentazione. Entrambe le versioni, single-core e multi-core, sono compatibili tra loro a livello di applicazioni ed è possibile incrementare ulteriormente il livello di performance utilizzando sia il Cortex-A9 NEON Media Processing Engine (MPE), che l’unità di eleborazione in virgola mobile (FPU). Tra i principali tipi di applicazioni ricordiamo:

- dispositivi portatili: smartphone, laptop, netbook, tablet, palmari, ecc... Le prestazioni di questi dispositivi sono comprese tra circa 600 e 3000 DMIPS;

- elettronica di consumo e infotainment: include dispositivi come registratori DVD e Blu-ray, set-top box, decoder televisivi, consolle per i videogiochi. Le performance sono comprese tra circa 800 e 3000 DMIPS;

- dispositivi per il networking: comprende gateway, router, switch, access point, con performace nel range 8008000 DMIPS;

- sistemi embedded: comprende dispositivi come stampanti, videocamere, fotocamere, scanner, con prestazioni comprese tra 800 e 2000

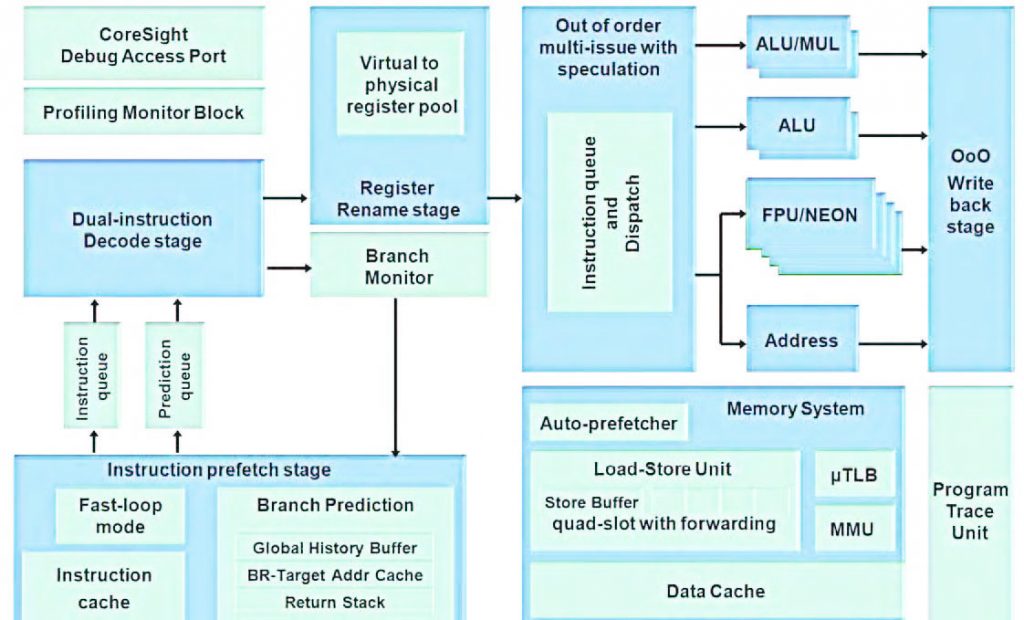

MICROARCHITETTURA DEL CORTEX-A9

Il processore Cortex-A9 è stato progettato con l’obiettivo di massimizzare l’efficienza di elaborazione contenendo nel contempo i costi ed evitando le problematiche connesse ad un valore eccessivo della frequenza di funzionamento. Il risultato è un processore che, grazie alle tecniche di sintesi adottate, può spingersi sino ad una frequenza di clock pari a 2 GHz, con assorbimenti contenuti ideali per dispositivi alimentati a batterie. In figura 2 è visualizzata la microarchitettura del processore Cortex-A9, qui in versione single-core, le cui caratteristiche principali a livello di pipeline sono le seguenti:

- processing avanzato a livello di fetch delle istruzioni e predizione dei branch;

- fino a 4 linee di prefetch dalla cache istruzioni, in grado di ridurre drasticamente i tempi di latenza durante l’esecuzione delle istruzioni;

- circuito di decodifica delle istruzioni alimentato continuativamente, ad ogni ciclo, con un numero di istruzioni compreso tra 2 e 4;

- modalità fast-loop in grado di fornire consumi ridotti durante l’esecuzione di piccoli loop;

- decoder superscalare in grado di decodificare due istruzioni complete per ciclo;

- ridenominazione dinamica dei registri fisici in un pool di registri virtuali;

- utilizzo esteso delle pipeline, che riduce la dipendenza dai dati delle istruzioni adiacenti e la latenza nella risposta agli interrupt;

- le istruzioni possono essere prelevate ed eseguite da ciascuna delle 4 pipeline in ordine qualsiasi (tecnica “out of order”), aumentando il grado di indipendenza dallo stile di scrittura del codice e dal particolare compilatore;

- esecuzione concorrente tra 2 pipeline aritmetiche (load-store e compute engine);

- supporto per quattro linee di richieste verso la cache dati.

Figura 2: microarchitettura del Cortex-A9.

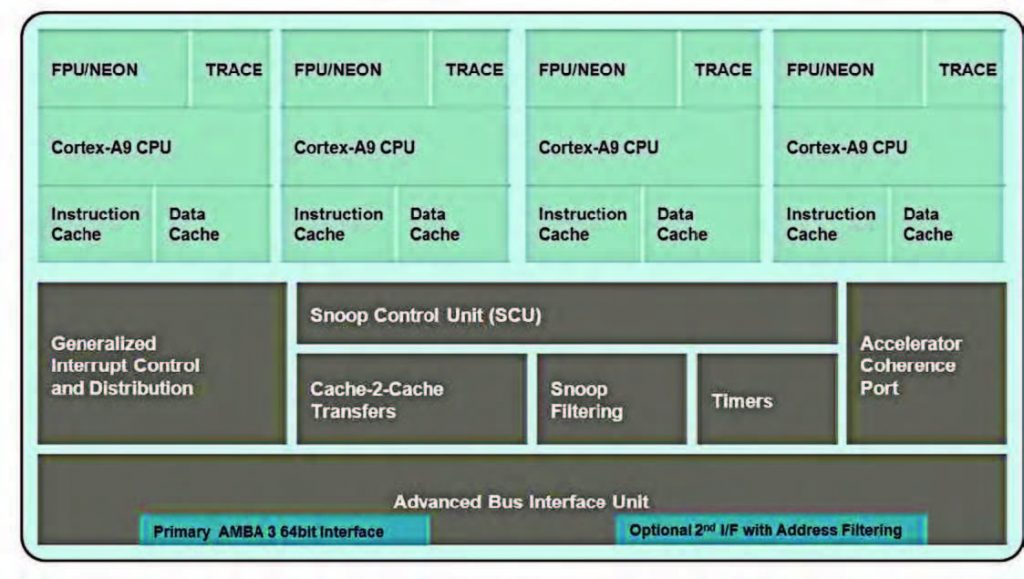

LA TECNOLOGIA MPCore

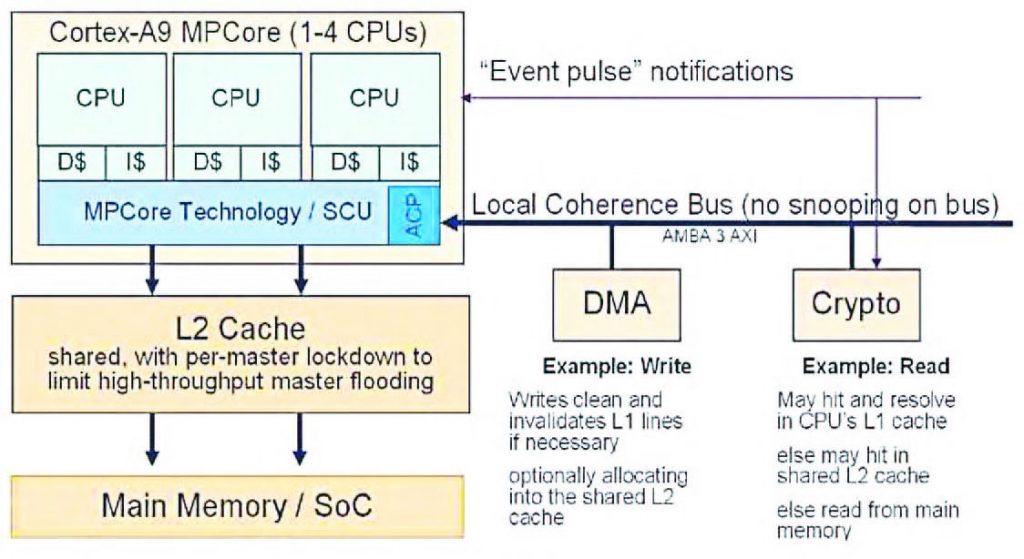

Il processore multi-core MPCore è configurabile con un numero di CPU da 1 a 4 ed è dotato di cache integrata di tipo coerente. Ciascun processore può essere configurato in modo indipendente dagli altri, stabilendo la dimensione della memoria cache e quale interfaccia tra FPU, MPE o PTM utilizzare. Inoltre, in ogni configurazione selezionata, il processore può mettere a disposizione la Accelerator Coherence Port (ACP), consentendo ad altri sistemi non dotati di cache (come controllori DMA od acceleratori crittografici) di essere coerenti con la cache L1 del processore. E’ presente anche un’unità integrata (GIC) per la gestione degli interrupt e la comunicazione, dotata di periferiche private per aumentare le prestazioni ed ottenere una buona portabilità del software; questo sistema è in grado di gestire fino a 224 sorgenti di interrupt indipendenti. Il processore supporta, inoltre, un’interfaccia di collegamento a 64 bit di tipo AMBA 3 AXI, sia singola che doppia.

SNOOP CONTROL UNIT

E’ posta al centro di figura 3 proprio perché rappresenta l’intelligenza centrale della tecnologia multicore ARM ed è responsabile della gestione di interconnessione, arbitraggio, comunicazione, trasferimenti tra cache e cache e verso la memoria di sistema, coerenza della cache ed altre funzionalità ancora. Per la prima volta in assoluto, il processore MPCore esporta queste funzionalità verso altri sistemi e periferiche in modo da incrementare le performance e ridurre gli assorbimenti. Questa coerenza a livello di sistema riduce anche la complessità del software, che altrimenti dovrebbe occuparsi di questa funzionalità.

Figura 3: processore multi-core Cortex-A9.

ACCELERATOR COHERENCE PORT

Questa interfaccia slave, compatibile AMBA 3 AXI, permette di interfacciarsi con sistemi master di vario tipo e supporta tutte le transazioni standard di lettura e scrittura senza richiedere un controllo di coerenza addizionale allocato sul componente esterno. Ogni transazione in lettura diretta ad un’area di memoria coerente dovrà interagire con la SCU per verificare se l’informazione richiesta sia già presente nelle memoria cache di livello 1 del processore. Se ciò avviene, il valore viene restituito direttamente al richiedente, altrimenti (cache miss) si controlla dapprima la sua disponibilità nella cache di livello 2 e, in caso di ulteriore miss, si accede alla memoria principale. Per ogni transazione in scrittura diretta ad una qualunque area di memoria coerente, la SCU forza la coerenza prima di eseguire la scrittura sulla memoria di sistema. La transazione, opzionalmente, può allocare l’informazione anche nella cache L2 (vedi figura 4).

Figura 4: Accelerator Coherence Port.

GENERIC INTERRUPT CONTROLLER

Il blocco GIC costituisce un approccio completo e flessibile alle tecniche di inter-process communication (IPC), con una gestione degli interrupt basata sulle priorità. Vengono supportati fino a 224 interrupt indipendenti, tutti controllati dal software. Ciascun interrupt può essere distribuito tra le varie CPU disponibili, con priorità stabilita a livello hardware, ed è supportata la virtualizzazione degli interrupt attraverso la tecnologia ARM Trustzone. Quest’ultima garantisce un’implementazione affidabile delle applicazioni nel campo della sicurezza, come la gestione digitale dei diritti (DRM), i sistemi di pagamento elettronici ed i servizi basati sul web. Attraverso questa tecnologia è possibile rendere sicure anche le periferiche, come tastiera, schermo e lo stesso processore, per evitare che un software doloso possa acquisire dati personali, chiavi di sicurezza o applicazioni in esecuzione in un dominio sicuro.

ADVANCED BUS INTERFACE UNIT

Il processore Cortex-A9 MPCore supporta la configurazione con una oppure due interfacce master a 64 bit di tipo AMBA 3 AXI, ed è in grado di gestire un traffico di transazioni sul bus di interconnessione anche superiore a 12 Gb/s. Alternativamente, la seconda interfaccia può essere impiegata per implementare un filtro sulle transazioni basato su un sottoinsieme dello spazio di indirizzamento globale, in modo tale da partizionare lo spazio d’indirizzamento direttamente, a livello di processore. Ciascuna interfaccia può anche presentare differenti rapporti di frequenza CPU/bus.

CORTEX-A9 FLOATING-POINT UNIT (FPU)

E’ un’unità addizionale che espande l’architettura base del Cortex-A9 (sia nella versione single-core che multi-core). La FPU dispone di istruzioni in virgola mobile in singola e doppia precisione compatibili con l’architettura ARM VFPv3 ed è compatibile a livello software con le precedenti versioni di coprocessori matematici ARM. Supporta pienamente lo standard IEEE-754 ed opera per la prima volta alla stessa velocità delle precedenti modalità “run-fast” (con prestazioni almeno doppie rispetto ai precedenti modelli), non utilizza eccezioni trap, snellendo pertanto la gestione del software. Sono state, inoltre, aggiunte istruzioni per la conversione di tipi di dati in virgola mobile a 16 bit aumentando il grado di interazione con i processori 3D come il processore grafico ARM Mali, ed estendendo il campo di applicazione agli acceleratori grafici ed alle applicazioni di tipo scientifico.

NEON Media Processing Engine

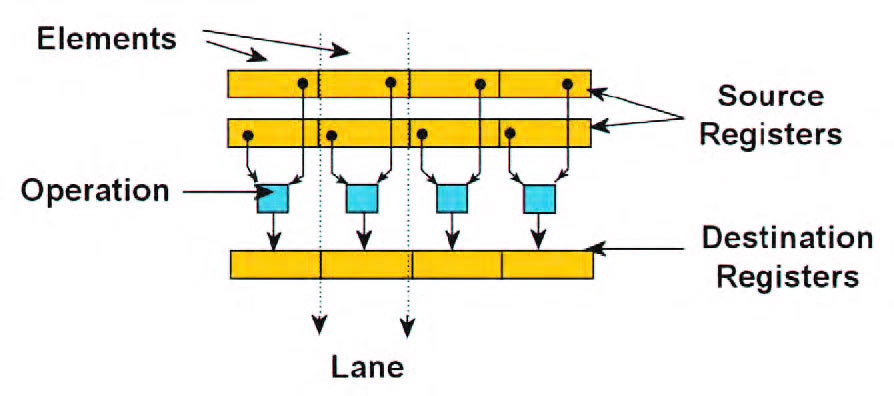

L’MPE è anch’esso disponibile per entrambe le versioni di A9 e rapppresenta in pratica un motore che offre le stesse funzionalità e prestazioni dell’FPU, alle quali si aggiunge un’implementazione avanzata SIMD del set di istruzioni ARM NEON, capace di processare gli attuali e futuri formati multimediali. La tecnologia NEON è nata con lo scopo di accelerare gli algoritmi per applicazioni multimediali, eleborazione del segnale, trattamento delle immagini, codifica/decodifica video, grafica 2D/3D, videogiochi, eleborazione dei segnali audio, telefonia. La tecnologia NEON è un’architettura SIMD a 128 bit (Single Instruction, Multiple Data) dotata di 32 registri da 64 bit (che possono anche essere visti come 16 registri da 128 bit). Come indicato in figura 5, le istruzioni NEON si basano sul seguente processing:

- i registri sono considerati come vettori di elementi dello stesso tipo di dati;

- i tipi di dati possono essere interi con o senza segno a 8, 16, 32 o 64 bit, oppure numeri in virgola mobile a singola precisione (32 bit);

- le istruzioni eseguono le stesse operazioni su tutti i percorsi (lane).

Figura 5: ARM NEON

CONTROLLORE DI CACHE L2

Il controllore della cache di secondo livello PrimeCell PL310 supporta transazioni multiple su ogni interfaccia AXI e rappresenta, di fatto, un buffer tra gli acceleratori (connessi alla Accelerator Coherence Port) ed il processore. E’ in grado di operare alla stessa frequenza del processore, supporta fino ad 8Mb di cache L2 associativa 16-way, e si può integrare con memorie con controllo di tipo ECC o parità. Sono, inoltre, presenti tecniche di lockdown avanzate per bloccare il contenuto della cache, che può pertanto essere utilizzata come una RAM di scambio tra gli acceleratori coerenti ed il processore.

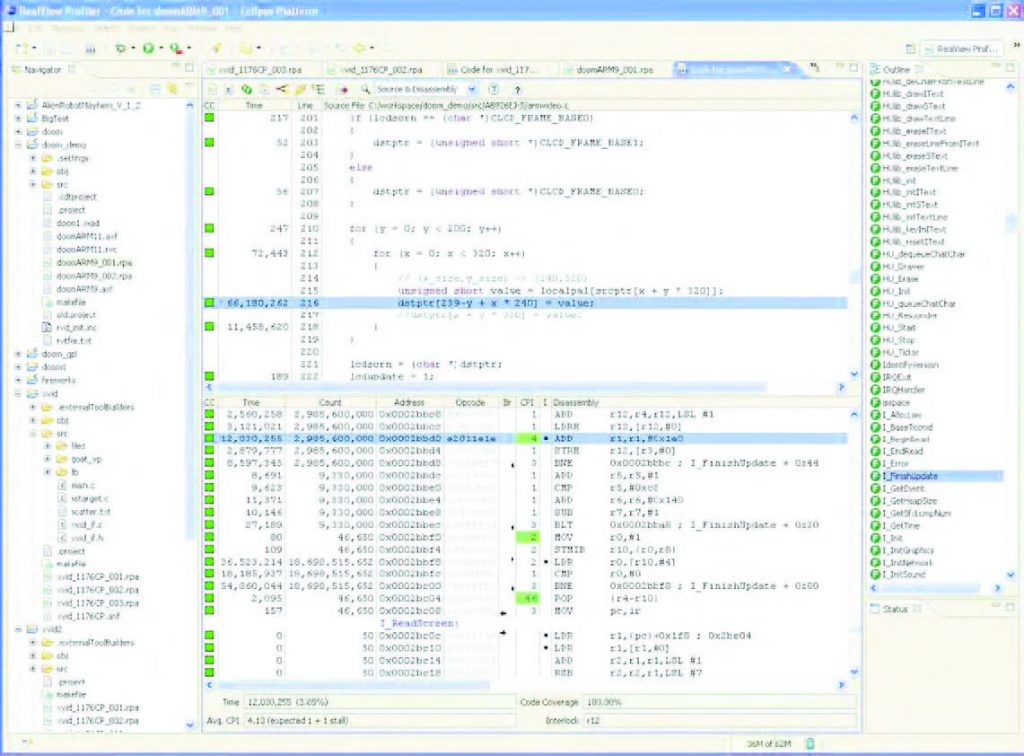

PROGRAM TRACE MACROCELL (PTM)

Insieme alla tecnologia CoreSight, il PTM fornisce uno strumento di debugging che permette allo sviluppatore software di disporre di un trace non intrusivo relativo al codice in esecuzione su ognuno dei processori. Il trace può poi essere memorizzato in un’area posta direttamente sul chip (on-chip buffer) oppure trasferito all’esterno tramite un’interfaccia standard di trace. E’ fornita la piena visibilità su tutti i branch del codice e sulle variazioni del flusso di esecuzione del programma, con analisi dei profili e conteggio dei cicli di esecuzione.

STRUMENTI DI SVILUPPO

Tutti i processori ARM sono supportati dal pacchetto di strumenti di sviluppo RealView, ma anche da un’ampia scelta di tool prodotti da terze parti e sono anche disponibili diversi tipi di sistemi operativi. La catena di sviluppo ARM RVDS 4.1 rappresenta una soluzione completa end-to-end per lo sviluppo software, con supporto pieno per la tecnologia di debug CoreSight. La versione standard di RVDS 4.1 offre le seguenti funzionalità:

- compilatore ARM ad elevata ottimizzazione;

- ARM Workbench IDE;

- ARM RVD Debugger con supporto JTAG e La versione Professional aggiunge altre funzionalità tra cui:

- supporto per i processori Cortex-A9, -A5, ed –M4;

- compilatore con supporto per i set di istruzioni Thumb, Thumb-2 e NEON SIMD;

- trace e profiling real-time non intrusivi con acquisizione continua, anche per diversi

In figura 6 è mostrato l’ARM RealView profiler per Cortex-A9, uno strumento in grado di eseguire l’analisi di performance non-intrusiva per periodi di tempo virtualmente illimitati con il codice in esecuzione a frequenze di clock fino a 400 MHz.

Figura 6: ARM RVDS.