MSP430 rappresenta una famiglia di microcontrollori prodotti dalla Texas Instruments e basati su un’architettura a 16 bit. I vantaggi principali sono il consumo estremamente ridotto (ultra low-power) e il design innovativo.

La famiglia dei dispositivi MSP430 rappresenta la serie mixed-signal dei processori a 16 bit di Texas Instrument (TI). Essi sono la soluzione ideale per applicazioni di misura caratterizzate da alimentazione a batteria e quindi bassissimo consumo. La leadership sia nella tecnologia mixed-signal che in quella digitale ha permesso a TI di creare i chip MSP430 che consento al progettista di interfacciarsi, anche simultaneamente, con segnali analogici, sensori di vario tipo e componenti digitali, il tutto con un consumo ridotto. Applicazioni tipiche includono misurazione, strumentazione portatile, sensori intelligenti ed elettronica di consumo.

Architettura

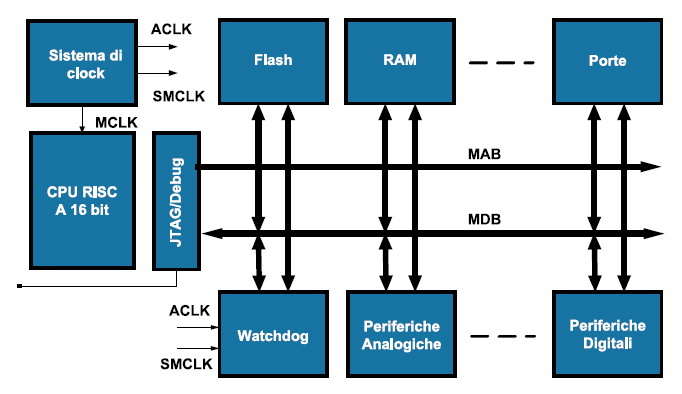

La CPU a 16 bit, le periferiche analogiche e digitali, il sistema di clock flessibile sono combinati secondo un’architettura di tipo von Neumann, basata su un bus per l’indirizzamento della memoria (MBR) ed un bus per i dati (MAB). La Figura 1 schematizza l’architettura interna. TI offre differenti modelli di MSP430, distinti sulla base del supporto di LCD (x4xx e x3xx) e non (x1xx e x2xx):

- MSP430x1xx. Si tratta di dispositivi Flash/ROM – based con una tensione di alimentazione compresa tra 1.8V e 3.6V. È prevista una memoria programma fino a 60kB e 8MIPS con il clock di default.

- MSP430x2xx. Questa famiglia ultra low-power incrementa le sue prestazioni grazie all’uso di un clock da 16MHz, di ulteriori periferiche analogiche o digitali e di una tensione di programmazione della flash ridotta a 2.2V. Con il termine ultra low-power si intendono dispositivi il cui consumo di potenza è ridotto al minimo; in particolare, tale serie presenta i seguenti consumi:

- 0.1mA per la data-retention dei dati in RAM;

- 0.8mA per il real-time clock;

- 250mA/MIPS in modalità attiva.

- MSP430x3xx. È un vecchio modello di dispositivi ROM/OTP con tensione compresa tra 2.5V e 5.5V, 32kB di memoria programma e 4MIPS di operazioni.

- MSP430x4xx. È alimentata con una tensione compresa tra 1.8V e 3.6V. La memoria programma è estesa fino a 120kB di tipo Flash/ROM. È particolarmente indicato per applicazioni di misura ed in ambito medicale grazie al controller integrato per display LCD (figura 1).

Figura 1. L’architettura dei chip MSP430 è di tipo von Neumann

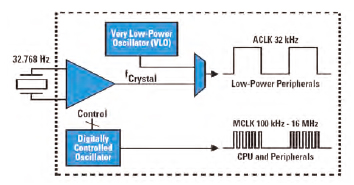

L’architettura del clock è specificatamente progettata per applicazioni battery-powered. Infatti, sono previsti più sorgenti di clock in base alla periferica che lo utilizza. Con il termine ACLK si indica un clock a bassa frequenza pilotato direttamente da un quarzo a 32KHz oppure da un VLO (Very Low power Oscillator) interno. Tale segnale potrebbe essere impiegato per realizzare un RTC con funzione di wake-up. Con il termine SMCLK si indica, invece, un DCO (Digitally Controlled Oscillator) integrato nel chip, il quale ha il compito di fornire un clock ad elevata frequenza per la CPU ed altre periferiche ad alta velocità. Lo schema di principio del sistema di clock presente in MSP430 è rappresentato in Figura 2.

Figura 2. Il sistema di clock del micro MSP430 è appositamente progettato per soddisfare le stringenti richieste delle applicazioni low-power ed ultra low-power

Per agevolare lo sviluppatore e permettergli di scegliere il micro che più si adatta al suo progetto, TI mette a disposizione una pagina web per effettuare una ricerca parametrica.

L’INTERFACCIA USI

Con la sigla USI si intende un’interfaccia digitale del MSP430 che consente con un unico modulo di realizzare la comunicazione SPI e I2C. USI significa infatti Universal Serial Interface ed è implementata su tutti i modelli della serie MSP430x20xx. Le caratteristiche salienti di tale modulo sono:

- Supporto della modalità SPI a 3 fili.

- Supporto della modalità I2C.

- Lunghezza dati variabile.

- Ordine di trasmissione dei dati selezionabile (MSB o LSB).

- Rilevamento automatico del bit di START e STOP nella modalità I2C.

- Generazione del clock programmabile.

- Polarità e fase del clock selezionabili.

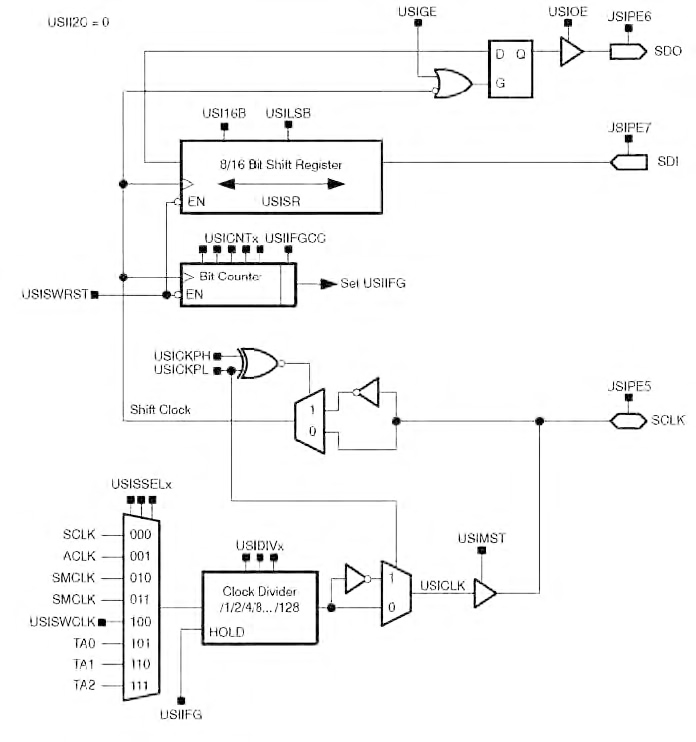

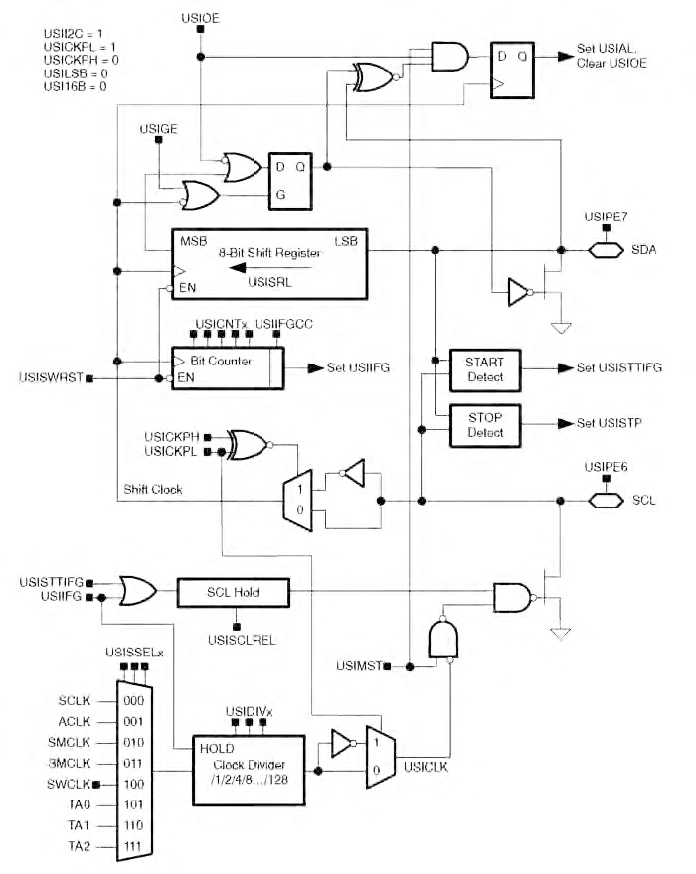

La Figura 3 illustra lo schema a blocchi del modulo USI configurato in modalità SPI (Serial Peripheral Interface), mentre in Figura 4 è riportato lo schema a blocchi della modalità I2C.

Figura 3. Schema a blocchi del modulo USI in modalità SPI

Figura 4. Schema a blocchi del modulo USI in modalità I2C

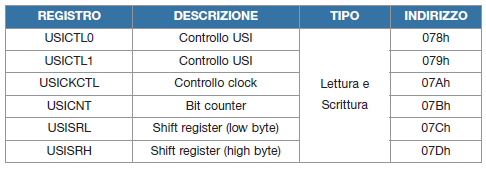

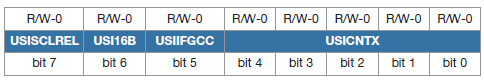

Il modulo USI è realizzato come un registro a scorrimento con un contatore di bit, a cui è stata aggiunta zione SPI e I2C. Il modulo USI è realizzato come un registro a scorrimento con un contatore di bit, a cui è stata aggiunta della logica digitale per il supporto della comunicazione SPI e I2C. Lo shift register (USISR) è direttamente accessibile da software e contiene i dati da trasmettere o ricevuti. Il bit counter rileva il numero di bit campionati e imposta il flag di interrupt (ISIIFG) quando il valore di USICNTx diventa zero. Entrambi i blocchi (contatore e shift register) sono pilotati dallo stesso clock. Sul fronte di salita di tale clock, USICNTx si decrementa e USISR campiona il bit successivo in ingresso. Il latch connesso all’uscita ha lo scopo di ritardare i bit trasmessi e sincronizzarli con il fronte di discesa. Tramite USIGE questo blocco può essere reso trasparente (ad esempio, tale possibilità è usata per generare la condizione di STOP nella I2C). Per attivare le funzionalità della porta USI è necessario settare i bit USIPEx nel relativo registro di controllo (USICTL0). La Tabella 1 riassume tutti i registri interessati nella configurazione e gestione del modulo USI.

Tabella 1. L’interfaccia USI è facilmente controllabile via software tramite i registri di configurazione e controllo

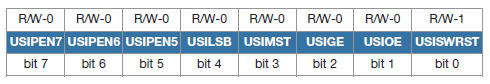

Tabella 2. Registro USICTL0

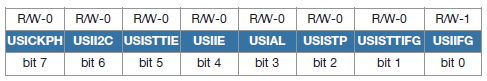

Tabella 3. Registro USICTL01

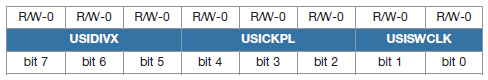

Tabella 4. Registro USICKCTL

Tabella 5. Registro USICNT

Il generatore di clock per il modulo è costituito da un multiplexer per la selezione del clock, un divisore di frequenza e da un selettore della polarità come mostrato negli schemi a blocchi in Figura 3 e Figura 4. Le sorgenti di clock possono essere selezionate tra:

- Clock ACLK o SMCLK (Figura 2).

- Clock esterno.

- Clock generato dall’uscita del timer A.

I bit USISELx selezionano le suddette opzioni. Il blocco successivo al multiplexer consente di effettuare il prescaler del clock selezionato. La selezione delle diverse opzioni è fatta mediante i bit USIDIVx. La generazione del clock è inibita quando il bit USIIFG è impostato ad 1 oppure quando il modulo è configurato come slave (quindi il clock sarà generato dal master).

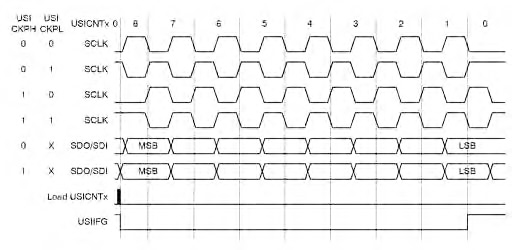

Modalità SPI

Per attivare la modalità SPI bisogna impostare il bit USII2C (nel registro USICTL1) a 0. I bit USICKPL e USICKPH impostano rispettivamente il livello inattivo del clock ed il fronte del clock su cui avviene il campionamento del bit. Inoltre, i bit USIPE5, USIPE6 e USIPE7 servono per abilitare i pin SCLK, SDO e SDI tipici dell’interfaccia SPI. La Figura 5 riporta le diverse temporizzazione dei segnali SPI ottenuti al variare dei bit suddetti.

Figura 5. I bit USICKPL e USICKPH permettono la selezione del livello di tensione del clock quando è inattivo ed il fronte del clock su cui avviene il campionamento dei bit

Per selezionare se il dispositivo deve agire da master o slave è necessario agire sul bit USIMST (‘1’ significa master, mentre ‘0’ slave). Per una gestione più efficiente dei dati trasmessi e ricevuti è possibile utilizzare l’interrupt della SPI. Per la sua abilitazione è necessario impostare a ‘1’ i bit USIIE e GIE. In questo modo, quando USICNTx (il bit counter) sarà zero il flag USIIFG farà scattare l’interrupt. Il bit deve essere azzerato via software.

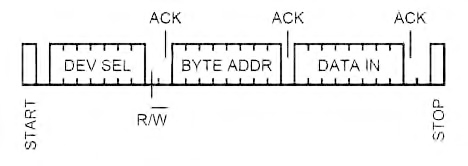

Modalità I2C

Per utilizzare questa modalità bisogna utilizzare la seguente configurazione dei bit:

- USII2C = 1;

- USICKPL = 1;

- USICKPH = 0;

- USILSB = USI16B = 0;

- USIPE6 = USIPE7 = 1.

Anche in questo caso è possibile abilitare la modalità master o slave con lo stesso sistema mediante il bit USIMST. In modalità trasmissione, i dati sono inizialmente inseriti nel registro USISRL. L’uscita è abilitata impostando il bit USIOE e la trasmissione inizia scrivendo 8 in USICNTx. La fine della trasmissione del byte è segnalata dal bit USIIFG = 1 e dal fatto che il clock è arrestato. Per ricevere il bit di acknowledgement (ACK), bisogna impostare USIOE a 0 e caricare in USICNTx il valore 1. In questo modo si sta preparando il modulo a ricevere un solo bit. Quando nuovamente USIIFG sarà divento 1 allora sarà possibile testare il bit ricevuto, eventualmente utilizzando il codice assembler riportato nel Listato 1.

; Ricezione ACK/NACK

1. BIC.B #USIOE,&USICTL0 ; SDA input

2. MOV.B #01h,&USICNT ; USICNTx = 1

3. TEST_USIIFG

4. BIT.B #USIIFG,&USICTL1 ; Test USIIFG

5. JZ TEST_USIIFG

6. BIT.B #01h,&USISRL ; Test received ACK bit

7. JNZ HANDLE_NACK ; gestione NACK

...altrimenti, gestione ACK

| Listato 1 |

La ricezione di un byte è molto simile alla ricezione dell’ACK. L’unica differenza è nello scrivere il valore 8 anziché 1 nel registro USICNTx. Ovviamente, il ricevitore deve essere in grado di trasmettere un ACK oppure un NACK al dispositivo che ha iniziato la trasmissione. Il relativo codice assembler è riportato nel Listato 2.

; Generazione ACK

1. BIS.B #USIOE,&USICTL0 ; SDA output

2. MOV.B #00h,&USISRL ; MSB = 0

3. MOV.B #01h,&USICNT ; USICNTx = 1

4. TEST_USIIFG

5. BIT.B #USIIFG,&USICTL1 ; Test USIIFG

6. JZ TEST_USIIFG

7. ......

; Generazione NACK

1. BIS.B #USIOE,&USICTL0 ; SDA output

2. MOV.B #0FFh,&USISRL ; MSB = 1

3. MOV.B #01h,&USICNT ; USICNTx = 1

4. TEST_USIIFG

5. BIT.B #USIIFG,&USICTL1 ; Test USIIFG

6. JZ TEST_USIIFG

7. ......

| Listato 2 |

Nella comunicazione I2C il dispositivo master avvia la trasmissione dei dati verso lo slave mediante la condizione di START (vedere Figura 6).

Figura 6. Per gestire il protocollo I2C è necessario che il master generi una condizione di START per iniziare la comunicazione ed una condizione di STOP per terminarla

Si tratta, in sostanza, di una transizione alto-basso sul pin SDA, mentre il pin SCL è tenuto nello stato logico ‘1’. La generazione di tale condizione è ottenuta abbastanza semplicemente agendo sul latch di uscita. Le istruzioni utilizzate sono riportate nel Listato 3.

; Generate START 1. MOV.B #000h,&USISRL ; MSB = 0 2. BIS.B #USIGE+USIOE,&USICTL0 ; Latch/SDA output enabled 3. BIC.B #USIGE,&USICTL0 ; Latch disabled 4. ......

| Listato 3 |

In corrispondenza ad una condizione di START deve essere generata una condizione di STOP per chiudere la connessione tra master e slave. Il Listato 4 riporta le istruzioni assembler per gestire anche questa condizione.

; Generate STOP 1. BIS.B #USIOE,&USICTL0 ; SDA=output 2. MOV.B #000H,&USISRL ; MSB = 0 3. MOV.B #001H,&USICNT ; USICNT = 1 per un ciclo di clock 4. TEST_USIIFG 5. BIT.B #USIIFG,&USICTL1 ; Test USIIFG 6. JZ TEST_USIIFG ; 7. MOV.B #0FFH,&USISRL ; USISRL = 1 per portare SDA alto 8. BIS.B #USIGE,&USICTL0 ; Latch disabilitato 9. BIC.B #USIGE+USIOE,&USICTL ; 10. ......

| Listato 4 |