La tecnologia 3D sta generando molto interesse come modo di ridurre i costi NRE (non-recurring engineering, riferito al costo iniziale per la ricerca, lo sviluppo,la progettazione e il test di un nuovo prodotto) e i tempi di immissione nel mercato. La tecnologia 3D è nella sua fase di ascesa, per cui si è alla ricerca di uno standard singolo nella tecnologia thorugh-silicon vias (TVS), che permette di compattare in modo più serrato i componenti dei chip, con il risultato di creare sistemi più economici, piccoli e veloci. Questo viene fatto per ridurre principalmente i costi di infrastruttura. Ma sarà davvero questo il caso?

Tecnologia 3D: due differenti applicazioni

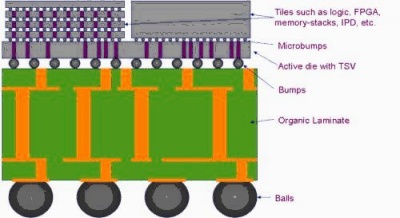

Esistono almeno due applicazioni fondamentalmente differenti per la tecnologia 3D che sono guidate da motivazioni nettamente diverse. Lo spazio mobile è condizionato principalmente dal bisogno di ridurre l’energia, l’altezza e l’area. Lo spazio di networking e di infrastruttura dipende invece dal bisogno del miglioramento della produzione e dalla capacità di inserire quanta più memoria possibile in una sola volta, al minor consumo di energia. I dispositivi portatili hanno bisogno di architetture sottili, così come dispositivi per il networking più grandi richiedono strutture 3D-IC più spesse per gestire la piattezza necessaria per un die più grande e per le architetture side-by-side dei dispositivi.

Tecnologia 3D e 2.5D e ASIC

La tecnologia 3D e quella 2.5D (una pseudo 3D, termine che si usa per indicare una tecnologia che usa allo stesso tempo il 2D e il 3D oppure che è 2D e da l’illusione del 3D) possono cambiare l’intero panorama e l’architettura degli ASIC (Application Specific Integrated Circuit). Questo processo si è già verificato per gli FPGA (Field Programmable Gate Array, circuiti integrali digitali programmabili via software) e gli ASSP (Application Specific Standard Product, circuiti integrati che implementano una specifica funzione ideale per un ampio mercato), ma per gli ASIC si deve affrontare un problema particolarmente ostico; Il costo, crescente in maniera esponenziale, dei tape-out a nodi più bassi ha avuto come risultato un numero inferiore di tape-out. Inoltre, esistono meno esperti in questo specifico campo e alcune compagnie sarebbero in grado di spendere molti soldi per sviluppare la tecnologia (3D) e poi diffondere l’expertise nel campo. Le fonderie e le case di assemblaggio si tengono strette le loro schede 3D-IC in attesa che la leadership del settore passi agli utenti della tecnologia 3D e 2.5D. Ovviamente, non hanno intenzione di spendere soldi per accorgersi successivamente di dover cambiare corso per seguire la corrente prevalente. eSilicon ha già investito un gran quantitativo di denaro e di tempo sulla tecnologia 3D e 2.5D-IC. Gli ASIC necessitano di alcuni tasselli base collaudati, come le memorie, microprocessori, dispositivi passivi integrati, die FPGA e altri. Implementare una tecnologia 2.5D e 3D-IC può includere la presenza di tecnologie a 28nm, con un NRE più basso grazie ad un interposer da 65nm. Avere quindi i suddetti tasselli permette ad un team di progettazione di avere dei punti fissi da cui partire e di risparmiare quindi molto tempo, oltre a ridurre i rischi. Il futuro degli ASIC nel 3D è quindi ancora incerto e la direzione da prendere dipenderà dal corso della cosiddetta corrente principale.