Nel prossimo articoli mostreremo come la necessità di realizzare un sistema di acquisizione ed elaborazione digitale il più compatto possibile, ha portato alla scelta di integrare su un’unica scheda stampata (PCB) sia il sensore che il convertitore A/D. In questo modo si renderà più semplice e versatile l’utilizzo del sistema complessivo, facilitando eventuali operazioni future di conversione analogica (tramite un opportuno DAC) e consentendo l’aggiunta di ulteriori sensori ELIS-1024, per aumentare il più possibile il numero di fibre ottiche da controllare senza occupare troppo spazio. In particolare in questo articolo ci concentreremo sulla scelta del dispositivo A/D motivandola opportunamente.

Caratteristiche richieste al convertitore A/D:

Prima di inoltrarsi nel vasto mercato dei convertitori A/D, è necessario imporre dei vincoli restrittivi che permetteranno una scelta adeguata del convertitore. Tali vincoli sono dettati dalle prestazioni richieste dal sistema, nonché dalle caratteristiche del sensore ELIS-1024 scelto di cui è stato trattato negli articoli precedenti (vedi link a fine articolo).

Tenendo in conto di ciò, si possono evidenziare i seguenti fattori cruciali per la scelta del convertitore A/D:

1. Frequenza di campionamento almeno pari a 1 kHz;

2. Elevata risoluzione.

3. Tensione analogica di ingresso fino a 5V.

4. Semplicità nella gestione dei segnali di controllo.

5. Basso tempo di conversione.

Il primo parametro è ricavato dalla massima frequenza di Read Out dei pixel del sensore ELIS-1024. Tale frequenza indica con quale velocità i pixel vengono inviati in uscita dal sensore ed è regolata dal segnale di clock del sensore stesso. Come vedremo il segnale di clock del sensore e quello del convertitore A/D saranno correlati.

Il secondo parametro è dovuto al range dinamico di tensione in uscita dal sensore ottico mentre si richiede un‘ elevata risoluzione , quindi un numero sufficiente di bit, per ottenere una buona sensibilità alle variazioni di tensione fornite dal sensore .

Come quarto parametro troviamo la semplicità nella gestione dei segnali di controllo in quanto si vuole realizzare la logica più semplice possibile sia per il controllo del sensore e dell’adc ,sia per l’elaborazione dei dati acquisiti in ambito digitale.

Infine, troviamo la richiesta di un basso tempo di conversione, in modo da poter effettuare le operazioni di acquisizione ed elaborazione in Real-Time .

Il convertitore A/D scelto : l’ ADS7818.

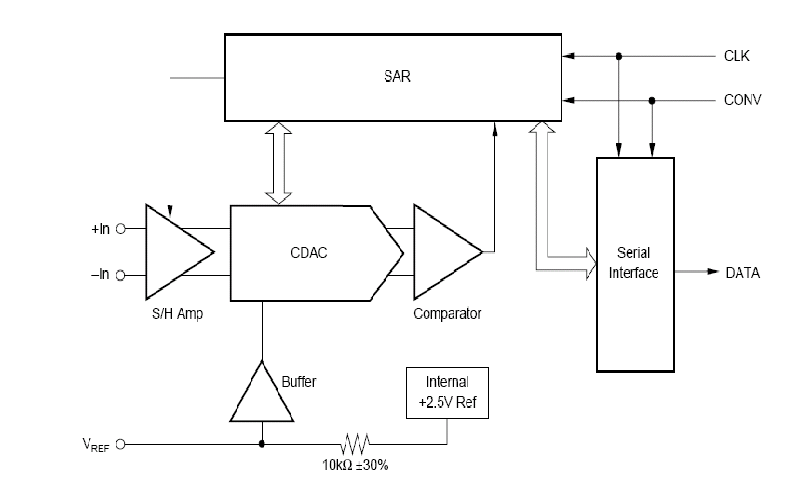

Viste le caratteristiche richieste al sistema di elaborazione elencate nel paragrafo precedente, è stato scelto come convertitore A/D l’ ADS7818 della Burr-Brown® (qui trovate il datasheet ). L’ADS7818 è un convertitore Analogico-Digitale con registro ad approssimazioni successive (SAR) ed una risoluzione di 12 bit , nella figura successiva troviamo la rappresentazione a blocchi del convertitore.

Le principale caratteristiche di questo convertitore sono elencate di seguito:

-Alimentazione singola compresa tra 0V e 5V.

-Tensione di riferimento interna di 2.5 V ma con possibilità di utilizzare una tensione di riferimento estern.

-Interfaccia seriale.

- Socket DIP-8.

- Frequenza di clock minima di 200kHz, massima di 8 MHz.

- Risoluzione a 12 bit.

- LSB pari a 1,22 mV (se si usa il riferimento interno di 2.5V).

- Tempo di conversione minimo pari a 1.625 μs.

- Tempo di acquisizione minimo pari a 350 ns.

- Errore di non linearità integrale tipico di ±1 LSB.

- Errore di non linearità differenziale tipico di ±0.8 LSB.

- SNR di 72 db con ingresso analogico di 5v picco-picco e frequenza di 100 kHz.

La scelta di un convertitore ad approssimazioni successive è giustificata dal fatto che non è richiesta una conversione A/D molto veloce. Infatti, notiamo che la massima frequenza di clock non è molto elevata (8 MHz) così come il tempo di conversione minimo non è molto piccolo(1.625 μs).

Il nostro sistema di acquisizione mira ad avere come fattore privilegiato la precisione della conversione A/D. Per questo è stato scelto un convertitore a 12 bit, che seppure non rappresenti la massima risoluzione disponibile sul mercato (attualmente vi sono in commercio ADC che arrivano fino a 32 bit di risoluzione grazie all’utilizzo di modulatori Σ∆), permette di ottenere il giusto compromesso tra prestazioni e prezzo( 6.60€ per unità nel novembre ’08 ).

Gli errori di non linearità integrale e differenziale sono contenuti in quanto entrambi non superano l’ampiezza del LSB, garantendo una buona linearità nella conversione. Il rapporto segnale/rumore di 72 dB ad una frequenza del segnale in ingresso di 100kHz garantisce buone prestazioni del dispositivo anche a fronte di disturbi ad alte frequenze.

Segnali di controllo:

Dalla figura precedente è stato possibile notare la presenza di soli due segnali di controllo (CLK e CONV ) e un segnale di uscita (DATA) in cui vengono riportati uno per volta i 12 bit (dal più significativo al meno significativo), relativi alla conversione del segnale analogico in ingresso.

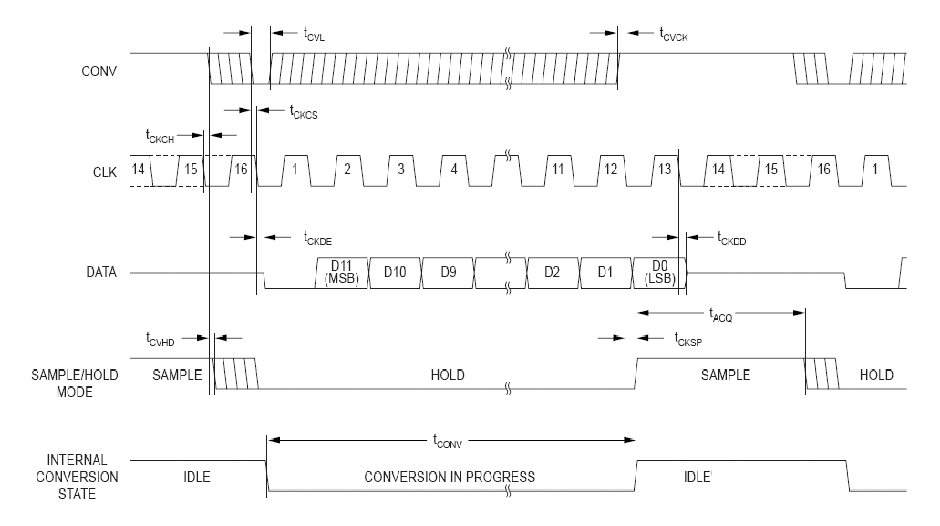

Per poter analizzare nel dettaglio il funzionamento del convertitore in esame, riportiamo nella prossima figura la tempificazione standard per la conversione A/D.

L’intera fase di conversione può essere suddivisa nelle due tipiche sottofasi di SAMPLE e HOLD.

Temporalmente si verifica prima la fase di SAMPLE all’interno della quale il segnale CONV è alto, mentre il segnale in ingresso viene campionato dal circuito di S/H mostrato nello schema precedente.

Quando il segnale CONV si porta al livello logico basso e rimane tale per un tempo non inferiore al tCVL, allora viene avviata la fase di HOLD. In questa seconda fase si effettua la vera e propria conversione del segnale campionato in precedenza, proponendo in uscita i bit in maniera seriale e sincrona con il fronte di discesa del clock.

Come si evince dalla figura analizzata, sono evidenziate la durata della fase di sample con tACQ, la durata della conversione con tCONV ed altri intervalli di tempo di interesse minore.

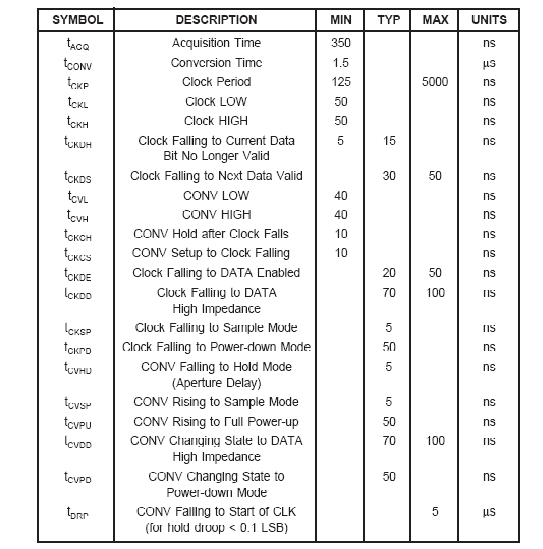

I valori massimi e minimi di questi intervalli sono riportati in tabella:

Schema di montaggio

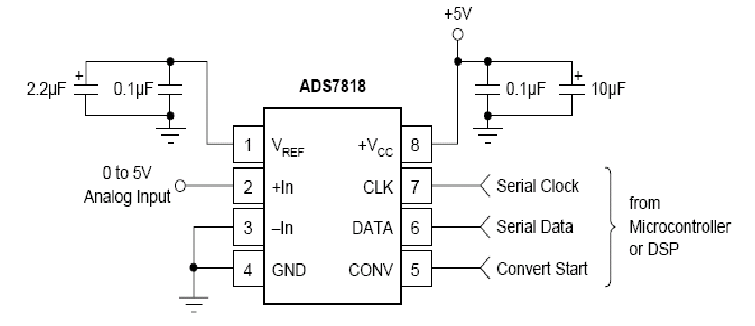

Riportiamo nella prossima figura lo schema di montaggio per l’ ADS7818.

Lo schema mostrato prevede delle capacità connesse tra Vcc e massa e tra VREF e massa, per eliminare gli eventuali disturbi in alta frequenza provenienti dall’alimentazione ed eventuali glitch provenienti dalla logica interna del dispositivo. All’interno del datasheet del convertitore, viene suggerito di l’opportunità di prevedere una posizione delle capacità di filtraggio quanto più vicina possibile al convertitore. Di queste considerazioni se ne terrà in conto nel prossimo articolo, in cui sarà progettato il layout del circuito che comprende lo schema di montaggio dell’ ADS 7818 e dell’ ELIS-1024. Nel nostro caso i segnali di CLK, DATA e CONV saranno utilizzati da un FPGA per realizzare la corretta sincronizzazione tra il sensore ELIS-1024 e il convertitore A/D.

Link correlati all'articolo:

https://it.emcelettronica.com/sensore-di-immagine-elis-1024