Ai giorni nostri con schede complesse risulta necessario testare i circuiti stampati dopo la produzione. Il boundary scan standardizzato secondo JTAG è un buon metodo di testing. L’articolo analizza alcuni importanti concetti che riguardano questa tecnica ed anche le modalità di gestione di situazioni di testing complesse.

Introduzione al testing JTAG

Quando una complessa PCB viene prodotta risulta necessario testarne le funzionalità. In ogni caso è necessario effettuare una sessione di prova del componente prima del test funzionale, in modo da assicurare il funzionamento della maggior parte delle componenti prodotte. All’inizio dell’era dei sistemi digitali ci si preoccupava di questa fase attraverso l’in-circuit testing. Si trattava di testing abbastanza simili a controlli completi delle funzionalità di singoli chip posizionati sulla PCB. Con l’aumentare della complessita’ questo processo diventò praticamente impossibile in termini di tempo richiesto e di costo delle risorse di testing.

I circuiti integrati contenevano la maggior parte della logica per l’implementazione di un sistema e utilizzavano un numero incrementale di transistori. Fu semplice dedurre che, con un così gran numero di transistori inclusi in un chip, una certa quantità di logica di test può essere inserita. Questi controllori dei test possono essere gestiti dall’esterno del chip così da eseguire test all’interno ed inviare all’esterno i risultati. I transistori aggiunti per questa procedura non saranno in ogni caso un peso per lo schema circuitale. Un collegamento in cascata seriale (daisy chain) può quindi collegare queste componenti e, in questo caso, i chip IC (Integrated Circuits) possono essere testati sequenzialmente sul fronte della PCB, in modo da determinare se la scheda sia funzionante. Questo è lo schema principale del testing JTAG.

Gli Standard JTAG

IEEE 1149.1, IEEE 1149.4 ed IEEE 1149.6 sono gli importanti standard applicati nel JTAG. IEEE 1149.1 è la versione originale dello standard creata nel 1990 (anche conosciuto come standard dot1) il quale, da allora, è stato aggiornato due volte. Esso è uno standard realizzato principalmente per trattare circuiti digitali. IEEE 1149.4 (lo standard do4) creato nel 2000 regolamenta il boundary-scan analogico. L’utilizzo dei signal paths LVDS (segnali differenziali a basso voltaggio) per sistemi ad alta velocità nei sistemi digitali è in rapido aumento. Lo standard IEEE 1149.6 regolamenta questo tipo di testing. L’IEEE 1532 imposta uno standard per la programmazione di componenti PLD e FPGA cosicchè esse possano essere programmati per cambi di configurazione attraverso input del JTAG.

L’IEEE 1149.1 definisce la tecnologia di test embedded in migliaia di circuiti integrati (IC), fornendo lo ”scheletro” del test e della programmazione di un gran numero di sistemi. Una TAP (Porta di Accesso Test), una macchina sequenziale, un registro istruzioni e un certo numero di registri dati devono essere implementati in un IC per poterlo testare attraverso il metodo del Boundary Scan. Il Boundary Scan Description Language (BSDL) stabilisce la sintassi che descrive come implementare il controller TAP e anche le operazioni che dovrebbe svolgere. L’IEEE 1149.4 (dot4) introduce funzionalità che permettono di testare segnali analogici. AT1, un circuito di pilotaggio analogico, ed AT2, un pin di misura analogico, sono stati inseriti nello schema. Quest’ultimi sono collegati a dei bus di test analogici interni che permettono di pilotare e, successivamente misurare, le risposte a parti di funzioni analogiche nell’IC. IEEE 1149.6 introduce la possibilità di testare segnali LVDS e segnali capacitativamente accoppiati. È possibile inviare e ricevere dati su paths del segnale per rilevare problemi come pin aperti, pin cortocircuitati a terra, e condensatori aperti dalla risposta degli impulsi dati.

Uno standard relativo a IEEE 1532 si occupa dei metodi base per la programmazione di componenti come PLD e FPGA. Lo standard 1149.1 è stato utilizzato nella produzione di questi componenti e la porta JTAG è stata impiegata per la loro programmazione. Comunque ci sono differenze nel modo in cui i componenti vengono programmati e, per questo, si è reso necessario un processo di standardizzazione. Quando un componente è fedele allo standard, è possibile la configurazione, lettura, cancellazione e verifica dati indipendentemente dal produttore. Una descrizione BSDL dell’algoritmo usato per uniformare un componente allo standard è disponibile nello stardard stesso. BSDL è un sottoinsieme del linguaggio VHDL.

Alcuni standard futuri, ora in fase di sviluppo, sono: l´IEEE 1149.7 spesso conosciuto come JTAG a conteggio di pin ridotti, il P1581, simile a 1532 ma usato per il testing di componenti di memoria e il SJTAG, una estensione per testing a livello sistema.

I concetti del JTAG

JTAG fornisce accesso a cellule digitali interconnesse in un IC e fornisce anche un metodo di accesso per test, la diagnostica e il software debug. JTAG rende disponibile anche modalità per effettuare aggiornamenti in-circuit e aggiornamenti firmware remoti. La Fig. 1 illustra il supporto logico necessario all’interno dell’IC per essere conforme allo standard 1149.1. Le cellule interne sono connesse serialmente in maniera necessaria per lesecuzione del test, come mostato nel diagramma.

Figura 1

TMS, TCK e TRST sono segnali comuni a tutti i componenti inclusi nel ciclo di test. La linea seriale di test è quella collegata alla linea TDI (Test Data In) ed i risultati vengono rilevati dal pin TDO (Test Data Out) in ogni componente. I componenti devono essere collegati secondo metodo daisy-chain collegando la linea TDO del primo circuito alla TDI del cicuito successivo, così da creare una catena seriale. TMS è il segnale della modalità di test mentre TCK è il clock di test che invia un segnale di clock sincronizzando i dati seriali ed i segnali TMS. TRST* è un segnale di reset asincrono. TDI è connesso serialmente ai blocchi interni come mostrato in figura. In caso di necessità il segnale di test può essere bypassato.

Per testare segnali analogici un IC deve contenere all’interno strutture aggiuntive come mostrato in figura 2 (secondo l`IEEE 1149.4). La circuiteria di interfaccia al bus di test deve occuparsi di unire i paths di test analogici e digitali in maniera adatta.

Figura 2

Il circuito di interfaccia al bus dei test gestisce il testing basato sugli input AT1 e restituisce i risultati sulla linea AT2. Queste linee seriali sono poi collegate in cascata con lo stesso metodo usato per le linee TDI e TDO. IEEE 1149.6 fornisce le modalità per le misurazioni dei segnali LVDS e lo standard suggerisce che esse vengano eseguite come mostrato in Fig. 3. Nella figura il BSR è il registro del Boundary Scan.

Figura 3

I progettisti degli IC devono prestare particolare attenzione a questi schemi ed in particolare ai dettagli interni. In ogni caso gli ingegneri di architetture embedded devono comprendere i concetti, poichè saranno loro a dover fornire la struttura dei collegamenti in cascata sulla PCB di sistema per poter svolgere il testing correttamente. È in questa fase che possono sorgere dei problemi e sono loro a doversene curare durante la progettazione dell’ hardware e della PCB.

Complessità dei collegamenti Daisy Chain seriali

Con una scheda di discreta complessità il testing seriale dovrà essere effettuato su varie componenti sulla PCB. Il testing può divenire una prassi che necessita di grandi quantità di tempo, in questi casi anche un testing full-rate può risultare difficoltoso.

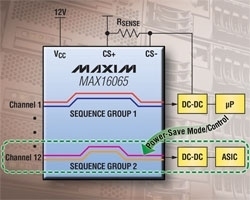

Con svariati diversi tipi di chip sulla scheda ed un ampio numero di componenti da dover collegare in loop, il testing diverrà complicato. L’unica soluzione possibile è la divisione del loop principale in loop più semplici. Lo sviluppo dei programmi di test risulta quindi essere più semplice da affrontare, poichè diviene quindi possibile raggruppare più componenti dello stesso tipo in gruppi come mostrato in Fig. 5.

È necessario quindi tener conto di questo aspetto durante lo sviluppo della scheda, in modo da includere questo componente e le connessioni necessarie per i cicli di testing già nella fase di net-list. Esempi tipici di IC che possono eseguire questo tipo di partizionamento sono il National Semiconductors SCANSTA 111 e SCANSTA 112. SCANSTA 111 può fornire fino a 3 partizioni mentre SCANSTA 112 fino a 7 partizioni. In caso si necessiti di un maggior numero di partizioni questi componenti possono essere collegati in cascata ad altri dello stesso tipo, utilizzando una delle porte di scansione locale oppure usando un LSP. Per maggiori partizioni si potrebbe impostare un componente per gestire le sequenze di test di una parte del sistema con un test master JTAG embedded, ad esempio SCANSTA 101. Questo può essere controllato dal microprocessore che gestisce il sottosistema e che ha memorizzato i vettori di test. Esso può iniziare una sequenza di test quando il controllore dei test di alto livello richiede l’inizio del testing e, successivamente, notifica i risultati a quest´ultimo.