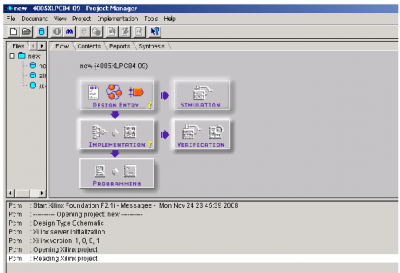

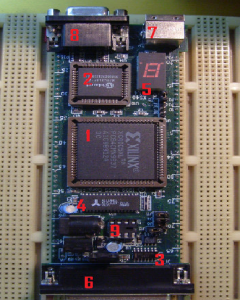

Il software utilizzato per la programmazione della scheda XS40 è il Project Manager 2.1 che fa parte della XILINX FOUNDATION SERIES. E’ un software creato verso la fine degli anni ’90 e dal quale poi è stato successivamente sviluppato l’attuale tool di sviluppo della XILINX: l’ ISE FOUNDATION. In questo paragrafo saranno trattate le operazioni principali che il software è in grado di realizzare, senza scendere troppo nei dettagli di come esse vengono effettivamente eseguite.

La programmazione di un FPGA passa attraverso le seguenti principali operazioni :

-Realizzazione della netlist.

-Simulazione Funzionale.

-Implementazione.

-Download del bit stream.

Per netlist si intende un particolare tipo di file che indichi le connessioni effettuate tra i

dispositivi logici utilizzati nel circuito. Il Project Manager prevede la categoria “Design

Entry” che permette di generare la netlist, attraverso uno dei seguenti approcci :

1. Descrizione del progetto attraverso il linguaggio VHDL (HDL Editor).

2. Realizzazione di una macchina a stati finiti (FSM Editor).

3. Descrizione schematica del progetto (Schematic Editor).

4. LogicBLOX Module generator.

5. Xilinx CORE Generator System.

Il primo dei cinque approcci sopra elencati si basa sul linguaggio VHSIC Hardware Description Language (VHDL) ed è un derivato del programma Very High Speed Integrated Circuit (VHSIC), ideato dal Dipartimento della Difesa Statunitense tra la fine degli anni ‘70 e l’inizio degli anni ‘80. La generazione della netlist tramite linguaggio VHDL avviene attraverso un particolare tool di sintesi integrato nel Project Manager: l’HDL Editor. La sintesi produce la netlist a partire da un opportuno codice e da una libreria in cui sono contenuti gli elementi standard da utilizzare. Ogni famiglia di FPGA ha una propria libreria di elementi standard come porte logiche, buffer, contatori, mux , ecc. La descrizione VHDL può essere eseguita anche nello Schematic Editor, in quanto un codice completo può essere importato come un vero e proprio blocco logico.

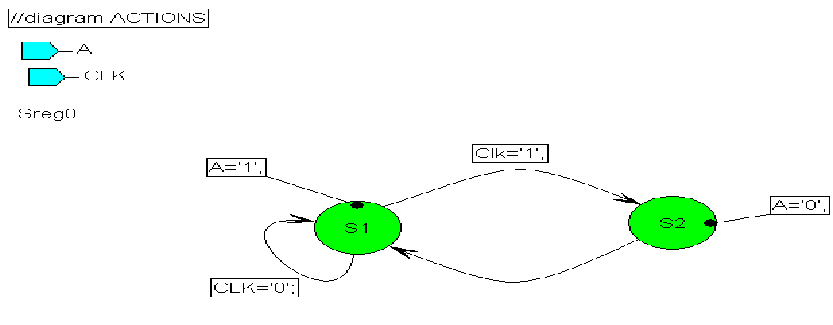

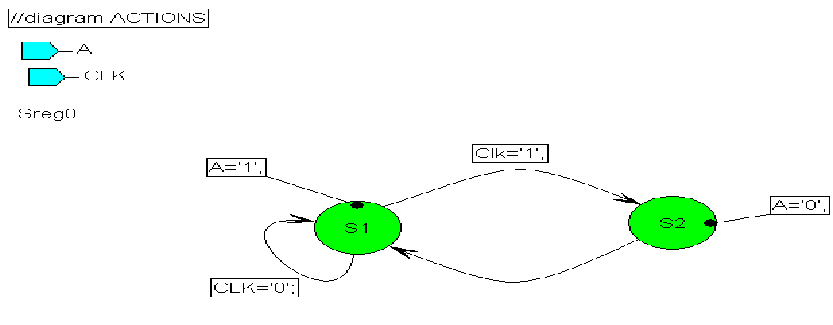

Nella figura precedente è possibile vedere un esempio realizzato tramite il secondo approccio: realizzare una “Finite State Machine “ ossia una macchina a stati finiti. Questa strada può essere utile da seguire per descrivere gli stati di una macchina elementare (contatori , riconoscitori di sequenza, ecc.. ), la quale potrà poi essere utilizzata nello Schematic Editor per comporre il nostro progetto finale. In generale, non è consigliabile seguire l’approccio a stati finiti per realizzare l’intero progetto, dato che in questo caso è impossibile visualizzare i collegamenti fisici tra i vari dispositivi e quindi verificarne l’esattezza in fase di simulazione.

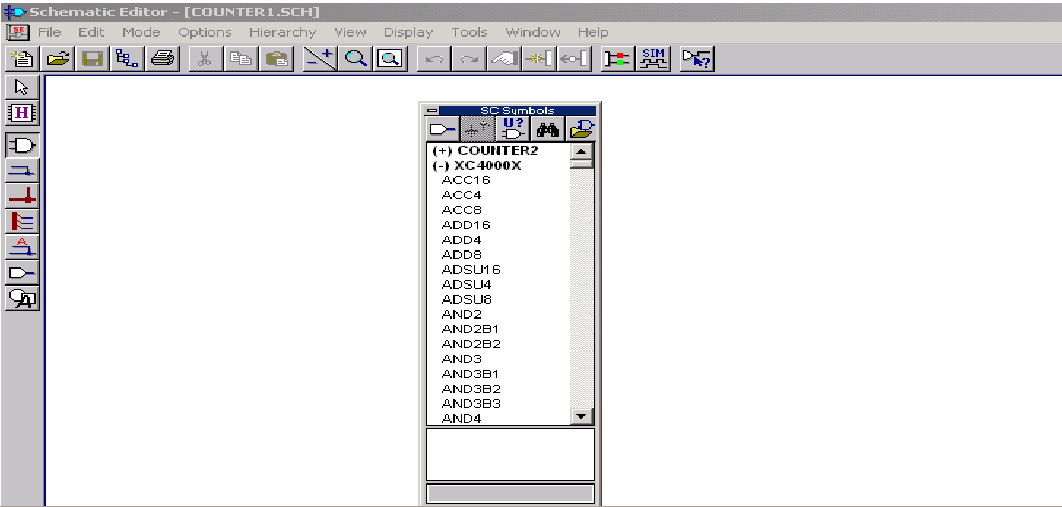

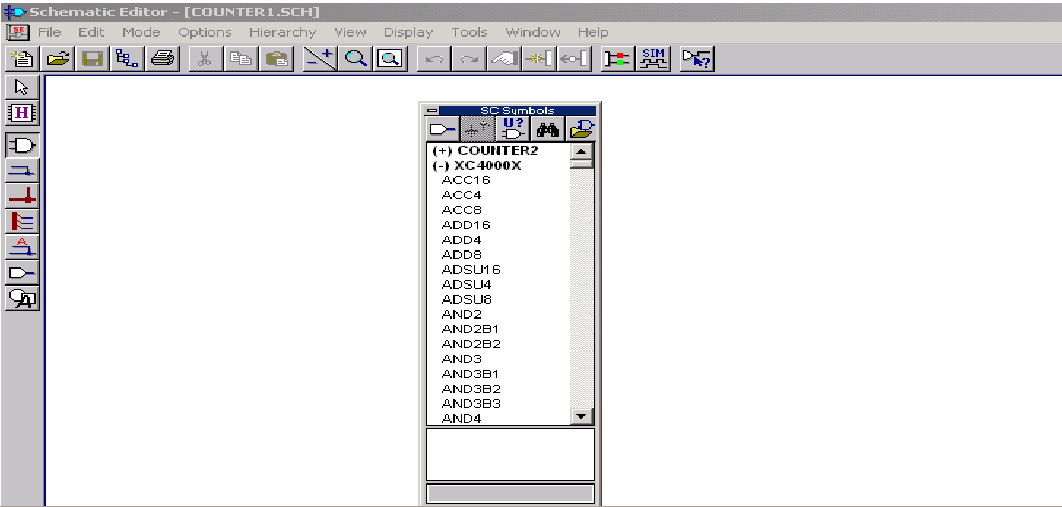

Il terzo approccio riguarda il vero e proprio disegno dello schematico attraverso lo Schematic Editor. Come già detto in precedenza, è possibile importare sia le FSM che codici VHDL all’interno dello Schematic Editor, per poi collegarli

opportunamente tra di loro. Inoltre, in questo editor è possibile sfruttare le librerie di ogni diversa famiglia di FPGA, in cui sono contenuti tutti gli elementi logici standard che possono essere importati nello schematico. Infine ,dopo aver disegnato l’intero

progetto, utilizzando l’opportuno comando di “Create Netlist “ l’editor attiva il tool di sintesi che produce il file con estensione “ .ALB ” che rappresenta la netlist del progetto.

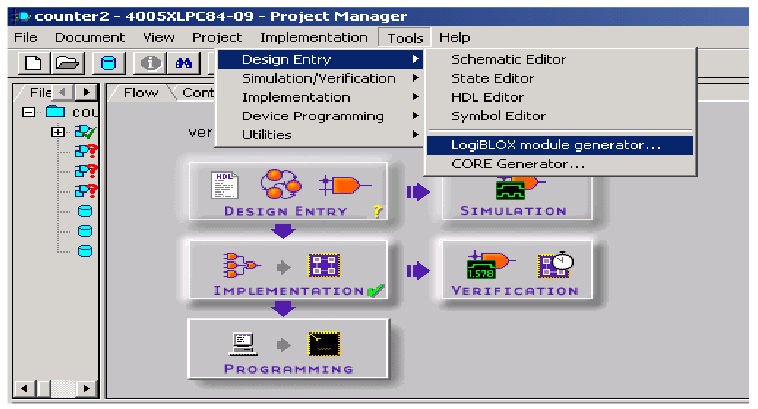

Il quarto approccio riguarda l’utilizzo del LogiBLOX module selezionabile dalla schermata principale del Project Manager mostrata di seguito:

Questo modulo permette l’implementazione automatica di macchine di uso comune nei circuiti logici come: adder, comparatori, memorie, decoder, ecc. L’utilizzo di questo modulo può essere utile per ridurre i tempi di elaborazione del progetto, purché

ci si assicuri che il componente generato svolga effettivamente le funzioni richieste.

Infatti, non è possibile entrare nel cuore della descrizione comportamentale del blocco una volta che esso è stato creato. E’ però possibile selezionare diverse opzioni inerenti alle funzionalità del blocco logico, attraverso la schermata principale del LogiBLOX.

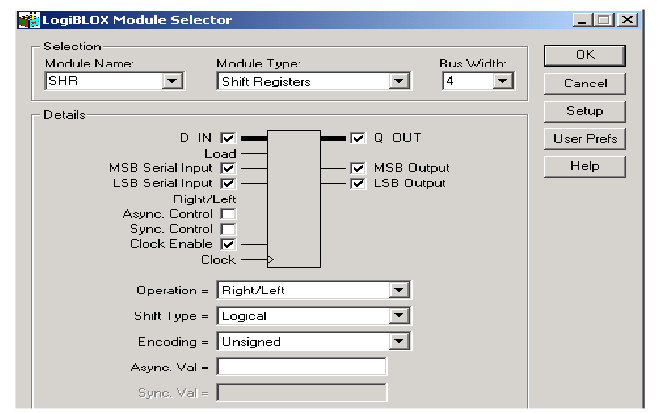

Di seguito riportiamo un esempio di shift register a 4 bit implementato utilizzando quest'ultima feature del Project Mangaer 2.1:

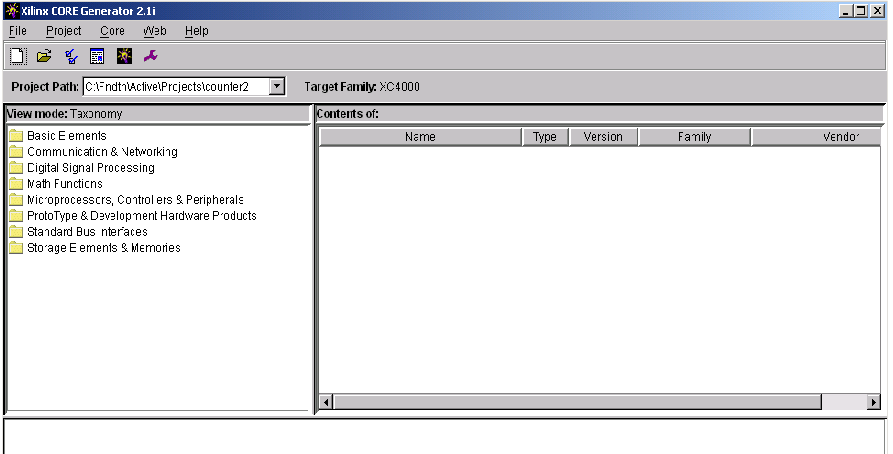

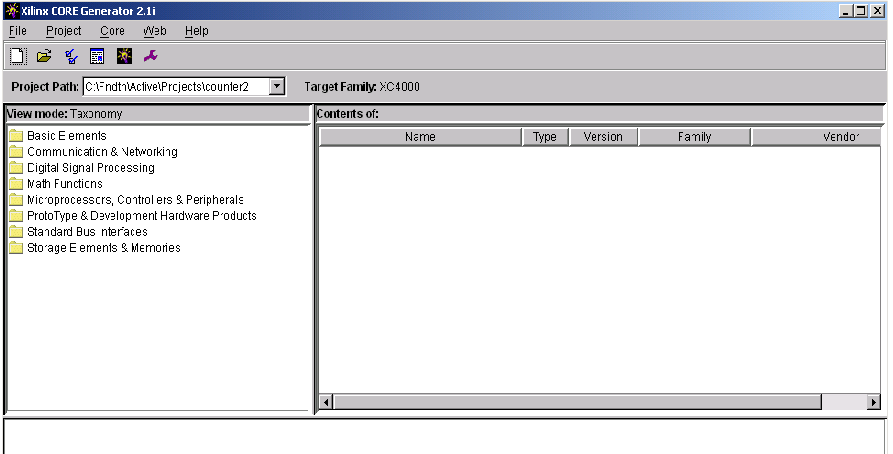

Il quinto ed ultimo approccio prevede l’uso dello Xilinx CORE Generator System, che contiene un insieme di funzioni, che vanno dalle semplici operazioni matematiche alle più complesse operazioni di elaborazione digitale. Tutte queste funzioni sono già implementate e quindi utilizzabili all’interno dello Schematic Editor. Ovviamente l’insieme di funzioni implementabili dipende dal particolare FPGA su cui si opera. Di fatto, uno dei parametri da impostare inizialmente nello Xilinx CORE Generator System è proprio la famiglia di FPGA su cui poi si vuole sviluppare.

Una volta terminata la fase di realizzazione della Netlist, è possibile passare alla fase successiva di simulazione funzionale del progetto. Questa fase prevede l’applicazione di opportuni “stimoli “(segnali di ingresso), e l’analisi successiva dell’andamento temporale di tutti i segnali desiderati al fine di testare l’effettivo funzionamento delle varie parti del progetto. E’ importante sottolineare però che questa simulazione non tiene in conto dei tempi di ritardo prodotti dall’implementazione hardware della logica.

Leggi anche:

https://it.emcelettronica.com/forum/fpgavhdle-tool-di-sviluppo-vi-piacerebbe-parlarne

Ti potrebbe interessare anche:

Mi sembra un pò troppo semplificata la cosa!!

Senza entrare nel dettaglio, magari scrivo un articoletto a riguardo, la programmazione di un FPGA passa attraverso i seguenti passi fondamentali:

1)descrizione del sistema (linguaggi HDL, schema, code generator ecc)

2)Simulazione logica

3)Sintesi (Netlist logica)

4)simulazione funzionale (post sintesi)

5)Fitting (–> Netlist gate level)

6)Impostazioni dei timing constrain.

6)simulazione gate level (post fitting che include i ritardi di interconnessione)

7)Download del bit stream

Ognuno di questi passi in realtà implica l’eseguire altri sotto passi. Forse il tool di sviluppo nasconde, per semplificare, alcuni di questi passi. Ma il processo di Fitting e di timing constrain non possono mancare nel tool che descrivi. Anche il software di altera Max+Plus contemporaneo a Project Manager 2.1, mette in evidenza la maggior parte dei passi che ho elencato.

Tra laltra in una delle immagini che hai messo si vedono il fitting, nominato implementation, e il passo di timing analisys e timing constrain nominato verification.

La frase “In generale, non è consigliabile seguire l’approccio a stati finiti per realizzare l’intero progetto, dato che in questo caso è impossibile visualizzare i collegamenti fisici tra i vari dispositivi…… ” Non mi è molto chiara.

Tutti i tools di sviluppo di questo tipo come passo finale generano del codice sorgente che descrive la nostra macchina a stati e in più generano un simbolo logico da utilizzare in un apporccio descrittivo a schema elettrico. In simulazione dovresti poter vedere tutto della tua FSM altrimenti che simulazione è?

La frase “L’utilizzo di questo modulo può essere utile per ridurre i tempi di elaborazione del progetto…..” Forse intendi “ridurre i tempi di sviluppo…”?

Forse è uno strumento un pò troppo vecchiotto!! 🙂

Non è solo una questione di quantità di dati o di risorse utilizzabili del dispositivo, ma della capacità di controllo e analisi di ciò che si stà facendo!!!

Io aggiungerei il fatto che esistano altri linguaggi di programmazione per FPGA ad esempio nel mondo di anglosassoni e molto le diffusob il Verilog è poco poco si sta diffondendo un altro linguaggio basato sul linguaggio c chiamato SystemC

secondo me non è così vecchiotto come strumento di sviluppo visto che a volte non è necessario tirare al massimo le risorse disponibili, ma bastano cose semplici senza andare nella stravaganza o trattare mole di dati dell’ordine di centinaia gigaflop al secondo.

non è vero dipende il dispositivo che devi controllare,

faccio un esempio semplice alcuni dispositivi possono essere controllati in pura analogica,

prendi un frigo una cella frigorifero per fare un controllo al limite basta soltanto UA741 in modalità compratore.

semplice perfettamente efficace e perfettamente affidabili.

ecco il componente era disponibile prima che nascessi io.

Non ho capito a cosa ti riferisci!! Cosa c’entra il ua741 con l’implementazione di una FPGA??? Comunque il sotftware è obsoleto ormai, prova a dare un’occhiata alle ultime versioni e ti accorgerari di quanti strumenti hai a disposizione per l’implementazione e la verifica del progetto.

Ciao ragazzi scusate ma rispondo appena posso in dettaglio comunque si il software è vecchio così come la scheda….e poi ero alle prime armi quindi l ho pubblicato anche per capire quanto di più si poteva fare e si può fare grazie allora aiuto della community …vi scrivo presto ciao

Ciao mino finalmente riesco a risponderti allora faccio un elenco di risposte:

1) Si hai ragione infatti avevo previsto un altro articolo in cui descrivere nel dettaglio le fasi che hai detto (tranne quella a gate level che non ho mai visto purtroppo)..in realtà mostrerò le fasi utilizzando il vero e proprio circuito che ho realizzato 😉

2) Riguardo la frase dei collegamenti mi riferivo allo schema vero e proprio della FSM..non a quello che realizzi realmente nell’fpga…si hai ragione è scritto un pò troppo scarno.. Intendo che se tu disegni il diagramma di stati praticamente puoi vedere le commutazioni logiche da uno stato all’altro ma non si riesce a controllare come implemenentare quel comportamento logico (almeno così ho capito io…) cioè con quali porte/dispositivi logici si può realizzare tutto il processo..

3)si i tempi di sviluppo 🙂 non quelli relativi al timing ;)..

si è uno strumento vecchiotto ma semplice da cui iniziare prima di lanciarsi di petto nell ise 13 !! ma con tutti gli help che ci stanno oggi…

ciao e grazie per i commenti sempre ben accetti soprattutto quando critici e costruttivi come i tuoi 😉

ps

l’articolo di cui ti parlavo è già uscito..eccolo:

http://it.emcelettronica.com/flow-manager-i-passi-realizzazione-del-bit-stream-fpga-xilinx