Questo articolo descrive i requisiti tipici da soddisfare nel progetto di uno stadio di alimentazione per FPGA. Si prenderanno in considerazione due famiglie di prodotti di costruttori leader nel segmento FPGA. Infine, verrà presentata una soluzione applicativa.

Per questo articolo consideriamo due prodotti FPGA, Virtex-5 di Xilinx e Stratix III di Altera. Si tratta di due famiglie di prodotti in tecnologia da 65 nm di fascia alta che contengono piattaforme a elevate prestazioni, alta velocità ed elevato pin out, in maniera da garantire un’estrema flessibilità per l’utilizzatore. Il primo obiettivo è definire quali sono i requisiti di un sistema di alimentazione per le FPGA in esame, soprattutto valutando la necessità di più livelli di tensione e di corrente, la necessità di un'adeguata sequenza di uscita e le caratteristiche di startup dei singoli dispositivi.

REQUISITI DELL’ALIMENTAZIONE

Le FPGA Virtex-5 o le Stratix III generalmente richiedono almeno due differenti livelli di tensione. Per Virtex-5 la tensione di core raccomandata è di 1,0 V ± 50 mV, mentre per Stratix III può essere scelta tra 0,9 V ± 40 mV oppure 1,1 V ± 50 mV. A seconda dello standard di I/O implementato, l’alimentazione degli I/O della Virtex-5 può variare da 1,14 V a 3,45 V, i livelli di I/O ottenibili sono: 1,2 V, 1,5 V, 1,8 V, 2,5 V e 3,3 V. In maniera analoga la Stratix III riporta tra le specifiche la possibilità di alimentare gli I/O da 1,14 V a 3,15 V per ottenere di conseguenza i livelli: 1,2 V, 1,5 V, 1,8 V, 2,5 V e 3,0 V. In aggiunta la Xilinx definisce una tensione ausiliaria che deve essere di 2,5 V ± 5% per alimentare le risorse di clock dell’FPGA. Anche Altera definisce dei livelli specifici per le sezioni analogiche e digitali dei PLL, per i pre-driver di I/O, per gli ingressi differenziali del clock e così via. Solitamente viene richiesto che l’alimentazione gestisca transitori di corrente consistenti durante lo startup del sistema, mentre a regime le correnti statiche e dinamiche risultano invece più basse. Le tempistiche per la rampa di power-up per ogni livello di tensione vanno da 0,2 ms a 50 ms per Virtex-5, mentre per Stratix III da 0,1 ms a 100 ms.

PROGETTO DELL’ALIMENTAZIONE

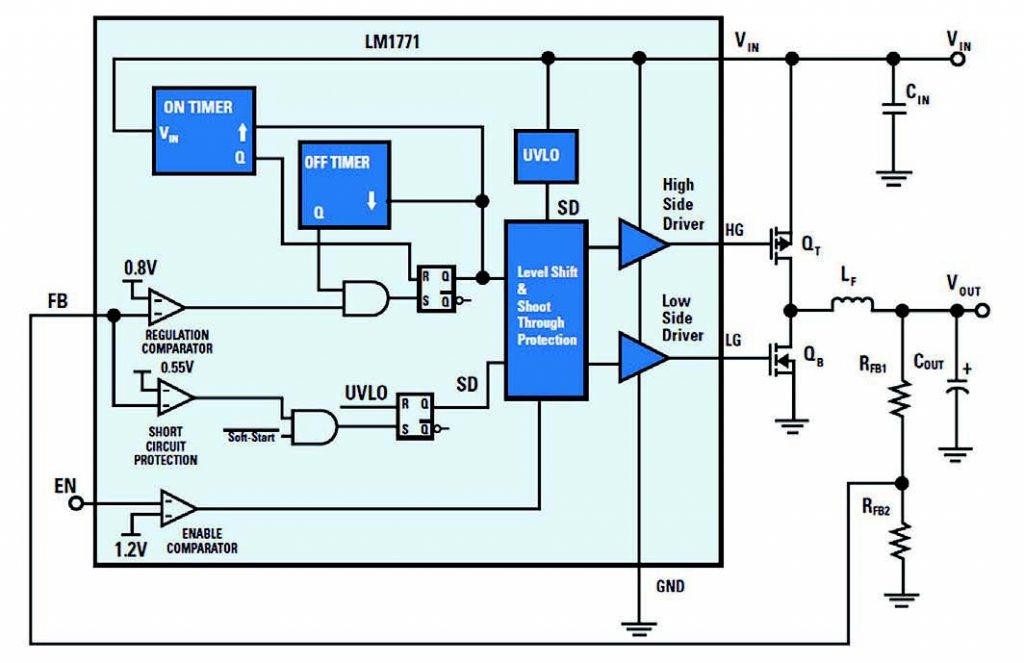

Il progetto dello stadio di alimentazione che andremo a sviluppare è basato su Virtex-5. Un progetto analogo può essere fatto per utilizzare Stratix III, con piccole modifiche, riportate nel paragrafo precedente. Per Virtex-5 le tensioni sono denominate rispettivamente VCCINT per la tensione di core, VCCAUX per la tensione ausiliaria e VCCO per la tensione di I/O. La sequenza di power-on deve fornirle nell’ordine in cui sono appena state presentate, sebbene qualsiasi sequenza di alimentazione monotonica sia tollerata. In ogni caso rispettare questa sequenza risulta vantaggioso per ridurre al minimo la corrente di in rush richiesta. La soluzione proposta per realizzare lo stadio di alimentazione della Virtex-5 utilizza il controllore PWM LM1771 della National Semicondutor. Tale controllore ha tra le caratteristiche la possibilità di eseguire il power-up e il power-down individuale delle tensioni sfruttando il sequencer LM3880. Il diagramma a blocchi dell’LM1771 con i relativi componenti esterni è mostrato in Figura 1.

Figura 1: LM1771 DC-DC Buck con architettura di controllo COT

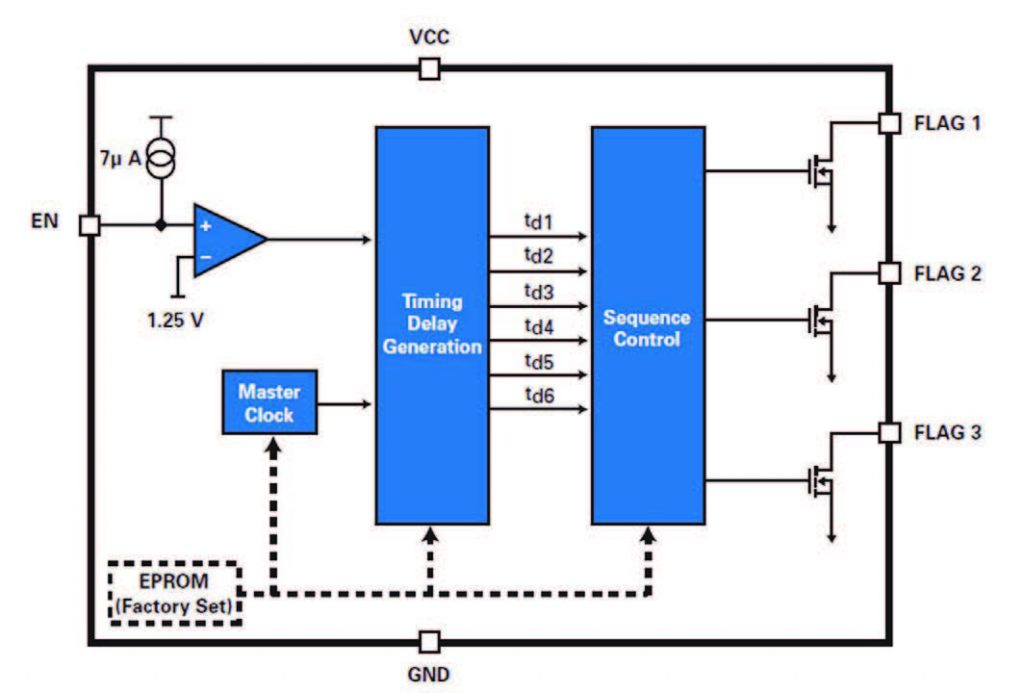

L’LM1771 è un convertitore switching di tipo buck, disponibile nei package MSOP-8 e in LLP6, in grado di convertire una tensione d’ingresso tra 2,8 V e 5,5 V in una tensione d’uscita regolata inferiore a 0,8 V. Il convertitore pilota due MOSFET esterni, un PFET in high side e un NFET in low side, utilizzando un’architettura di controllo con tempo di on costante (COT) che elimina la necessità di un amplificatore d’errore e dei componenti di compensazione esterna. In questo modo, la risposta a transitori veloci di corrente sul carico sono possibili. In aggiunta, l’LM1771 dispone di un pin di enable estremamente preciso per agevolare la sequenza di avvio. Sono tre le diverse tipologie di questo componente che differiscono per le tempistiche: la S, la T e la U, riportati nel part number del componente. Ogni versione permette di lavorare a una frequenza diversa per una determinata tensione d’uscita. Per un determinato set di tempistiche operative la frequenza di switching risulta indipendente dalla tensione d’ingresso; anche il controllo sull’ingresso di feed-forward modifica i tempi di switch del MOSFET alto in funzione della tensione d’ingresso, mantenendo costanti i volt per secondo al nodo di switching. In virtù delle dimensioni estremamente ridotte del package, l’LM1771 permette di occupare poco spazio sul PCB senza sacrificare efficienza e performance. L’LM3880 è presentato nel suo schema a blocchi in Figura 2.

Figura 2: schema a blocchi dell’LM3880

Il package disponibile per il componente è il SOT23-6, nel quale tre uscite open drain permettono di controllare tre pin di enable di altrettanti LM1771. Una volta abilitato l’LM3880, i tre segnali di abilitazione sono attivati in sequenza, dopo i tempi di attesa specifici, permettendo agli alimentatori di eseguire il power-up nella sequenza desiderata. I tre segnali di abilitazione seguono poi la sequenza inversa durante il power-down del sistema per evitare condizioni di latch-up. Le opzioni standard prevedono tempistiche di 10 ms, 30 ms, 60 ms e 120 ms. Volendo, il componente può essere anche programmato in fase di costruzione con tempistiche specifiche e abbinato a sei diverse modalità di power-down.

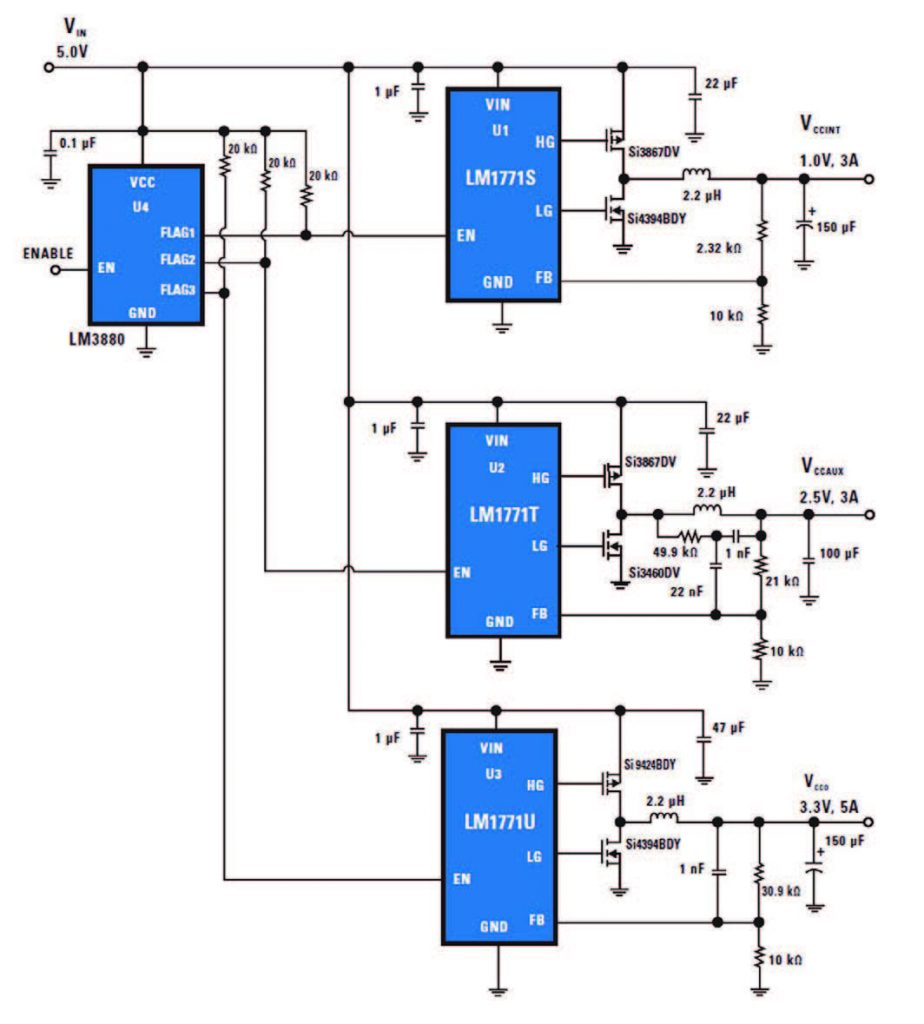

REALIZZAZIONE DELL’ALIMENTATORE

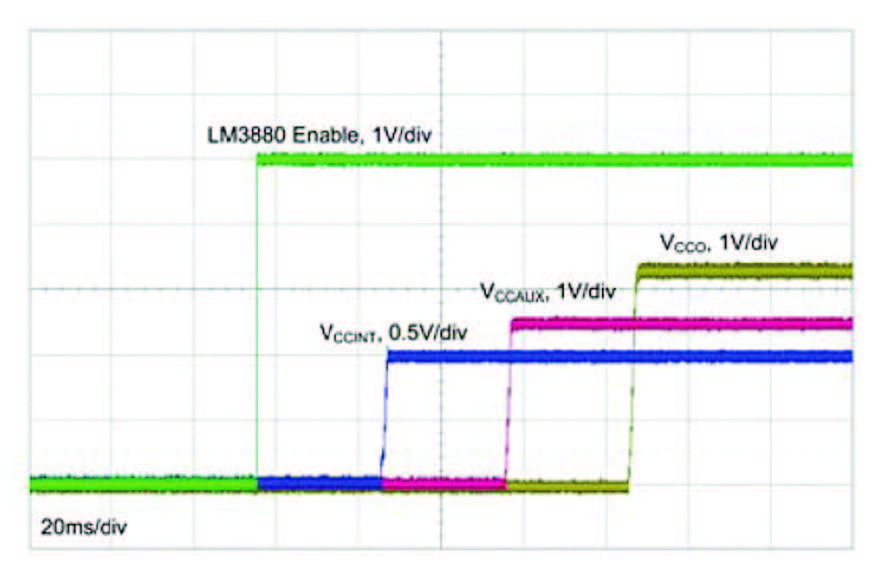

La sequenza tra LM1771 e LM3880 è mostrata in Figura 3.

Figura 3: catena di alimentazione per la Virtex-5

Per questo progetto, i tre canali dei regolatori buck sono dimensionati per fornire una corrente continuativa al carico di 5 A, 3 A e 3 A rispettivamente per ICCO, ICCAUX e ICCINT. La tensione degli I/O è impostata a 3,3 V, ma può essere facilmente modificata intervenendo su una delle resistenze di feedback del regolatore. I livelli di core e degli ausiliari sono impostati a 1,0 V e 2,5 V rispettivamente. I regolatori della tensione di core, degli ausiliari e degli I/O sono realizzati rispettivamente con LM1771S, LM1771T e LM1771U che lavorano alle frequenze di 606 kHz, 758 kHz e 500 kHz. Ogni alimentazione ha la propria capacità di filtro collocata il più vicino possibile ai FET di potenza a canale n e a canale p. In aggiunta sull’ingresso è collocata una piccola capacità di bypass per ogni LM1771. Le capacità del filtro d’uscita sulla tensione di core e sugli I/O sono al tantalio e sono scelte per avere la necessaria resistenza serie equivalente (ESR) allo scopo di mantenere un ripple sufficiente sul pin di feedback (FB). Una capacità di feed-forward dalla VCCO al pin FB incrementa l’ampiezza del ripple visto dall’LM1771.

La capacità d’uscita della tensione ausiliaria è di tipo ceramico, per minimizzare il livello di rumore su questa alimentazione. Una rete capacitivo-resistiva lavora come current sense in prossimità dell’induttanza di filtro, crea una forma d’onda triangolare, che viene accoppiata in AC al nodo di FB. Questo circuito può essere anche utilizzato per le alimentazioni di core e I/O se la capacità al tantalio non è adeguata o se una capacità ceramica a bassa ESR diventa indispensabile localmente al regolatore o in prossimità dell’FPGA. Le induttanze di filtro sono progettate per lavorare con correnti elevate, hanno bassa resistenza AC e DC, in maniera da massimizzare l’efficienza. Il valore di induttanza è determinato dalla corrente di ripple pari al 30% della corrente al carico. Inoltre, sarebbe bene scegliere un componente con una leggera saturazione, in maniera da poter gestire transitori ad elevata corrente ma di breve durata in aggiunta alla corrente nominale al carico. I FET sono in package TSOP-6 per la tensione ausiliaria, mentre sono in SO- 8 per il canale di alimentazione degli I/O. L’alimentazione di core, visto che utilizza un duty cycle basso nel punto di lavoro, ha il MOSFET in high-side in package TSOP-6 e quello in low-side in SO-8. La versione di LM3880 scelta è quella a ritardo 30 ms, siglata –1AB. Alcune resistenze esterne di pull-up sono collegate a ogni segnale open drain in uscita.

PERFORMANCE

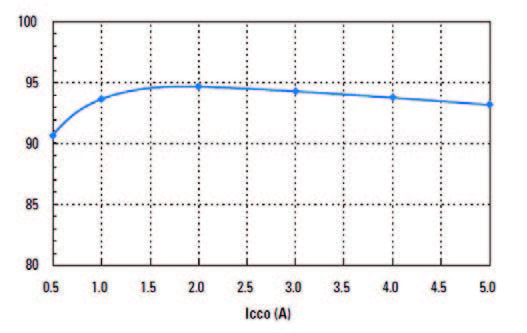

L’efficienza del canale di alimentazione degli I/O, che lavora in maniera indipendente a 5 V in funzione della corrente, è mostrata in Figura 4.

Figura 4: efficienza del canale di alimentazione degli I/O vs ICCO, Vin = 5 V

L’efficienza complessiva dei tre regolatori operanti a pieno carico, comprensivi delle correnti assorbite dall’LM3880, è del 90,5%. Questo si traduce in una potenza in uscita di 27 W con 2,85 W dissipati. In Figura 5 viene mostrata la sequenza monotonica di startup controllata dall’LM3880. I ritardi tra i rispettivi startup sono di 30 ms.

Figura 5: sequenza di startup, Vin = 5 V