Sul blog di Elettronica Open Source puoi leggere non solo tutti gli articoli Premium riservati agli abbonati Platinum 2.0 e inseriti nella rivista Firmware 2.0 (insieme ad articoli tecnici, progetti, approfondimenti sulle tecnologie emergenti, news, tutorial a puntate, e molto altro) ma anche gli articoli della Rubrica Firmware Reload. In questa Rubrica del blog abbiamo raccolto gli articoli tecnici della vecchia rivista cartacea Firmware, che contengono argomenti e temi evergreen per Professionisti, Makers, Hobbisti e Appassionati di elettronica. Ormai l’interfaccia USB 2.0 è diffusissima in moltissime applicazioni. L’obiettivo è quello di fornire delle linee guida per il design e per il layout della scheda che ci permettano di arrivare velocemente ad avere un’interfaccia USB affidabile e robusta.

Dando per scontato una conoscenza di base dell’interfaccia USB, partiamo subito con l’individuare quali sono le principali fonti di problemi nel progettare una comunicazione USB 2.0. Le frequenze di clock rappresentano la maggior sorgente di energia per un design USB. Le linee dati differenziali sono in grado di lavorare alla massima velocità a 480 Mbps. Il clock di sistema può quindi lavorare a 12, 48 e 60 MHz. Il cavo USB potrebbe comportarsi come un’antenna, sarà quindi necessario prendere le dovute precauzioni. I segnali da curare nel design di un’interfaccia USB sono di quattro tipi:

- Segnali di interfaccia tra i dispositivi: clock e segnali dati tra i vari dispositivi presenti sulla scheda.

- La potenza in ingresso e in uscita dal cavo. Dal pin 1 del cavo USB (VBUS) devono passare solo segnali a bassa frequenza (sotto 100 kHz) e il filtraggio deve essere massiccio. Dal pin 4 del connettore USB (massa analogica) deve essere possibile far passare tutta la corrente richiesta durante la trasmissione dei dati e il filtraggio deve essere esiguo.

- Le linee dati USB: sono due segnali differenziali che viaggiano su doppino ritorto. Genericamente vengono indicate con DP e DM (oppure D+ o D-). A seconda della velocità di trasferimento, devono commutare ad una frequenza di 240 MHz (per high speed), 6 MHz (per full speed) e 750 kHz (per low speed).

- Il segnale proveniente dal quarzo esterno: le frequenze fondamentali sono 12 MHz, 19,2 MHz, 24 MHz e 48 MHz. Quando si utilizza il quarzo esterno come riferimento per il clock, solitamente si sceglie un valore pari o superiore a 24 MHz.

PIAZZAMENTO DEI COMPONENTI E ROUTING

Andiamo adesso a definire alcune linee guida da seguire per il piazzamento dei componenti e la tracciatura delle piste per la realizzazione del layer fisico (PHY) dell’USB. Seguendo queste indicazioni si ottimizza la qualità del segnale e si minimizzano problematiche di interferenza (EMI).

- Partire piazzando prima i componenti relativi all’USB PHY senza essere partiti con il routing.

- Tracciare prima le piste relative ai clock ad alta velocità e le linee USB differenziali, cercando di minimizzare la lunghezza.

- Tracciare queste piste sul layer vicino al piano di massa.

- Per queste piste cercare di minimizzare l’uso di vie o la creazione di angoli, se necessario fare un angolo a 90 gradi, meglio disegnarne due da 45 o realizzare un arco. Questa soluzione minimizza le riflessioni e non genera discontinuità di impedenza.

- Le piste USB non devono viaggiare vicino a quarzi, oscillatori, generatori di clock, regolatori switching, fori di montaggio, dispositivi magnetici o circuiti integrati che usano moltiplicatori di clock.

- Evitare ramificazioni sui segnali USB high-speed, poiché ogni ramo è sorgente di riflessioni, se proprio non è possibile evitarlo allora la lunghezza del ramo deve essere inferiore a 5 mm (200 mils).

- Tracciare le piste dei segnali USB tutte integralmente su un unico piano (VCC o GND), senza interruzioni e senza attraversare zone a diversa tensione sullo stesso piano.

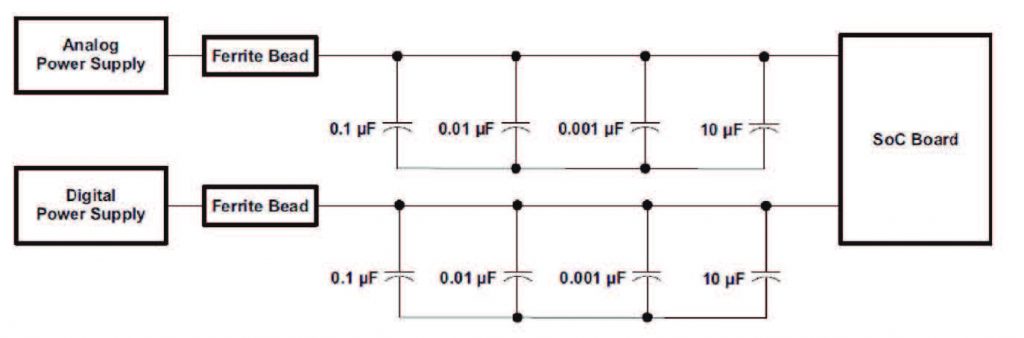

Per quel che riguarda il routing o il layout di scheda, alcuni punti chiave devono essere analizzati in dettaglio. Partiamo considerando le tensioni di alimentazione analogica, per i PLL, e per la parte digitale dei chip. Per minimizzare le EMI è necessario aggiungere capacità di disaccoppiamento con un anello in ferrite in corrispondenza dei terminali di alimentazione analogica, PLL e della circuiteria digitale. Questi componenti devono essere collocati più vicino possibile ai chip ritenuti potenziali sorgenti di interferenze, per minimizzare l’induttanza della linea e il contributo di rumore che questo introduce. In Figura 1 è mostrato un filtraggio come discusso, per una parte analogica e per una digitale. In caso di più pin di alimentazione con la stessa funzione conviene tenerli collegati assieme in un unico punto a bassa impedenza e aggiungere ulteriori capacità alla ferrite.

Figura 1: Configurazione con capacità e ferrite per minimizzare le EMI

In generale, per l’alimentazione proveniente dal bus USB valgono le seguenti indicazioni:

- Utilizzare una capacità da 0,01 F tra la linea VBUS e la GND di telaio, in prossimità del connettore USB.

- Utilizzare una capacità da 0,01 F tra la massa e la GND di telaio in prossimità del connettore USB.

- Se viene utilizzato un regolatore di tensione, inserire una capacità da 0,01 F all’ingresso e all’uscita, per aumentare l’immunità alle ESD e ridurre le EMI.

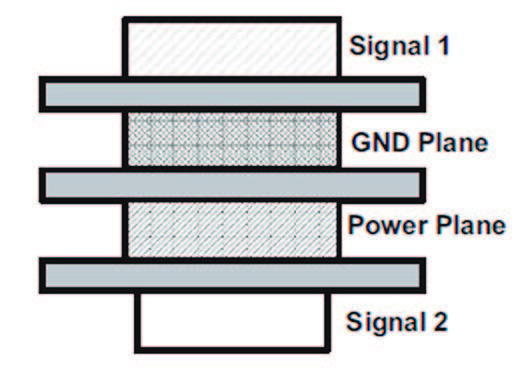

Le varie masse, quella analogica, digitale e dei PLL devono essere collegate in un unico punto a bassa impedenza sul piano di massa. Affrontiamo il discorso della stratificazione della scheda, per schede con interfaccia USB e alte frequenze in gioco è sempre raccomandabile avere almeno 4 strati. Due layer di segnale separati da due di alimentazione, come in Figura 2.

Figura 2: Struttura di scheda a 4 livelli

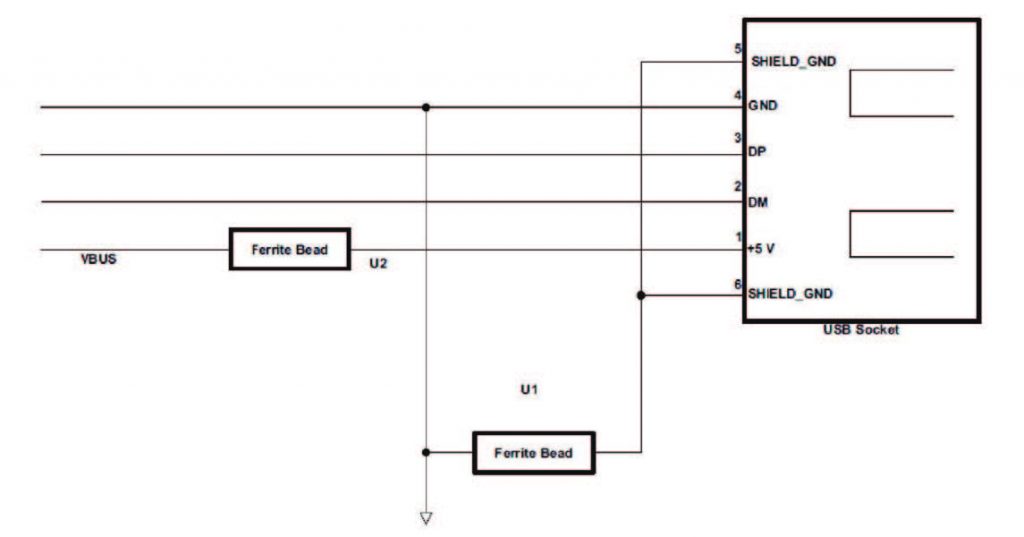

La maggior parte delle piste di segnale viaggiano su un solo strato, preferibilmente il layer SIGNAL 1 di Figura 2, subito sotto quello di massa. Per quel che riguarda connettori e cavi la Figura 3 è esplicativa.

Figura 3: Connettore USB

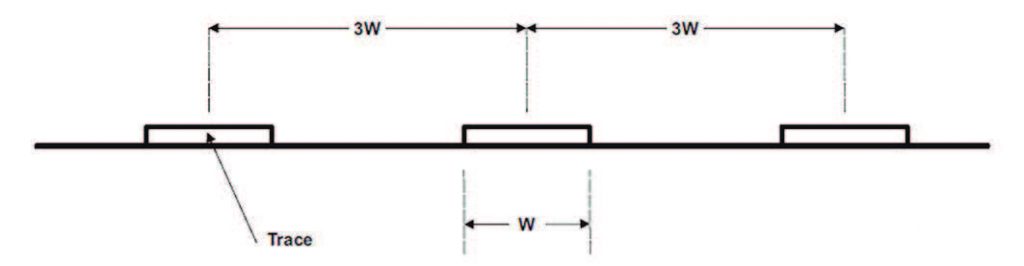

Un anello in ferrite sulla linea di VBUS subito sotto il connettore prima che si colleghi alla pista può aiutare a bloccare subito le cause di EMI, evitando di trasformare tutto in una grande antenna. La ferrite deve avere resistenza tra 47 e 1k ohm a 100 MHz e continuare a far pesare la propria parte resistiva fino al GHz di frequenza. Anche la schermatura del cavo con anello andrebbe collegata alla massa della carcassa del connettore. Questa ferrite può avere impedenza tra 10 e 50 ohm a 100 MHz e iniziare a far sentire maggiormente la componente resistiva a frequenze prossime al GHz. Discutiamo anche delle piste di clock e dei quarzi; per evitare problemi di emissioni tra le piste di clock solitamente si usa mettere delle resistenze tra 10 e 130 ohm in serie. Solitamente il valore giusto si ricava sperimentalmente verificando le forme d’onda del segnale di clock con un oscilloscopio. La resistenza va piazzata vicino alla sorgente che genera il clock e il valore non deve distorcere la forma d’onda ottenuta. Una regola semplice per il tracciamento delle piste di clock è quella delle “3W”, ossia la distanza tra il centro della pista di clock e qualsiasi altra traccia adiacente deve essere almeno 3 volte la larghezza della pista di clock (vedi Figura 4).

Figura 4: Regola di spaziatura “3W”

Grazie a questo semplice accorgimento, la diafonia tra le piste di clock e quelle adiacenti è minimizzata. Per quanto riguarda i quarzi, vanno tenuti, insieme ai relativi condensatori, vicini ai pin del chip che implementa il livello fisico dell’USB. Spesso le frequenze provenienti dalle sorgenti di alimentazione (regolatori a commutazione) e dalle grandi capacità possono modularsi con la frequenza del quarzo, per questo motivo questa situazione va evitata. Da notare che la potenza varia con il quadrato della corrente e che la corrente è proporzionale al carico capacitivo, perciò una riduzione del carico capacitivo della metà si tradurrà in un consumo di ¼ di potenza rispetto al valore originario. Una parte importante del layout considera le linee differenziali dell’interfaccia USB. Il transceiver USB fisico deve essere collegato il più possibile vicino al connettore USB 2.0. La dinamica dei segnali durante una comunicazione high speed è di 400mV ± 10%, perciò ogni rumore differenziale sulle linee va ad incidere sulla qualità di ricezione. Quando i segnali DP e DM non hanno nessuna forma di schermatura, tendono a comportarsi come antenne e raccogliere tutti i disturbi generati dai componenti circostanti. Per ridurre o evitare questo fenomeno sono indispensabili alcuni accorgimenti:

- le piste di DP e DM devono essere della stessa lunghezza e non superare i 10 cm;

- le piste DP e DM devono viaggiare appaiate e distanti dalle altre piste;

- la connessione high speed viene realizzata attraverso un doppino intrecciato e schermato con un’impedenza differenziale di 90Ω ±15%. Nel layout, l’impedenza di DP e DM deve essere ognuna di 45Ω ± 10%;

- non ci devono essere componenti extra per mantenere l’integrità di segnale (ossia le piste non possono essere portate a due distinti connettori USB).

ESD

Per ottenere il marchio CE tutti i prodotti/sistemi devono soddisfare dei requisiti standard definiti dall’IEC attraverso diverse norme. Per esempio, la IEC 61000-4-2 tratta l’argomento delle ESD e richiede che il prodotto/sistema superi una prova con scariche a contatto di 8kV e in aria di 15kV. Non ci devono essere danneggiamenti e il dispositivo deve continuare a lavorare normalmente al termine del test. Ovviamente, questo tipo di test interessa particolarmente l’esterno del sistema e il relativo “involucro”, tuttavia, l’USB solitamente è una delle parti che compaiono accessibili all’esterno e per questo sensibili al problema delle ESD. Lo stesso layout della scheda interviene nel minimizzare gli effetti delle scariche elettromagnetiche, infatti, incide l’attenuazione tra il punto di scarica e il tratto di cavo sino al circuito integrato oltre che l’induttanza serie del PCB. In generale, le raccomandazioni per irrobustire il design rispetto alle scariche ESD sono le seguenti:

- Inserire schermature metalliche per le parti più sensibili

- Separare la massa del telaio da quella della scheda

- Lasciare uno strato di aria per assorbire l’energia sviluppata dalle ESD

- Inserire dei diodi di protezione per scaricare l’energia delle scariche

- Inserire delle capacità per assorbire localmente l’energia delle scariche

- Non inserire componenti esterni dedicati alle ESD sulle linee differenziali dell’USB, potrebbero inficiare la qualità del segnale

CONCLUSIONI

Questo articolo non vuole essere una trattazione esaustiva su come realizzare il layout di un’interfaccia USB, ma solo dare delle linee guida con le quali sia più facile evitare i problemi più comuni che si possono incontrare nel progetto di un’interfaccia USB, specialmente se di tipo “high speed”.