In questa lezione affronteremo un argomento apparentemente marginale, ma in realtà fondamentale nello sviluppo di applicazioni embedded: il sistema di distribuzione del clock, quella rete più o meno complessa che porta il segnale di clock del nostro sistema embedded dalla sorgente (clock source) ai vari componenti che lo compongono (CPU, memorie, bus, periferiche e altro).

Introduzione

Il SAMD21 possiede un sofisticato sistema di distribuzione del segnale di clock, progettato per offrire la massima flessibilità. Questo sistema consente al progettista di regolare performance e consumo energetico del device dinamicamente, in modo da raggiungere il compromesso ottimale nelle diverse applicazioni.

Il clock tree: il sistema di distribuzione del clock del SAMD21

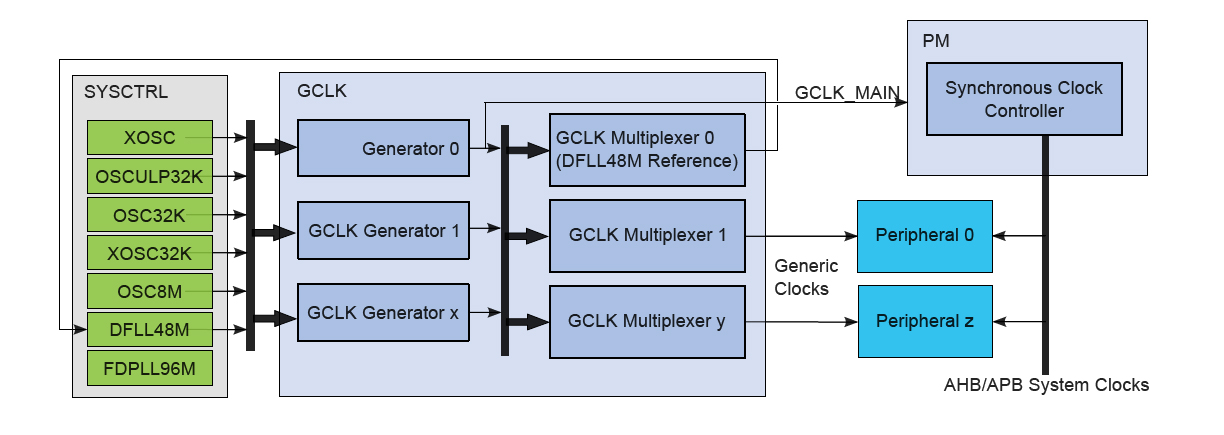

Il sistema di distribuzione del clock (clock tree) del SAMD21 (figura 1) è costituito da:

- le sorgenti (clock sources), controllate dal System Controller (SYSCTRL) e che forniscono una base temporale per i vari componenti (ad esempio i generatori del clock): un esempio di sorgente è l'oscillatore interno a 8 MHz (OSC8M);

- il Generic Clock Controller (GCLK), che controlla il sistema di distribuzione del clock, composto da:

- generatori di clock (Generic Clock Generators), dei prescaler programmabili (il SAMD21 ne possiede 9, da GCLK[0] a GCLK[8]) che possono utilizzare una delle sorgenti disponibili per generare un segnale di clock; il generatore di clock 0 (GCLK[0]) viene utilizzato per generare il clock principale (GCLK_MAIN) che attraverso il Power Manager viene distribuito alla CPU e ai vari bus (AHB e APBA, APBB, APBC)

- i clock generici, in uscita dal Generic Clock Multiplexer e destinati alle periferiche del sistema; - il Power Manager (PM), che gestisce il clock destinato alla CPU e ai vari bus (il bus AHB e i vari bus APB).

Figura 1: il sistema di distribuzione del clock del SAMD21; il generatore 0 viene utilizzato per il clock principale, il multiplexer 0 è collegato ad Fase Locked Loop.

All'avvio il sistema di clock è configurato in modo da utilizzare l'oscillatore a 8 MHz come sorgente con un prescaler di 8, utilizzato dal generatore 0 per generare il clock principale (GCLK_MAIN); il clock della CPU e dei vari bus non ha prescaler.

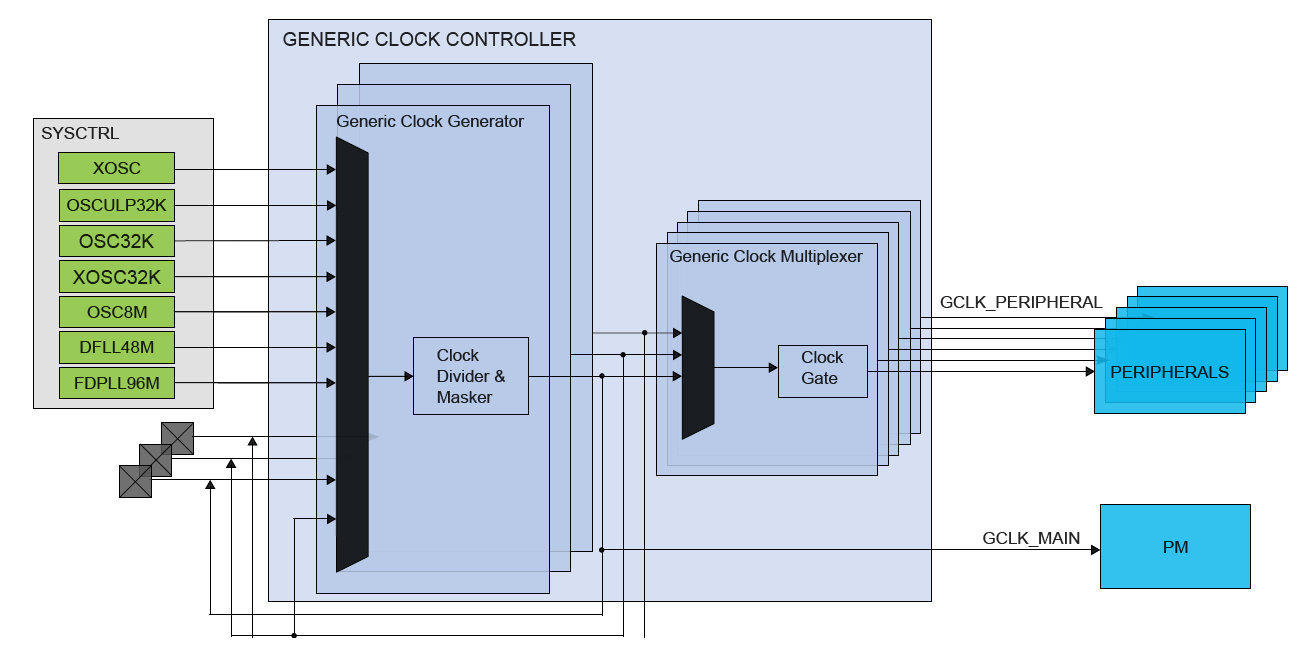

Generic Clock Controller e Power Manager

A seconda delle applicazioni le diverse periferiche possono richiedere specifiche frequenze di clock per operare correttamente. Il Generic Clock Controller, con i suoi 9 generatori (Generic Clock Generators), può generare una ampia gamma di segnali di clock in maniera flessibile. I diversi generatori possono essere configurati in modo da utilizzare una qualunque delle sorgenti disponibili; ogni sorgente può essere utilizzata come è o può essere divisa da un prescaler; ogni generatore può essere diviso; ogni generatore può essere indipendentemente abilitato o escluso; l'uscita di un generatore è utilizzata come sorgente da uno o più multiplexer (detti anche channels, ognuno associato ad una periferica del microcontrollore) che forniscono il clock alle diverse periferiche. L'uscita del generatore 0 va sempre al Power Manager come sorgente per generare il clock della CPU e dei bus; le uscite degli altri generatori vanno alle periferiche del microcontrollore (questi segnali di clock vengono detti asincroni, figura 2):

Figura 2: GCLK, il Generic Clock Controller è composto da generatori (Generic Clock Generators) e multiplexer; ogni multiplexer è associato a una periferica

Il Power Manager utilizza il generatore 0 del Generic Clock Controller per generare il segnale di clock per la CPU e i moduli collegati ai bus AHB, APBA, APBB e APBC (CLK_MAIN). Il clock principale (detto clock sincrono ) viene dapprima diviso da un prescaler a [...]

ATTENZIONE: quello che hai appena letto è solo un estratto, l'Articolo Tecnico completo è composto da ben 2824 parole ed è riservato agli ABBONATI. Con l'Abbonamento avrai anche accesso a tutti gli altri Articoli Tecnici che potrai leggere in formato PDF per un anno. ABBONATI ORA, è semplice e sicuro.

La gestione del clock non è per niente facile, ne vale un buon compromesso in termini di consumo energetico e prestazioni.