Gli ingegneri delle comunicazioni possono utilizzare MATLAB e Simulink, insieme a toolbox aggiuntivi, per sviluppare, simulare e perfezionare le loro applicazioni a livello di algoritmo. Ma implementare questi algoritmi per la prototipazione o la produzione richiede il coordinamento tra una serie di ruoli, aumentando notevolmente la complessità del progetto. In questo articolo, andremo a descrivere il processo di conversione da algoritmi Matlab e modelli Simulink in codice HDL per una FPGA.

Introduzione

La distribuzione di algoritmi su hardware FPGA consente di eseguire test e verifiche over-the-air. La generazione automatica di codice HDL direttamente dagli algoritmi e dai modelli a livello di sistema elimina la necessità per gli ingegneri di fare affidamento sui documenti delle specifiche o di progettare e scrivere manualmente il codice.

Questo documento descrive il processo di conversione diretta di algoritmi MATLAB e modelli Simulink in HDL per FPGA. Gli argomenti trattati includono:

- Modellazione algoritmica conforme allo standard 5G New Radio (NR) con MATLAB e 5G Toolbox

- Transizione da un algoritmo MATLAB ad una implementazione in Simulink

- Implementazione a virgola fissa tramite Fixed-Point Designer e conoscenza dell'hardware di destinazione

- Generazione HDL con HDL Coder e distribuzione su hardware di destinazione

Per illustrare il processo viene utilizzato l'esempio della ricerca all'interno di una cella 5G NR. 5G NR è la tecnologia di accesso radio sviluppata per la rete mobile 5G. Come per 4G (LTE), si basa sulla tecnica di trasmissione OFDM.

Implementare algoritmi in hardware

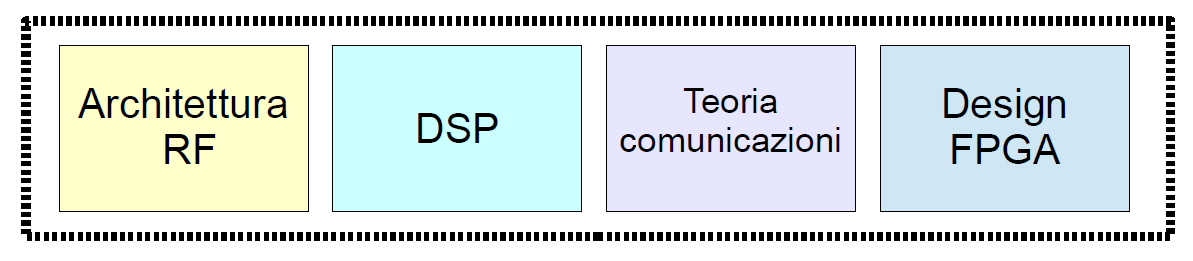

La Figura 1 mostra le competenze richieste per implementare un'applicazione per la comunicazione wireless in hardware. Gli ingegneri in genere hanno esperienza solo in una o due di queste aree, quindi i progetti spesso implicano il coordinamento tra diversi ruoli e dipartimenti.

Figura 1: Alcune delle competenze richieste per la distribuzione su hardware di un'applicazione di comunicazione wireless

La programmazione hardware di un dispositivo FPGA o ASIC è molto diversa dalla scrittura di un software che verrà compilato in una serie di istruzioni in esecuzione su un processore generico. Alcune delle differenze di alto livello sono:

- Streaming dei dati - nel software è possibile caricare dati di qualsiasi dimensione o numero di dimensioni. Tuttavia, l'hardware è un circuito che opera su un flusso di uni e zeri. Ciò significa che gli algoritmi devono essere adattati per lavorare su un flusso di dati nel tempo e includere alcune logiche per gestirlo.

- Parallelismo - i circuiti hardware possono elaborare flussi di dati in parallelo, il che velocizza l'elaborazione, ma la temporizzazione dei percorsi paralleli deve essere coordinata per garantire che i dati arrivino quando previsto.

- Tipi di dati a virgola fissa - la matematica a virgola mobile richiede in genere più operazioni e parole di lunghezza più ampia rispetto a quelle a virgola fissa. Poiché l'hardware possiede risorse limitate e si preferisce utilizzare i chip più piccoli possibili, la virgola fissa è ampiamente utilizzata nella progettazione hardware. Ma il processo di conversione da algoritmi a virgola mobile a implementazioni già pronte per hardware a virgola fissa può essere impegnativo anche per i progettisti hardware esperti.

- Interazione con software e altri dispositivi hardware - i dispositivi System-on-Chip (SoC) combinano almeno un processore con una struttura hardware FPGA. L'hardware e il software comunicano i dati avanti e indietro attraverso posizioni di memoria con indirizzi prestabiliti. L'accesso a questi registri, così come ad altra memoria esterna e all'I/O del chip, richiede una comprensione dell'architettura del dispositivo.

Il successo dell'implementazione hardware su FPGA richiede una stretta collaborazione tra ingegneri delle comunicazioni/DSP e le loro controparti che progettano l'hardware.

Il progetto

Per illustrare il flusso operativo della conversione, useremo un algoritmo per rilevare e demodulare i blocchi di sincronizzazione (SSB) del segnale 5G NR.

La sincronizzazione

Nella comunicazione cellulare, abbiamo due tipi di sincronizzazione: "sincronizzazione in downlink" e "sincronizzazione in uplink". Per questo esempio, analizzeremo solo la sincronizzazione in downlink (da stazione base verso cellulare). La sincronizzazione in downlink è il processo in cui l'UE (User Equipment), ovvero il cellulare, rileva la frontiera radio (cioè il momento esatto in cui inizia un frame radio) e la frontiera del simbolo OFDM (cioè il momento esatto in cui inizia un simbolo OFDM). Questo processo viene eseguito rilevando e analizzando il blocco SS (SSB Synchronization Signal Block). Le componenti di questo blocco sono due segnali specifici di livello fisico usati per la sincronizzazione dei frame radio: PSS, segnale di sincronizzazione primario, e SSS, segnale di sincronizzazione secondario.

Di seguito, è riportata la sequenza generale dell'accesso iniziale per la maggior parte dei sistemi cellulari con particolare attenzione al processo di sincronizzazione:

- Cerca il segnale di sincronizzazione

- Ottieni la sincronizzazione in downlink e decodifica le informazioni di sistema

- Esegui Accesso Random e ottieni sincronizzazione in uplink

- Stabilisci connessione dedicata e ottieni ID di connessione dedicato

Il modo più comune per implementare la sincronizzazione è:

- Creare un segnale predefinito (una sequenza di dati predefinita: questo segnale è chiamato segnale di sincronizzazione)

- Mettere il segnale in uno specifico simbolo OFDM in uno specifico sottoframe e trasmettere

Poiché l'UE ha già (o può derivare) tutti i dettagli del segnale di sincronizzazione predefinito, può cercare e rilevare tali informazioni dal flusso di dati che raggiunge l'UE. Poiché il segnale di sincronizzazione si trova nella posizione predefinita nel tempo, l'UE può rilevare l'esatta temporizzazione dal segnale di sincronizzazione decodificato.

I segnali di sincronizzazione primari e secondari vengono utilizzati dall'apparecchiatura utente (UE) per ottenere l'identità della cella e la temporizzazione del frame da una stazione base gNodeB (gNB).

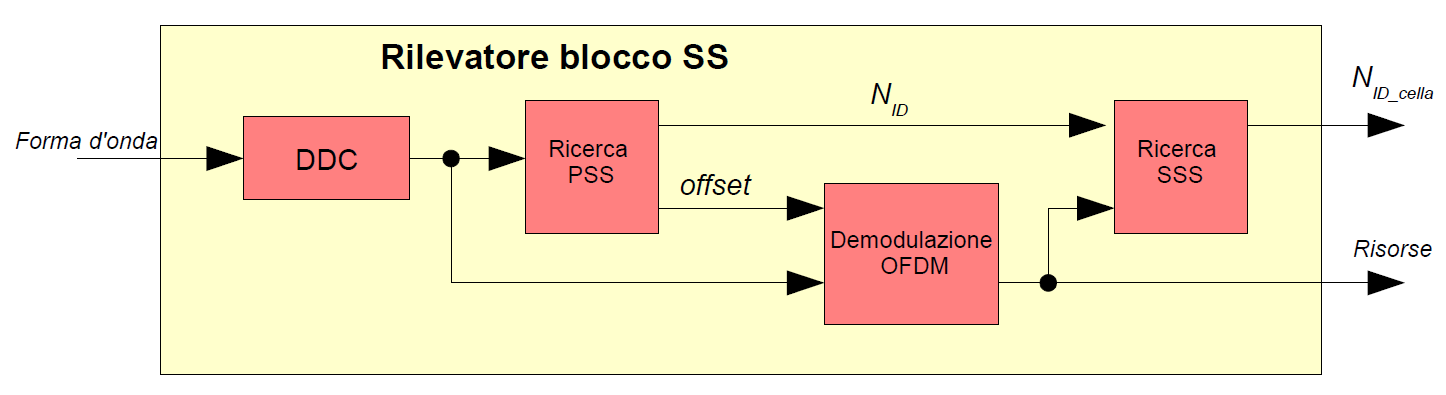

La Figura 2 mostra un diagramma a blocchi di alto livello dell'architettura del rilevatore del blocco SS. Il down-converter digitale (DDC) corregge gli offset di frequenza prima che il blocco PSS restituisca il più forte segnale di sincronizzazione primario (PSS). Il PSS più forte viene utilizzato per eseguire la demodulazione del segnale OFDM. La fase finale ricerca il segnale di sincronizzazione secondario (SSS) all'interno degli elementi di risorsa appropriati.

Flusso operativo

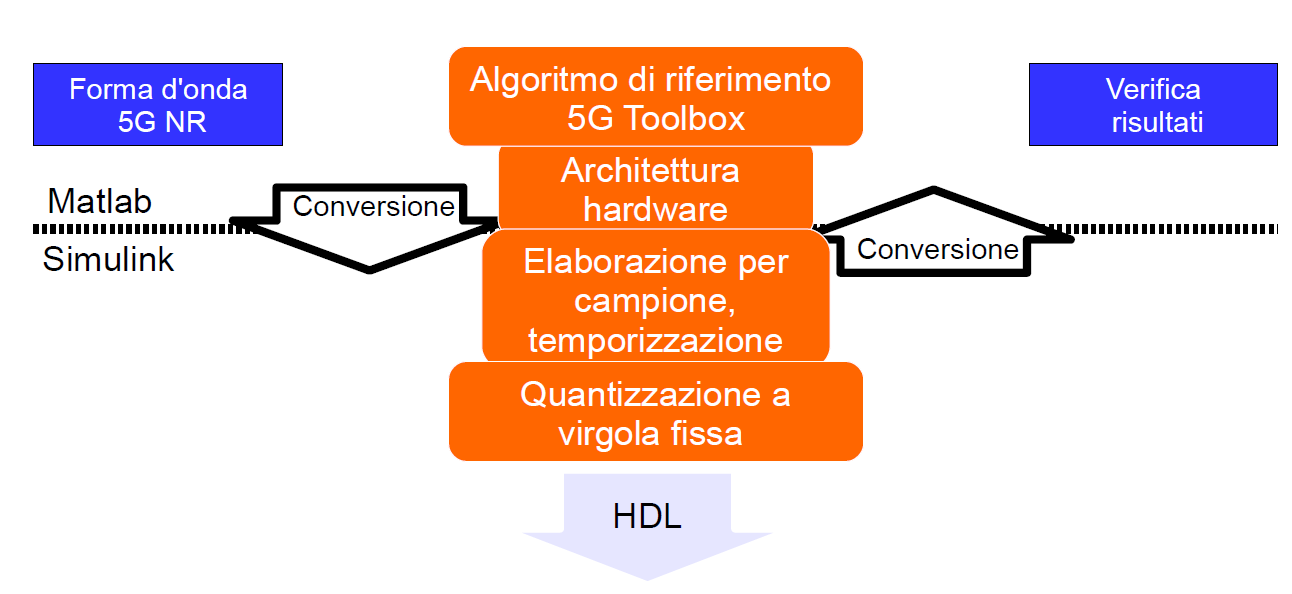

Ci sono molti percorsi che portano da un algoritmo MATLAB ad un'implementazione per FPGA. L'approccio top-down mostrato nella Figura 3 illustra il flusso operativo per distribuire un progetto wireless su FPGA.

Figura 3: Flusso operativo per il perfezionamento di un algoritmo wireless da distribuire su una FPGA

Questi passaggi non devono necessariamente seguire l'ordine mostrato nel diagramma. L'ordine dipenderà dall'applicazione e dalle preferenze. Questo approccio consente una transizione graduale a Simulink rimanendo connesso a MATLAB. Poiché Simulink ha una nozione incorporata di tempo, l'aggiunta dell'elaborazione del flusso basata su campioni è un buon passo per iniziare a perfezionare l'algoritmo in Simulink. Ciascuno dei passaggi dovrebbe essere verificato rispetto alla fase precedente o rispetto ai risultati dell'algoritmo originale. I blocchi in blu nella Figura 3 rappresentano gli elementi del banco di prova: generazione di forma d'onda in ingresso e verifica dei risultati. Descriviamo più nel dettaglio i blocchi del flusso operativo.

Algoritmo di riferimento

La progettazione delle comunicazioni wireless spesso inizia con lo sviluppo e il test di algoritmi in MATLAB. In questo progetto, l'algoritmo rappresenta sia il punto di partenza per un ulteriore perfezionamento che un modello eseguibile per verificare i perfezionamenti a valle. Lo standard wireless 5G NR è profondo e complesso, ma si può accelerare il processo di sviluppo dell'algoritmo utilizzando le funzioni predefinite, conformi allo standard, offerte da 5G Toolbox. Questi algoritmi, combinati con le funzioni wireless del Communications Toolbox, consentono di creare rapidamente un ben noto modulo di comunicazione 5G in modo da potersi concentrare sullo sviluppo dell'algoritmo personalizzato. Il design del progetto utilizza i passaggi di ricerca PSS, demodulazione OFDM e ricerca SSS mostrati nell'esempio di procedure di sincronizzazione NR fornito con 5G Toolbox.

ATTENZIONE: quello che hai appena letto è solo un estratto, l'Articolo Tecnico completo è composto da ben 2737 parole ed è riservato agli ABBONATI. Con l'Abbonamento avrai anche accesso a tutti gli altri Articoli Tecnici che potrai leggere in formato PDF per un anno. ABBONATI ORA, è semplice e sicuro.