I sistemi radar basano il loro funzionamento su un utilizzo esteso e massiccio di algoritmi di elaborazione del segnale, la cui implementazione è stata storicamente affidata ai Digital Signal Processor (DSP). Le attuali versioni di FPGA, che integrano al loro interno moduli DSP e possono processare numeri in virgola mobile, si propongono oggi come una soluzione efficiente, performante e con assorbimenti estremamente ridotti, in grado di fornire prestazioni fino a dieci volte superiori rispetto ai tradizionali DSP.

Introduzione

I più moderni sistemi radar sono in grado di implementare, sullo stesso apparato, diverse modalità di funzionamento, che tipicamente includono modi di ricerca, identificazione, rilevamento e tracciamento dei target, e sorveglianza. La maggior parte di questi sistemi radar, indipendentemente dal tipo di antenna utilizzata (a scansione comandata meccanicamente o elettronicamente), eseguono un'elaborazione digitale del segnale, in modo tale da migliorare la flessibilità del sistema nei vari modi operativi, ed utilizzando delle forme d'onda configurate a livello software.

Numerose applicazioni radar (soprattutto quelle che richiedono l'installazione a bordo di aerei militari) presentano dei requisiti stringenti in termini di spazio disponibile, assorbimento di potenza, temperatura operativa (che si riflette sul sistema di ventilazione e raffreddamento richiesto per il loro funzionamento) e peso. Questi requisiti vengono spesso riassunti in letteratura con l'acronimo anglosassone SWaP (Size, Weight, and Power). In questo contesto, la soluzione ottenuta tramite l'impiego di FPGA abilitate al calcolo in virgola mobile presenta i seguenti vantaggi:

- implementazione efficiente degli algoritmi DSP in virgola mobile;

- possibilità di eseguire gli algoritmi DSP in parallelo, grazie all'ampia disponibilità di memoria ed ampiezza di banda;

- possibilità di eseguire l'elaborazione digitale del segnale il più possibile vicino all'antenna: ciò consente di migliorare il range dinamico del sistema e ridurre le perdite;

- assorbimento di potenza contenuto e quantificabile a priori;

- l'elaborazione del segnale eseguita in virgola mobile consente di ridurre il rischio di overflow, rispetto ad un'analoga soluzione in virgola fissa.

I requisiti di elaborazione di un radar

I radar moderni sono in grado di processare un'enorme quantità di informazioni in tempo reale, senza quindi introdurre ritardi significativi nella catena di elaborazione del segnale. Ciò, inevitabilmente, impone dei requisiti molto stringenti sui dispositivi utilizzati per processare il segnale. Le tecnologie attualmente disponibili in grado di supportare questi requisiti sono le seguenti:

- Field Processor Gate Array (FPGA)

- Digital Signal Processor (DSP)

- General Purpose Graphical Processing Unit (GPU)

- processori multi core

Sebbene tutte le tecnologie elencate offrano un'elevata flessibilità e la capacità di processare il segnale a livello digitale (più precisamente, a livello software), soltanto le FPGA offrono contemporaneamente caratteristiche superiori quali: SWaP, elaborazione in vera virgola mobile ed elaborazione parallela del segnale. Un indicatore molto significativo che aiuta a scegliere il componente più adatto è rappresentato dalla misura delle prestazioni, riferita alla potenza assorbita. Questo indicatore viene normalmente espresso in GFLOP per Watt, come indicato nella seguente tabella:

| Dispositivo | GFLOP per Watt |

| CPU di fascia alta | < 3 |

| General purpose GPU | < 5 |

| DSP di fascia alta | < 8 |

| FPGA in tecnologia da 40 nm | 5 -7 |

| FPGA in tecnologia da 28 nm | 12 - 15 |

Tabella 1: efficienza computazionale delle più comuni soluzioni per l’elaborazione del segnale

Osservando questa tabella si deduce che le FPGA sono in grado di eseguire le operazioni in virgola mobile con un grado di efficienza fino a dieci volte superiore rispetto a quello di molti processori. In particolare, le FPGA realizzate in tecnologia da 28 nm sono riuscite a raddoppiare le già ottime prestazioni ottenute con la versione in tecnologia da 40 nm dello stesso componente. Le FPGA floating point forniscono la soluzione più efficiente, sia in termini di spazio che di assorbimenti, per l’implementazione di algoritmi complessi di elaborazione del segnale, e possono essere facilmente accoppiate con un processore o un DSP esterno.

Inoltre, le FPGA si dimostrano particolarmente indicate per l’esecuzione di calcoli in parallelo, soprattutto in virtù delle diverse modalità con cui possono essere eseguiti gli accessi in memoria, e dell’elevata ampiezza di banda interna. Le FPGA, infatti, contengono internamente numerosi blocchi elementari di memoria, che possono essere utilizzati in modo indipendente oppure combinati tra loro per creare blocchi di dimensione maggiore. Le più recenti versioni di FPGA contengono migliaia di DSP che operano in parallelo, diverse decine di megabyte di memoria interna, ed un’ampiezza di banda per l’input/output pari a centinaia di Gbps. Questi moduli DSP integrati includono spesso delle funzionalità, come il pre-sommatore, particolarmente utili per l’implementazione di filtri digitali, ampiamente utilizzati nelle applicazioni radar (come ad esempio i filtri FIR utilizzati nella compressione degli impulsi). Un’altra caratteristica fondamentale dei sistemi radar è il range dinamico: la potenza del segnale trasmesso (lungo il tragitto percorso per raggiungere il target, essere riflessa e tornare verso l’antenna), decresce con la quarta potenza della distanza (range). La capacità di rilevare target anche molto distanti, senza essere “accecati” da ritorni di segnale ad elevata intensità, richiede una mole di calcoli ed una capacità di elaborazione non indifferente, che può essere ulteriormente migliorata dalla possibilità di utilizzare istruzioni sia a singola che a doppia precisione. Soltanto un numero esiguo di DSP e processori multi core presenta questa caratteristica, oggi parte integrante delle FPGA con supporto in virgola mobile.

L'architettura di un radar

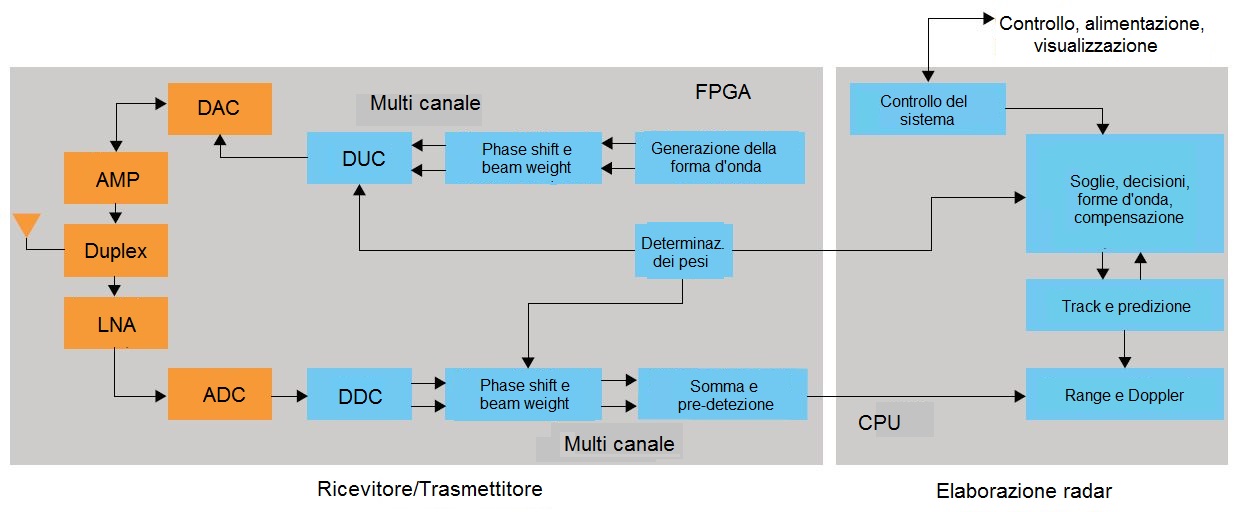

L'architettura tipica di un radar moderno è visibile in Figura 1. Il blocco sulla sinistra, in cui possono essere efficacemente utilizzate delle FPGA, comprende il trasmettitore (parte superiore dell'immagine), il ricevitore (parte inferiore dell'immagine) e l'interfaccia verso l'antenna (visibile sul lato sinistro). La trasmissione include la generazione delle forme d'onda, il beamforming e la conversione digitale della frequenza (indicata con il termine up conversion, in quanto la frequenza degli impulsi che compongono la forma d'onda viene traslata dalla banda base fino a raggiungere la frequenza di trasmissione, che può essere anche superiore a qualche GHz). Dopo essere transitato attraverso un DAC ed un amplificatore di potenza, il segnale raggiunge il duplex, un componente che funge da commutatore della sorgente del segnale: in trasmissione lascia passare il segnale da irradiare verso l'antenna (chiudendo il canale di ricezione), mentre nella fase di "ascolto" esegue esattamente l'operazione opposta, abilitando il canale di ricezione e disabilitando quello di trasmissione. La ricezione include una prima elaborazione a livello analogico (rappresentata in Figura 1 dall'amplificatore a basso rumore, LNA, e dall'ADC), la conversione di frequenza (in questo caso si tratta di una down conversion) ed il beamforming. Queste operazioni vengono normalmente eseguite su più canali.

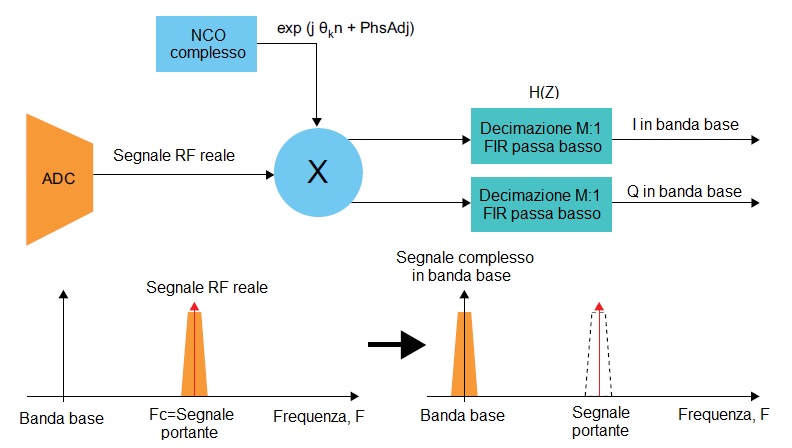

In Figura 2 possiamo osservare un tipico sistema di down conversion, il cui compito è quello di traslare ad un valore inferiore (la "banda base") la frequenza del segnale in ingresso. Quest'ultimo viene miscelato con il segnale prodotto da un oscillatore locale di tipo NCO (Numerically Controlled Oscillator), creando di fatto un'uscita eterodina che viene successivamente filtrata tramite un filtro FIR passa-basso e sotto campionata tramite decimazione. All'uscita si ottiene così un segnale in banda base pronto per essere processato dai successivi stadi di elaborazione del radar (si osservi il diagramma nella parte inferiore di Figura 2, dove è ben evidenziato il risultato prodotto dalla down conversion). Il blocco sulla destra di Figura 1 contiene invece il data processor, in cui vengono eseguiti opportuni algoritmi software che, operando esclusivamente su segnali in forma numerica, hanno il compito di rilevare e determinare la posizione dei target, tracciare e predire la loro traiettoria e velocità, visualizzare le informazioni rilevanti su un display ed eventualmente interfacciarsi con altri dispositivi esterni. Vediamo ora più in dettaglio alcuni tipi di elaborazione numerica eseguiti all'interno di un radar, particolarmente significativi per un potenziale utilizzo delle FPGA.

Il beamforming

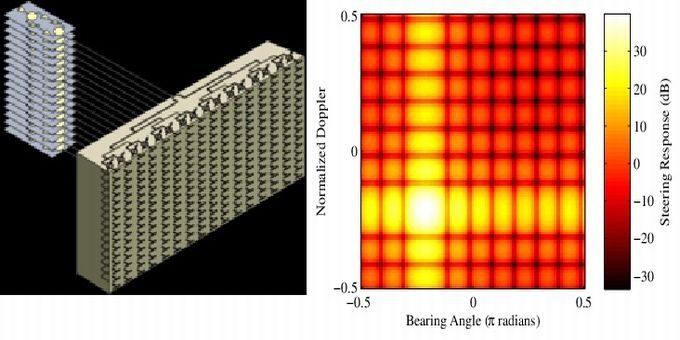

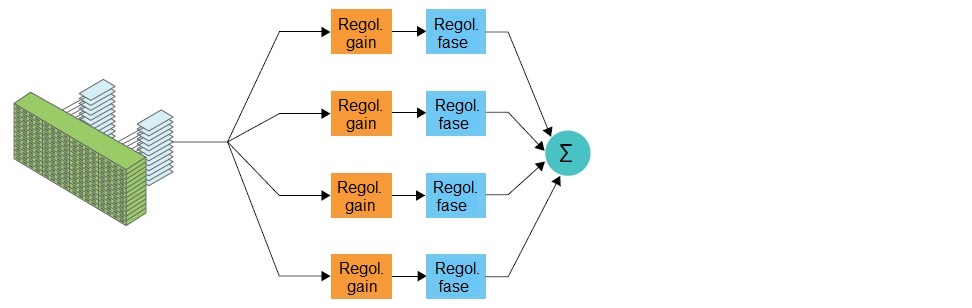

Il beamforming è una tecnica digitale con cui il trasmettitore ed il ricevitore radar vengono focalizzati in una precisa direzione. Quest'ultima viene normalmente riferita alle coordinate polari: la coordinata lungo l'asse orizzontale viene detta azimuth, quella lungo l'asse verticale elevation, e la distanza range. Il beamforming è in sostanza un filtraggio eseguito nella dimensione dello spazio con lo scopo di ottenere un'elevata sensibilità in una precisa direzione. Durante la ricezione del segnale radar, ad esempio, il beamforming permette di determinare con precisione l'angolo di arrivo del segnale riflesso (viceversa, in trasmissione, è possibile orientare il fascio in una specifica direzione). Questo aspetto si dimostra particolarmente utile con le antenne "phased array", composte da elementi multipli, e con le "antenna array", composte da più antenne allineate lungo gli assi orizzontale e verticale (Figura 3). Ogni elemento dell'antenna è dotato di un proprio modulo di trasmissione e ricezione, e può pertanto modificare sia l'ampiezza che la fase del segnale trasmesso o ricevuto. Queste variazioni, soprattutto della fase, permettono di direzionare il fascio radar (beam) sia in azimuth che in elevation. Soltanto quando il segnale ricevuto arriva in fase su tutti gli elementi dell'antenna, si otterrà la massima intensità di segnale.

Quando un singolo elemento dell'antenna (o dell'array di antenne) riceve un segnale, questo è normalmente interessato da fenomeni di interferenza e rumore prodotti da target non desiderati e dall'ambiente circostante (terreno, agenti atmosferici, etc.). Per compensare questi effetti, i sistemi radar includono sia un filtraggio spaziale che uno temporale. Il primo si focalizza sulla determinazione della distanza e della direzione (angolo) del target, mentre il secondo si focalizza sulla frequenza del segnale (opera quindi nel dominio del tempo). Attraverso il beamforming, vengono regolati sia il guadagno che la fase associati ad ogni elemento dell'antenna in modo tale da allineare lungo una direzione i ritardi del segnale associato ad ogni elemento. Il contributo di segnale apportato da ogni elemento dell'antenna può così sommarsi nella regione di interesse ed annullarsi in corrispondenza delle direzioni non desiderate, come mostrato in Figura 4.

ATTENZIONE: quello che hai appena letto è solo un estratto, l'Articolo Tecnico completo è composto da ben 2972 parole ed è riservato agli ABBONATI. Con l'Abbonamento avrai anche accesso a tutti gli altri Articoli Tecnici che potrai leggere in formato PDF per un anno. ABBONATI ORA, è semplice e sicuro.

Ottima trattazione!

Indubbiamente negli ultimi anni l’introduzione delle FPGA sta consentendo l’ottimizzazione di una vasta gamma di applicazioni in cui si richiedono elevate potenze di calcolo.

Nella fattispecie, le FPGA consentono la parallelizzazione dei processi di calcolo, abbassando drasticamente i tempi di calcolo a vantaggio delle prestazioni.

Inoltre l’avanzatissima tecnologia di realizzazione delle FPGA le rende sempre più piccole e dai consumi sempre più bassi.

Altra nota positiva, gli ambiente di sviluppo sono sempre più performanti e consentono di velocizzare sempre di più il flusso di progettazione, configurazione e testing .