Nonostante l’introduzione della nuova tecnologia DDR4, le memorie DDR3 rappresentano oggi un buon compromesso tra velocità, efficienza e costo, fattori che ne determinano il largo impiego soprattutto nei sistemi embedded di fascia alta.

Introduzione

Le memorie SDRAM (Synchronous Dynamic Random Access Memory) hanno subito una continua evoluzione nel corso degli anni, una necessità per rimanere al passo con le sempre crescenti esigenze dei computer e dei sistemi embedded. DDR3 SDRAM rappresenta la terza generazione della famiglia di memorie DDR SDRAM e offre miglioramenti in termini di maggiore frequenza, maggiore capacità e migliore qualità del segnale grazie all’adozione della tecnologia ODT (On Die Termination), in cui la resistenza di terminazione (necessaria per l’accoppiamento di impedenza sulle linee di trasmissione) non è posta sul PCB ma è all’interno del chip. Introdotto dal JEDEC nel 2007, lo standard per le memorie DDR3 SDRAM ha comportato un drastico miglioramento delle prestazioni accompagnato da un altrettanto significativa riduzione degli assorbimenti. La specifica DDR3 supporta velocità comprese tra 800 e 1600 Mbit/s e capacità sino a 8 Gbit, entrambe quasi raddoppiate rispetto alla precedente tecnologia DDR2. Anche la tensione di I/O è stata ridotta, passando dal valore operativo di 1,8V delle DDR2 a un più efficiente 1,5V, con una riduzione della potenza assorbita fino al 30%. Lo standard DDR3 non si limita soltanto a incrementare la velocità e ridurre i consumi, ma consente anche di semplificare la progettazione del PCB, ridurre il rumore e migliorare le tempistiche sui segnali. Le memorie DDR3 sono inoltre composte da un maggior numero di banchi interni di tipo DIMM (Dual In line Memory Module): 8, al posto dei 4 impiegati nelle memorie DDR2.

Topologie Fly By e T branch

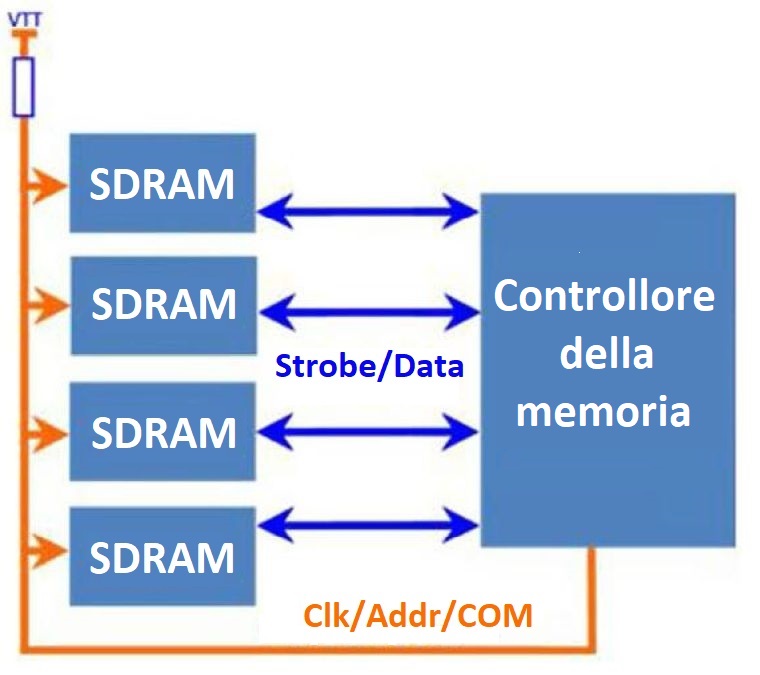

Poichè le memorie DDR3 sono state progettate per operare a frequenze maggiori, l’integrità dei segnali che viaggiano attraverso i moduli di memoria assume un’importanza fondamentale. A questo proposito, JEDEC ha introdotto la topologia di tipo Fly By, contrapposta a quella di tipo T branch impiegata nelle memorie DDR2. Come visibile in Figura 1, nella topologia Fly By l’indirizzo e le linee di controllo (clock differenziale e comandi) sono posti su un unico cammino che collega un modulo all’altro (una sorta di daisy chain).

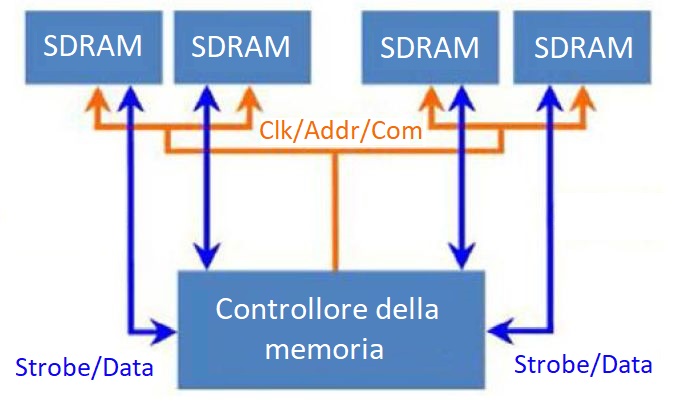

In Figura 2 è invece rappresentata la topologia T branch, in cui i collegamenti avvengono in parallelo su tutti i moduli.

Con il Fly By i segnali sono inoltrati ai moduli di memoria in modo lineare, sino a raggiungere l’estremità della catena dove è presente la terminazione del bus. In questo modo, rispetto al caso T branch, si riducono sia il numero che la lunghezza dei collegamenti elettrici. Lo svantaggio è che viene introdotto un ritardo (noto con il termine flight time skew) tra i segnali di clock e quelli dati e strobe. Per compensare questo fenomeno il controller della memoria deve implementare una funzionalità di compensazione dei ritardi, sia in lettura che in scrittura, nota anche con il termine read/write leveling. Se si devono progettare sistemi che impiegano moduli di memoria DDR3, occorre necessariamente supportare l’architettura Fly By. Viceversa, se si utilizzano memorie DDR3 non organizzate su più moduli (architettura point to point) si può scegliere tra la topologia Fly By oppure T branch. In Figura 3 possiamo osservare un confronto tra gli schemi di collegamento T branch (DDR2, a sinistra nell’immagine) e Fly By (DDR3, a destra nell’immagine), dove DQS indica il segnale di strobe. Da questo schema si evince come i ritardi introdotti dal Fly By siano imputabili proprio alla presenza del daisy chain tra i moduli. [...]

ATTENZIONE: quello che hai appena letto è solo un estratto, l'Articolo Tecnico completo è composto da ben 2711 parole ed è riservato agli ABBONATI. Con l'Abbonamento avrai anche accesso a tutti gli altri Articoli Tecnici che potrai leggere in formato PDF per un anno. ABBONATI ORA, è semplice e sicuro.

Poichè nell’articolo di parla di linee di trasmissione e microstriscia, mi permetto di mettere il link ad un mio vecchio articolo sulla progettazione di antenne in microstriscia:

https://it.emcelettronica.com/scopriamo-come-sono-realizzate-le-antenne-in-microstriscia-degli-smartphone

Ottima segnalazione, Andrea, grazie mille.

Quando la velocità di trasmissione è alta, anche un capello fa la differenza. Direi che si tratta di una vera e propria PCB ART.

Credo che uno degli aspetti più interessanti sia la possibilità di ridurre i consumi, cosa richiesta soprattutto nei sistemi embedded.

Articolo davvero ben fatto e chiaro. Grazie

Grazie a te, Andrea, per i complimenti. Il tema è più che mai attuale e riguarda diverse categorie di dispositivi elettronici in cui sono presenti segnali digitali ad elevata frequenza.