In questo articolo continuiamo l'analisi della stringa acquisita dal SAD iniziata negli articoli precedenti. In questo caso ci proponiamo di memorizzazione in RAM i risultati finali ottenuti a posteriori dell’elaborazione effettuata

L’ultima operazione eseguita dal nostro sistema di acquisizione ed elaborazione, consiste nel salvataggio delle stringhe in uscita dall’addizionatore, all’interno della RAM che si trova sulla scheda XS-40. Ciò consentirà ad un prossimo sviluppo del sistema di poter elaborare in maniera semplice i dati acquisiti. Tenendo conto che tutti i blocchi funzionali descritti in precedenza sono scritti in VHDL, risulterà estremamente facile estendere queste operazioni semplici con operazioni più complicate o che richiedono un maggior numero di bit da elaborare.

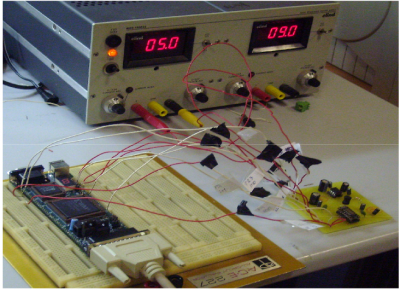

Per quanto riguarda l’operazione di scrittura in RAM dei dati, è stata realizzata un’opportuna interfaccia che sfrutti al massimo il Bus Dati e il Bus indirizzi. Per poter comprendere il funzionamento dell’interfaccia realizzata è necessario analizzare con dettaglio maggiore lo schema della RAM presente sulla scheda XS-40 : l'ALLIANCE AS7C1024 è una RAM di tipo statico da 32 Kbyte.

Come si nota dalla Figura 4.11 la RAM è dotata di 15 pin dedicati all’indirizzamento della memoria e 8 pin per la scrittura dei dati. Ciò significa che ogni singolo indirizzo di memoria può contenere 8 bit cioè 1 byte. Siccome la stringa in uscita dall’addizionatore è di 12bit, si presenta già una prima difficoltà da affrontare: come salvare i dati nella RAM?.

Una volta risposto a questa domanda, è possibile passare ad una seconda scelta da fare: quella relativa a quanti indirizzi utilizzare, cioè quanta area di memoria occupare. Per il sistema realizzato in questa tesi, è stata fatta la scelta di utilizzare tutti e 8 i bit a disposizione, e quindi rappresentare ogni singolo pixel in due indirizzi di memoria consecutivi. Ciò comporta che i 12 bit della stringa in uscita al sommatore saranno scritti in 2 byte:

-il primo composto dalla concatenazione di una stringa di 4 zeri seguita dai 4 bit più significativi dei 12.

-Il secondo è costituito dagli 8 bit restanti. Per effettuare queste operazioni è stato implementato lo schema rappresentato di seguito:

Il blocco DEMUX12x8 in figura, ha come ingressi il CLKADC e la stringa S[11:0] rappresentate il risultato della sottrazione. Il suo compito è quello di alternare in ingresso all’interfaccia della RAM una volta un byte composto da 4 zeri e i 4 bit più significativi di S[11:0], e la volta successiva un byte composto dagli 8 bit meno significativi della stringa S[11:0].L’uscita si alterna in maniera sincrona con il fronte di salita del CLKADC.

Il blocco RAM1 insieme ai segnali WE, CE, OE e ai bus A[14:0] e D[7:0] mostrati nelle prossime figure, rappresentano la vera e propria interfaccia con la RAM. Questo blocco ha in ingresso tre segnali:

-CLKADC:E’ il segnale di sincronismo per le operazioni interne.

-CONV: Abilita il trasferimento dei dati in ingresso.

-DIN[7:0]:Sono i dati da scrivere nella RAM.

La funzione di questo blocco RAM1 è quella di caricare i dati in uscita dal demux sul registro dati e indirizzarli in memoria in maniera opportuna. Per verificare il funzionamento di quest’interfaccia, effettuiamo una simulazione funzionale visualizzando l’andamento temporale dei principali segnali d’interesse.

Dalla prima figura possiamo notare che il segnale OE relativo all’Output Enable (attivo basso), è stato connesso all’alimentazione in modo tale che il bus dati sia utilizzato solo per la scrittura in Ram. I segnali CE e WE (attivi bassi), rispettivamente Chip Enable e Write Enable, sono stati connessi entrambi al segnale CLKCMOS in modo tale da abilitare la Ram in scrittura, solo quando la sottrazione è stata riportata in uscita.

E’ possibile notare tale aspetto guardando l'andamento dei segnali mostrato, in cui è anche possibile verificare che della somma ottenuta “757”(in valori esadecimale), viene caricato in ingresso all’interfaccia RAM1(DIN7), prima il byte corrispondente al valore ”07” e poi il byte “57”. Questi due byte saranno allocati in memoria all’indirizzo indicato dal bus A14 in corrispondenza del loro valore(000D e 000F).

Come si può notare questi 2 byte saranno in realtà memorizzati più di una volta occupando area di memoria inutilmente. Infatti, uno dei primi passi da compiere per uno sviluppo futuro di questo sistema, è quello di rendere il più efficiente possibile l’algoritmo VHDL dell’interfaccia RAM1. Per poter leggere i dati scritti in RAM è necessario utilizzare il tool GXSLOAD inserendo un indirizzo iniziale e finale da cui estrarre i dati. Ovviamente l’indirizzo finale sarà noto a priori dato che lo si può calcolare moltiplicando il numero di bit in uscita dal convertitore A/D(12 bit) per il numero totale di pixel che si vuole acquisire(128 pixel nel nostro caso). All’interno del tool GXSLOAD è anche possibile scegliere un opportuno formato del file estratto dalla RAM, per una comprensione migliore dei dati acquisiti.

Articoli precedenti correlati

https://it.emcelettronica.com/realizzazione-dei-segnali-di-controllo-sistema-di-acquisizione-dati

https://it.emcelettronica.com/seconda-parte-del-sistema-di-acquisizione-dati

Molto interessante e molto ben scritto.

L’argomento è piuttosto complesso da trattare in un blog!

Che applicazione hanno questi sensori?

Ciro.

Ciao Ciro,

guarda il sensore utilizzato in questa tesi è di vecchia data..ed erano i primi sensori utilizzati ad esempio nel riconoscimento dei codici a barre..

Oggi come ben sappiamo oltre a quelli lineari esistono quelli a matrice di pixel che comunemente utilizziamo nelle nostre fotocamere…ovviamente per questa tesi lo scopo era quello di piazzare un sensore per riconoscere i segnali provenienti da diverse fibre ottiche..

Immaginati un pettine di fibre disposte su un “array” monodimensionale.. lo spot luminoso di queste fibre cambia ad esempio a seconda della pressione meccanica esercitata sul rivestimento della fibra stessa.. quindi si voleva codificare e rilevare questa pressione in modo tale da dare al robot anche una sorta di “tatto” digitale 🙂

In particolare se vuoi vedere il progetto completo dovresti ripescare i primi articoli della tesi in cui l’ho citato : http://www.dexmart.eu/