Multi-Core Debug Solution, ovvero MCDS. La struttura di questa soluzione è quella di un edificio di blocchi IP configurabili che forniscono tracce di compressione, tempi di stampa, e cross-target triggering complesso, e consente inoltre la misurazione di molteplici misuratori di performance.

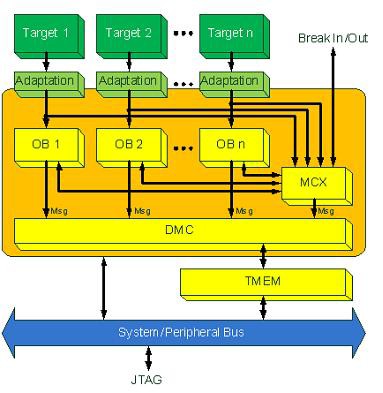

L'immagine mostra il sistema MCDS consistente in un kernel MCDS e una TMEM, una trace memory on-chip. Nell'esempio, la comunicazione tra l'ambiente di debug on-chip e il tool di debug avviene via JTAG. È anche possibile utilizzare altre interfacce come la Nexus.

Howto Debug un SoC multi-core

Ciascun obiettivo di debug (core del processore, bus) è connesso all'MCDS tramite un blocco logico di adattamento. Il design di questo tipo di blocchi, cioè, può essere adattato a un target specifico. Ogni blocco associa l'interfaccia utente del target a una interfaccia generica standardizzata che è usata dall'MCDS. Inoltre, sincronizza i segnali provenienti dal target al clock dell'MCDS nel caso in cui questi sono differenti.

L'architettura del kernel MCDS dipende dal numero e dal tipo degli obiettivi di debug e consiste di più blocchi di osservazione (OB), di un Multi Core Cross Connect (MCX) e di un Memory Controller di debug (DMC). L'MCX è connesso a tutti gli OB e al DMC. Questo è responsabile della distribuzione dei cross-trigger programmabili e fornisce il tempo di stampa per tutti i messaggi. In questo modo, tutti i messaggi provenienti dalle differenti sorgenti sono messi in coda e stampati in ordine cronologico. Un MCX aggiuntivo fornisce un numero di contatori che possono essere usati per il conteggio degli eventi e per attivare una precisa azione dopo che un evento si è presentato per un certo numero di volte o dopo che è trascorso un certo lasso di tempo. Nel complesso, l'MCX da la possibilità di osservare un sistema con processori multi-core, lì dove deve essere valutata l'interazione tra condizioni complesse per determinare e gestire ogni singolo evento.

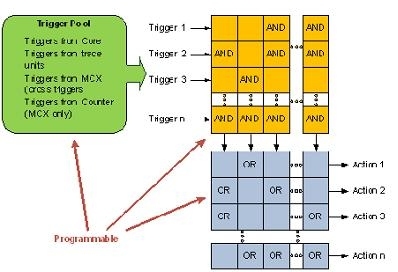

Ogni segnale da monitorare è collegato a un blocco OB dedicato. All'interno di questo blocco ha luogo la generazione dei messaggi. Ogni OB può contenere più Trace Unit di differenti tipi. Il numero e i tipi di queste dipende dal target di debug e dalle informazioni che ne derivano. Per dare l'avvio e lo stop alla registrazione delle tracce, alla generazione dei cross-trigger e al controllo degli obiettivi, è implementata una logica di trace qualification come mostrato in figura:

La matrice AND/OR applicata a tutti i blocchi di trace qualification è contenuta negli OB e nell'MCX. I valori di trigger in ingresso possono essere valutati direttamente o negati. Può anche essere scelta la soglia o livello di sensibilità.

Dal punto di vista del debug, l'MCDS è uno strumento che deve essere programmato per un certo tipo di debug scrivendo le informazioni di configurazione all'interno di una serie di registri di memoria opportunamente mappati. Questi registri controllano le matrici AND/OR di ogni blocco OB, DMC e di un certo numero di sorgenti di trigger (per esempio dei comparatori indirizzi/dati).

Leggi anche: Howto Debug un SoC multi-core 1

Re-post del: 01-12-2008