Nei prossimi articoli sarà presentato lo schema di controllo ed elaborazione da implementare attraverso l’FPGA, e realizzato mediante il software Project Manager. Verranno analizzate nel dettaglio tutte le operazioni realizzate e che compongono le varie fasi di progetto che elenchiamo di seguito :

1. Generazione dei segnali di controllo per il sensore ELIS-1024 e il convertitore A/D ADS7818.

2. Acquisizione dei bit generati dal convertitore A/D.

3. Elaborazione della stringa acquisita.

4. Conversione Parallelo/Seriale.

5. Memorizzazione del risultato nella RAM della scheda XS-40.

Siccome la maggior parte del progetto è stato realizzato in codice VHDL, si è ritenuto opportuno includere a fine trattazione un appendice in cui sono stati riportati i codici VHDL realizzati.

1)Generazione dei segnali di controllo:

La prima fase della realizzazione del sistema di acquisizione ed elaborazione oggetto di questa tesi, è quella di realizzare sulla scheda XS40 gli opportuni segnali di controllo da applicare al sensore ELIS-1024. L’obiettivo è ottenere dei segnali che seguano la tempificazione standard del sensore in modalità DPR (Dinamic Pixel Reset)riportata nella figura sottostante:

.png)

I segnali da generare sono :

-Clock (CLK in seguito rinominato come CLKCMOS);

-Shutter (SHT);

-Reset (RST);

-Data;

Inoltre, bisogna considerare anche i segnali M1 e M0 che determinano la risoluzione del sensore nonché la dimensione effettiva del singolo pixel e del segnale Reset Mode (RM), che indica la modalità di funzionamento del sensore. Come vedremo in seguito questi segnali sono stati ottenuti mediante opportuni blocchi elaborati in VHDL e connessi al PCB tramite i pin della scheda XS-40.

1.1)Generazione del Clock

La prima operazione da fare è quella di settare il clock dell’oscillatore (montato sulla scheda XS40) ad un opportuna frequenza di lavoro tramite il tool GSXSETCLK. Infatti, sarà proprio l’oscillatore a generare il clock principale che utilizzeremo per ricavare tutti gli altri segnali di controllo. La scelta di questo clock non è casuale, ma deve tenere in conto i seguenti fattori :

1. Ogni pixel viene integrato sul fronte di salita del CLKCMOS.

2. Il valore di tensione del pixel viene riportato in uscita al sensore durante l’intera durata di un periodo del CLKCMOS.

3. Tutti i pixel vengono integrati tra due impulsi del segnale Data che delimitano il cosiddetto t_FRAME.

4. L’A/D effettua una conversione che restituisce in maniera seriale una stringa di 12 bit in uscita (dall’MSB all’ LSB).

Quindi, il segnale di clock principale, che chiameremo d’ora in poi CLKADC, deve avere un periodo T_CLKADC pari a:

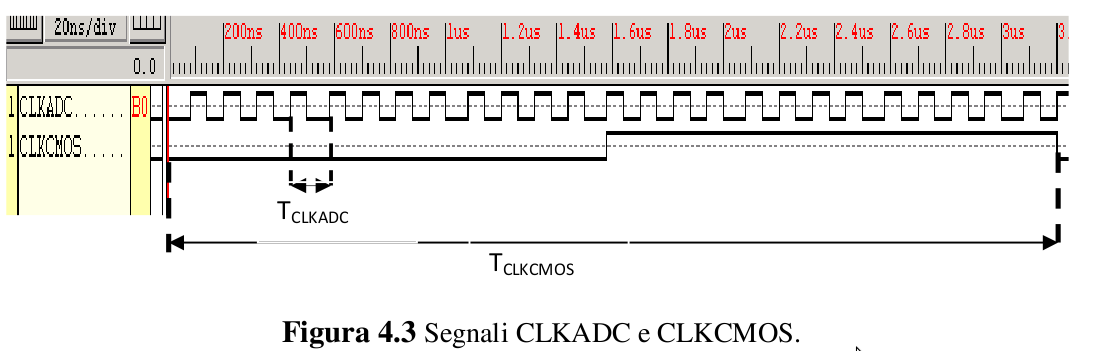

T_CLKADC=(2*T_CLKCMOS)/12

dove con T_CLKCMOS si è indicato il periodo del segnale CLKCMOS. Questa relazione nasce dal fatto che il valore di tensione di ogni pixel viene mantenuto costante per un tempo pari al T_CLKCMOS, ed in questo tempo il convertitore deve essere pilotato da un clock che permette di restituire in uscita all’ADC, i 12 bit della stringa relativa alla conversione.

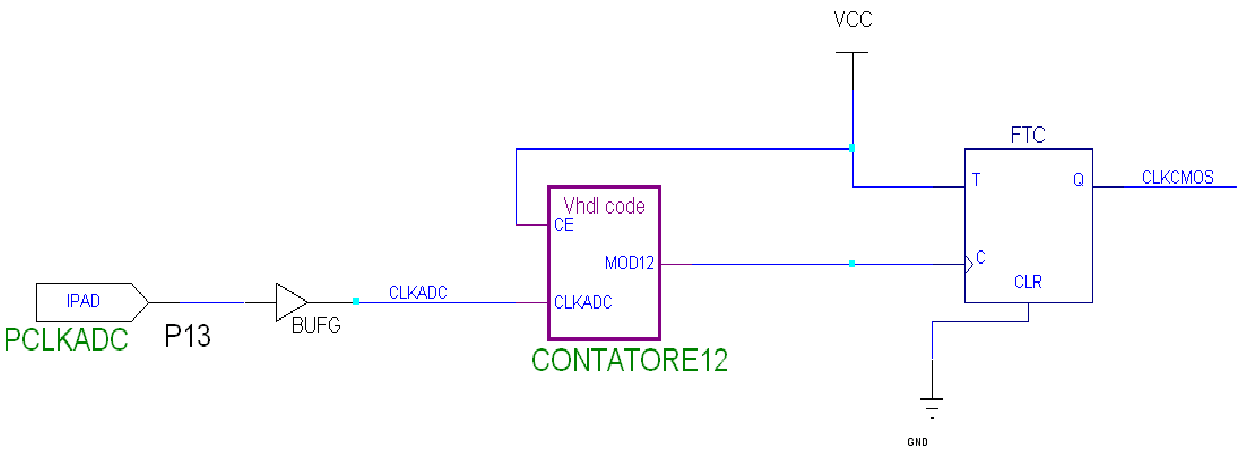

Per realizzare il segnale di CLKCMOS è stato implementato in VHDL un contatore modulo 12 seguito da un Flip-Flop T (vedi figura successiva).

Quindi, la frequenza scelta per l’oscillatore è quella a cui lavorerà l’ADC. Per tale componente è stata scelta una frequenza di 2 MHz in modo da rispettare le specifiche di progetto. Questa frequenza non è molto elevata, dato che la massima frequenza di lavoro dell’ADS7818 è di 8 MHz, ma ciò si giustifica col fatto che non è stato possibile apprezzare un’uscita dell’ADC significativa a frequenze superiori, in quanto il rumore prevaleva sul segnale utile.

Ad una frequenza di 2 MHz dell’ADC corrisponde una frequenza del segnale di clock del CMOS pari a 333.3 kHz (T_CLKCMOS pari a 3.2 us). Di seguito invece si riporta l’andamento temporale ricavato da una simulazione funzionale dello schematico mostrato nella figura precedente in cui si può verificare la correttezza dei segnali generati, che sarà poi successivamente confermata da un’analisi all’oscilloscopio degli stessi(nei prossimi articoli).

1.2 Generazione del segnale Data

Dalla figura inerente i segnali di controllo dell'ELIS-1024, è possibile notare che il segnale Data delimita la fine di un frame, ossia indica l’istante di tempo in cui è stato effettuata l’operazione di Read-Out per tutti i pixel. La risoluzione dell’ELIS-1024 è stata scelta pari a 128 pixel in modo da avere la dimensione più grande possibile del singolo pixel(ricordiamo che la max risoluzione è 1024 pixel).

Questo perché si vuole che lo spot di luce emanato da una fibra ottica colpisca il minor numero di pixel possibile, in modo da massimizzare il numero di fibre controllabili dal sensore. Siccome lo spot size dipende dalla distanza a cui si pone la fibra, assumendo una distanza pari a circa 1mm si nota che lo spot size è dell’ordine dei millimetri.Infatti, è stato necessario prevedere l’uso di opportune lenti ottiche per collimare lo spot di luce e diminuire la larghezza di tale spot fino all’ordine delle centinaia di μm.

Affinché la dimensione del singolo pixel sia superiore allo spot size ,è stato necessario impostare la risoluzione del sensore a 128 pixel ottenendo una dimensione del pixel pari a 64.4μm x 125μm. Quindi, siccome l’operazione di Read Out viene eseguita ad ogni colpo di clock ,il segnale di data dovrà essere un impulso generato ogni 128 colpi di clock(CLKCMOS) per cui risulta che :

T_DATA = 128*T_CLKCMOS = 2,6kHz

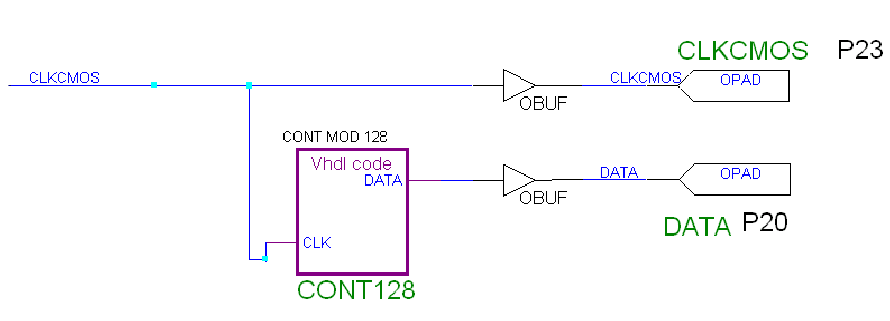

Per ottenere questo segnale è stato realizzato in VHDL un contatore modulo 128 in grado di contare i fronti di salita del CLKCMOS, mostrato nella prossima figura:

In seguito sarà mostrata la coerenza di questi segnali con quanto appena esposto, mostrando i risultati di misure effettuate mediante l’utilizzo di un oscilloscopio digitale, ma prima seguirà un articolo in cui si continuerà la progettazione dei restanti segnali di controllo.

Articoli correlati:

https://it.emcelettronica.com/convertitore-ad-ads7818-burr-brown

https://it.emcelettronica.com/realizzazione-del-pcb-mediante-software-target-3001-v11-ligth

https://it.emcelettronica.com/analisi-dei-segnali-di-controllo-del-sensore-elis-1024