Synplify DSP è un tool che costituisce un punto di incontro tra gli applicativi usati dai progettisti DSP ed i motori di sintesi RTL. Ecco in dettaglio tutte le funzionalità di questo strumento di sintesi automatica.

La crescente capacità logica dei dispositivi a semiconduttore – FPGA ed ASIC – ne ha determinato una rapida diffusione nell’ambito delle applicazioni di Digital Signal Processing. Grazie alla disponibilità di funzioni aritmetiche embedded ed alla naturale predisposizione per la realizzazione di architetture parallele, questi dispositivi consentono di raggiungere elevate capacità di calcolo (dell’ordine di centinaia di MIPS), impensabili con processori DSP classici ‘programmabili’ via software. Nel settore, tuttavia, si era creato negli ultimi anni un vero e proprio gap di produttività legato all’assenza di un ambiente che facesse da tramite tra gli applicativi (tipicamente Matlab Simulink) utilizzati dai progettisti DSP ed i motori di sintesi RTL. Tale gap sembra oggi ridursi grazie alla disponibilità di soluzioni automatiche; tra queste, una delle più interessanti è sicuramente rappresentata da Synplify DSP distribuito da Synplicity. Lo scenario, in effetti, è del tutto simile alla situazione cui ci si era trovati di fronte negli anni ’90 con l’introduzione dei dispositivi FPGA in sostituzione delle classiche PLD di limitata capacità logica. La risposta in quel caso fu rappresentata dallo sviluppo dei linguaggi di programmazione HDL in sostituzione dei CAD gate-level. La stessa esigenza, ovvero la necessità di un modello di progettazione di più alto livello rispetto alla descrizione RTL, si avverte oggi, in particolar modo nel campo della applicazioni DSP, nel momento in cui le logiche programmabili sono divenute complesse piattaforme per applicazioni system-on-chip.

LE PRIME ESPERIENZE

In ambito DSP, in effetti, sono stati seguiti fino ad oggi diversi approccie con alterne fortune per la implementazione in logiche programmabili dei modelli comportamentali sviluppati in Matlab Simulink. Un primo stile prevedeva la traduzione manuale degli M-file in linguaggio HDL o, più recentemente, C/C++. In questo caso, tuttavia, il problema principale risiede nell’assenza di costrutti sintetizzabili per le funzioni aritmetiche di alto livello disponibili in Matlab; si pensi ad esempio al calcolo della trasformata FFT di un segnale, operazione rappresentata in Matlab da una semplice istruzione del tipo y = fft(x) ma per la quale non esiste un corrispettivo supportato dai motori di sintesi tradizionali. Come conseguenza di questo, il codice originario deve essere profondamente modificato; il processo non può ritenersi immune da errori e non è possibile ricavare una stima delle caratteristiche fisiche del progetto (in termini, ad esempio, di risorse logiche occupate, frequenza di funzionamento o dissipazione di potenza) prima che tutti i blocchi funzionali siano stati tradotti. Con la diffusione dei metodi di design-reuse, il flusso descritto è stato sostituito da una metodologia di progetto basato sull’utilizzo di core di proprietà intellettuale per le principali funzioni DSP, quali trasformate di segnale o filtri FIR. In questo caso sono resi disponibili ai progettisti DSP modelli Matlab equivalenti delle funzionalità dei core per consentire la simulazione a livello sistema; la traduzione in linguaggio sintetizzabile del progetto si riduce all’istanziazione dei core ed al progetto della logica di connessione e controllo. Tale approccio soffre tuttavia di grosse limitazioni. I core tipicamente disponibili, ad esempio, sono dipendenti da una particolare architettura hardware e quindi non portabili tra dispositivi di vendor diversi; questo non consente di migrare facilmente un progetto preesistente verso una nuova soluzione tecnologica qualora si dimostri più efficiente. Nella maggior parte dei casi, inoltre, i core hanno un costo di manutenzione non trascurabile ma non sono disponibili in codice sorgente e, quindi, non sono aperti per eventuali modifiche. Infine non possono chiaramente coprire le esigenze di tutti gli utenti per cui non sempre rappresentano la soluzione migliore per una particolare applicazione.

SINTESI DSP

La soluzione offerta da Synplify DSP (figura 1) è invece una vera e propria sintesi DSP, che supera i limiti ed i problemi sopra esposti.

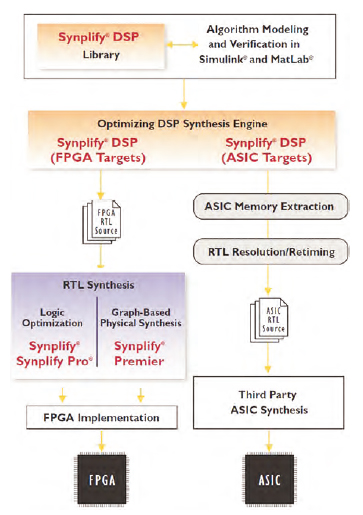

Inizialmente sviluppato per i soli dispositivi FPGA, il tool è ora disponibile – come annunciato durante la conferenza DATE 2007 – anche per ASIC in una versione che si configura come front-end verso ambienti di sintesi di terze parti. La figura 2 mostra il flusso di processo tipico nello sviluppo di applicazioni DSP con Synplify DSP. Il tool è, in pratica, un add-on per Matlab/Simulink che comprende i seguenti moduli:

Un block-set in ambiente Simulink che include le principali funzioni DSP;

- Un motore di sintesi automatica in grado di tradurre un modello Simulink che si basi su tale block-set in una descrizione RTL sintetizzabile ed identica al modello di partenza a livello di singolo bit;

- Un meccanismo automatico di cattura dei vettori di test durante una simulazione Simulink;

- Un meccanismo di generazione automatica di test-bench in linguaggio HDL che consenta di verificare la validità e l’accuratezza della traduzione eseguita e della successiva sintesi fisica.

Il block-set include, oltre agli elementi fondamentali che servono per costruire una qualunque funzione DSP come moltiplicatori, addizionatori e linee di ritardo digitali, anche funzioni di più alto livello come accumulatori, filtri CIC, FIR, commutatori, encoder convoluzionali, DDS e strutture logiche di base come shift-register, memorie RAM e ROM, registri, macchine a stati. La libreria è estendibile e personalizzabile. È inoltre possibile includere black-box qualora si intenda riutilizzare parti di codice HDL già sviluppate in precedenza o rese disponibili da terze parti. In quest’ottica, in particolare, è supportata la co-simulazione con il motore Modelsim. Unitamente alla generazione automatica di test-bench ed alla cattura dei vettori di test, tale funzionalità consente anche una verifica puntuale del risultato della sintesi del modello Matlab Simulink. I moduli inclusi nel block-set di Synplify DSP, inoltre, supportano un meccanismo per la propagazione automatica del tipo di dati. Tale aspetto assume rilevanza particolare nell’analisi degli effetti di quantizzazione introdotti nel modello dalla rappresentazione con precisione tipicamente in virgola fissa dei dati. È sufficiente specificare il tipo di dati in ingresso e la larghezza di parola essendo certi che le informazioni ricavate internamente saranno aggiornate in accordo a tale rappresentazione. Diversamente, poi, dall’approccio classico basato sul riutilizzo di core IP discusso in precedenza, i modelli inclusi nel block-set di Synplify DSP sono indipendenti da una qualsiasi tecnologia. In questo modo il progettista è libero di esplorare diverse soluzioni implementando lo stesso modello funzionale in dispositivi di vendor diversi, scegliendo, infine, la soluzione che in termini di prestazioni o di costi meglio si adatti alla particolare applicazione. Il motore di sintesi incluso nel tool, infatti, è in grado di individuare per ogni famiglia di logiche programmabili supportata la realizzazione architetturale più adeguata considerati i constraints imposti dal progettista e le risorse (in termini, ad esempio, di moduli aritmetici o blocchi di memoria embedded) disponibili nella tecnologia selezionata. Gli unici parametri che devono essere specificati riguardano l’architettura target, il sampling rate desiderato associato alla applicazione e la frequenza di funzionamento del dispositivo. In questi termini, seppure con le ovvie limitazioni del caso, la realizzazione del modello può essere eseguita dagli stessi progettisti DSP che non abbiano una conoscenza di dettaglio delle architetture interne dei diversi dispositivi. Al contrario, qualora sia invece un progettista di logiche programmabili ad occuparsi direttamente della sintesi e della implementazione fisica, il supporto offerto dal tool permette di non avere una conoscenza di dettaglio dell’algoritmo per trovarne la migliore realizzazione. Tra le capacità di ottimizzazione automatica del motore di sintesi incluse in Synplify DSP vi sono, ad esempio, le seguenti:

- Folding: vengono identificate le operazioni comuni eseguite sui diversi flussi di dati in ingresso. Il modello viene, quindi, modificato nel modo seguente:

- viene creata una sola istanza della funzione comune;

- viene creata una logica di multiplexing e controllo per l’utilizzo di questa sola istanza per i diversi flussi singolarmente;

- la frequenza di clock viene incrementata in modo da rispettare le specifiche progettuali in termini di data rate di ingresso.

- Retiming: vengono individuati i path critici dal punto di vista timing. Il modello viene quindi modificato in modo da riarrangiare la disposizione logica dei registri od introdurre nuovi stadi di pipeline così da soddisfare i requisiti di massima frequenza di funzionamento.

- Multi-channelization: nel caso di uno stream di dati in ingresso costituito da più canali (si pensi ad esempio alle componenti RGB di un segnale video composito) soggetti alla stessa elaborazione, è posibile istruire il tool in modo da realizzare una condivisione delle risorse tra i diversi canali.

Oltre ai moduli inclusi nel block-set distribuito per Simulink, Synplify DSP supporta la sintesi di un sottoinsieme di costrutti Matlab in linguaggio M per la descrizione di macchine a stati e logiche di controllo. Sono supportate le tipiche istruzioni condizionali del tipo switch-case ed if-then-else oltre alle operazioni aritmetiche di base come addizione e moltiplicazione. Tale funzionalità denominata M-control, permette di descrivere in un linguaggio sequenziale le strutture di controllo e di data-path delle proprie applicazioni DSP all’interno dello stesso ambiente di progetto dei moduli DSP ed in un linguaggio nativo. I task di controllo saranno successivamente direttamente tradotti in una descrizione RTL.