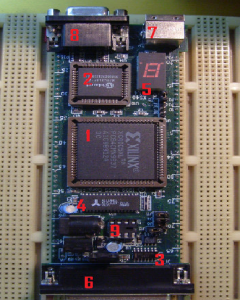

Per la realizzazione dell’elaborazione digitale è stata utilizzata la scheda XS40 prodotta dalla XESS Corporation. La scheda che viene mostrata nella figura iniziale, contiene svariati componenti che permettono la realizzazione di progetti anche molto complessi. Il cuore elaborativo è un dispositivo programmabile FPGA Spartan2 da 9k-Gate in package QFP (Quad Flat Pack) da 144pin.

Vi sono poi numerosi componenti di contorno, indispensabili per l’interfacciamento con il computer. Di seguito si riporta un breve elenco dei componenti, per una descrizione dettagliata ci si riferisca al file XS40 manual ;in formato PDF.

1. FPGA XC4005XL da 9k-Gate in package QFP (Quad Flat Pack) da 144pin.

2.Un microcontrollore 8031uC a 8 bit.

3.Oscillatore programmabile che genera il clock con una frequenza massima di 100MHz e minima di 48.7 kHz.

4.Memoria SRAM da 32KB per la memoria volatile.

5.Display a 7 segmenti.

6.Porta parallela per la connessione con il computer.

7.Porta PS/2 per la connessione di una tastiera.

8.Porta VGA per il pilotaggio di un monitor esterno.

9.Socket per l’aggiunta di una memoria EEPROM compatibile .

Una serie di pin al di sotto della scheda sono collegati ai pin dell’FPGA per permettere il test del funzionamento o per la connessione con altre schede. L’FPGA presente sulla suddetta board è il XC4005XL della XILINX ed appartiene alla famiglia di FPGA XC4000X.

Le caratteristiche tecniche di questo componente sono riportate di seguito:

-Quantità di logic cells : 466 .

-Numero di Gate : 9000 .

-Matrice CLB: 14 x 14 per un totale di 196 CLB .

-Numero di FLIP FLOP : 616.

-Massimo numero di pin per l’I/O : 112 .

-Frequenza massima di clock: 150 MHz.

Vi faccio notare che l'FPGA utilizzata in questa tesi è veramente molto datata rispetto ai giorni nostri, basti pensare che è stata realizzata con processo tecnologico CMOS a 90 nm contro l'attuale processo a 28 nm che permette ad esempio nella Virtex-7 di poter disporre fino a 2 Milioni di logic cells.

Più celle significa poter realizzare più funzioni logiche e quindi aumentare la complessità delle elaborazioni da effettuare. Non solo il numero di celle ma anche il numero di pin di I/O e la frequenza max di clock sono notevolmente aumentate. Tutto ciò ovviamente è stato detto per sottolineare quanto sia stato fatto in quest'ultimo decennio di scaling tecnologico.

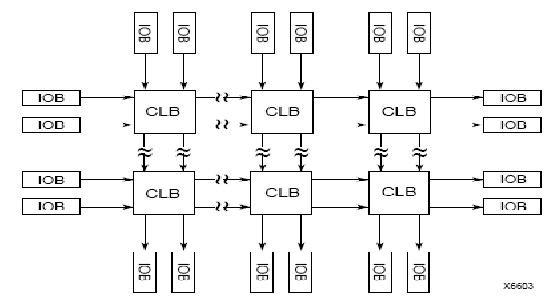

L’architettura generale delle connessioni tra i principali elementi descritti in precedenza è mostrata nella figura successiva:

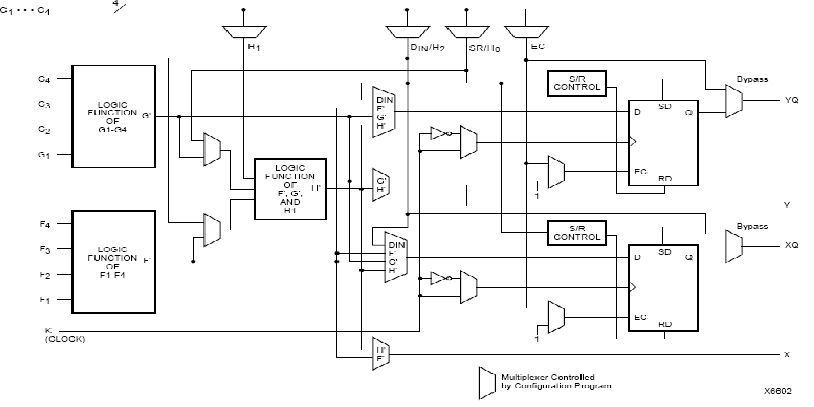

L’elemento principale è il CLB che per questa particolare famiglia di FPGA Xilinx presenta una struttura interna che viene mostrata all'interno della figura successiva:

Il CLB prevede quattro ingressi indipendenti tra loro e per ogni singolo generatore di funzioni logiche (F1-F4, G1-G4), ciascuno dei quali è in grado di implementare una qualsiasi funzione Booleana a quattro ingressi(es. Y=A+B+C+D). Questi generatori di funzione sono realizzati come “Memory Look-up-Tables”, quindi il ritardo di propagazione è indipendente dalla funzione logica implementata.

La presenza di un terzo generatore di funzioni (H), che prevede come possibili ingressi le uscite dei due generatori di funzioni precedenti, consente di connettere due CLB tra di loro. Al più il CLB può elaborare una funzione logica che prevede nove ingressi indipendenti. Il CLB può passare le uscite combinatorie (X e Y) alla rete di interconnessioni, oppure memorizzarle prima tramite i FLIP FLOP D e poi metterle a disposizione per altri collegamenti. Oltre al CLB nella figura precedente si nota la presenza di un secondo blocco IOB che rappresenta l’Input/Output Block.

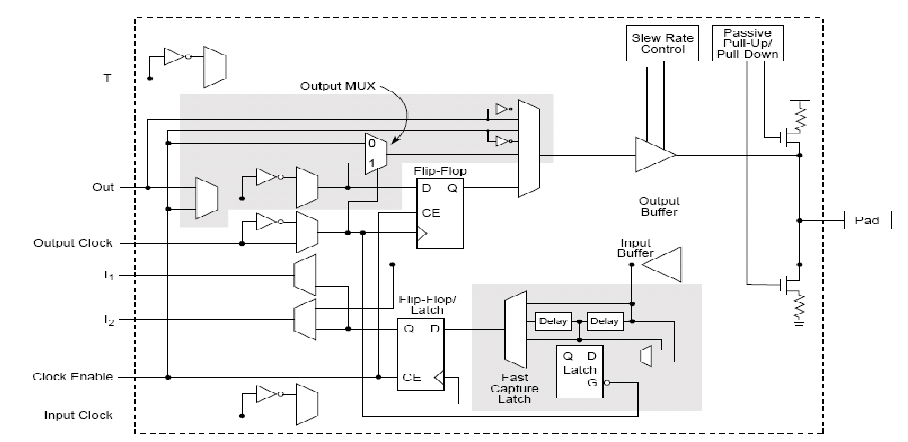

Lo schema semplificato dell’IOB è mostrato nella seguente figura:

L’IOB è un blocco configurabile dall’utente che prevede l’interfaccia tra i pad del package e la logica interna. Ognuno di essi può essere configurato in modo tale che il segnale proveniente dal pad sia di Input,Output o Input/Output tramite i segnali I1 e I2.

Ovviamente la configurazione di questi pin di I/O viene effettuata all'interno del processo di generazione del file binario ".bin" da parte del tool di sviluppo software fornito dalla Xilinx che sarà mostrato in seguito.

Leggi anche: Introduzione alle FPGA

Molto bella questa scheda, in pratica un è un mini computer, ottimo per il fatto di aver aggiunto il supporto vga per poterlo attaccare a una tv.

Una domanda cosa significa che questa scheda è datata, nel senso che c’è ne è una nuova?. Quanto costa?

Una cosa, guarda che il link XS40 manual ; in formato PDF, non funziona

Veramente ? Avevo provato il link e mi pareva funzionava…

Comunque googlando l’ ho trovato :

http://www.xess.com/manuals/xs40-manual-v1_4.pdf

La scheda penso potresti ancora comprarla da qualche parte..prova a vedere..

Per quanto riguarda le evoluzioni ce ne sono quante ne vuoi… qui al mio fianco ho il kit di sviluppo della Spartan 6 ad esempio…quindi basta che vedi sul sito della Xilinx..

Il tool di sviluppo invece è l’ISE e mi pare sia arrivato all’edizione 13 !!

Fatti due conti e capisci subito quanto è “vecchiotta” la Xs40 🙂

ciao

In realtà questa scheda non puoi considerarla come minicomputer,

semplicemente per il fatto che essendo basato FPGA dovresti implementare tu il funzionamento del computer.

comunque un’ottima scheda anche se ormai fa parte del passato.

Ma su queste schede è molto interessante incominciare sono molto semplici ma complete,

ideale per i principianti,

e il fatto che è possibile cambiare anche FPGA questo la rende ancora più interessante visto che potrei cambiare con una altro FPGA così tanti altri il campo di prove