Lo Schmitt-trigger è uno dei circuiti più utilizzati in elettronica. Questo articolo spiegherà brevemente perché. Inoltre, ci aiuterà ad utilizzare questa funzionalità anche quando abbiamo a che fare con logiche programmabili.

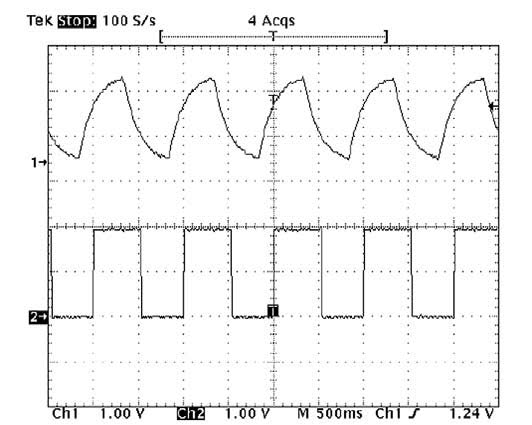

L’uso di Schmitt-trigger migliora notevolmente l’immunità ai disturbi a discapito dell’introduzione di un ritardo di propagazione sul segnale. Per questo motivo l’utilizzo di Schmitt-trigger è diffusissimo nelle applicazioni dove si hanno segnali disturbati e/o segnali a basso slew-rate. Se così non fosse, i disturbi genererebbero oscillazioni e false commutazioni così come farebbero i segnali a basso slew-rate, nei dintorni della tensione di soglia dell’ingresso. Gli Schmitt-trigger risolvono questi problemi aggiungendo l’isteresi. Il risultato è che il buffer d’ingresso non commuterà a un livello alto finché la tensione non supera la soglia superiore VT+, e non commuterà al livello basso fino alla discesa al di sotto della soglia inferiore VT - (Figura 1).

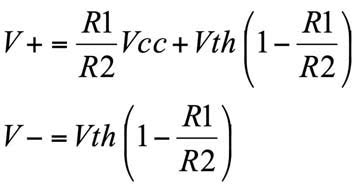

Figura 1: schematizzazione del funzionamento di un buffer d’ingresso con Schmitt-trigger

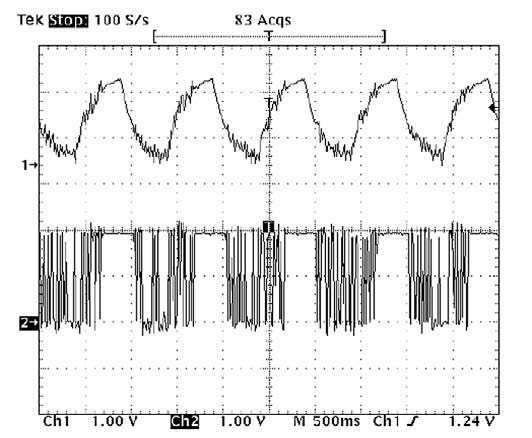

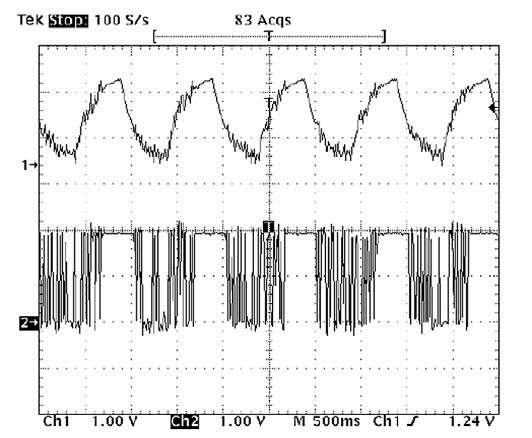

Il risultato è un segnale pulito; il confronto lo si può vedere anche dalle immagini delle Figure 2 e 3 dove un segnale a basso slew-rate, senza utilizzare Schmitt-trigger, genera moltissime commutazioni spurie.

Figura 2: effetto su un segnale a lenta salita del mancato utilizzo di Schmitt-trigger

Figura 3: effetto su un segnale a lenta salita dell’utilizzo di Schmitt-trigger

SCHMITT-TRIGGER E FPGA

In base a quanto affermato in precedenza, i circuiti che al loro interno sono dotati di isteresi con Schmitt-trigger sono utilizzatissimi. Infatti essi accettano segnali in ingresso a basso slew-rate e forniscono in uscita una transizione pulita priva di glitch. Sfortunatamente, le logiche programmabili come le CPLD e le FPGA non offrono agli utilizzatori l’opportunità di sintetizzare in maniera diretta buffer o porte logiche dotate di Schmitt-trigger. L’obbiettivo di questo progetto è andare in aiuto ai progettisti permettendo di realizzare questa utilissima funzionalità solamente con pochi componenti esterni e un pò di codice VHDL. Per creare qualcosa di equivalente a un buffer con Schmitt-trigger si devono utilizzare due resistenze esterne per creare un feedback positivo intorno a un buffer (vedi Figure 4a e 4b). Si possono anche utilizzare quattro resistenze esterne; in questo caso si impostano due livelli di soglia per un flip-flop R-S (Figura 4c). Le seguenti equazioni descrivono come impostare i livelli di soglia, positivi e negativi, per la versione base a due resistenze dello Schmitt-trigger:

In queste equazioni, Vth rappresenta la tensione di soglia in ingresso alla CPLD/FPGA, e Vcc è la tensione di alimentazione.

Figura 4: come utilizzare una porzione di FPGA per realizzare uno Schmitt-trigger con solo due, oppure quattro, resistenze esterne

CIRCUITI CON SCHMITT-TRIGGER REALIZZATI IN FPGA

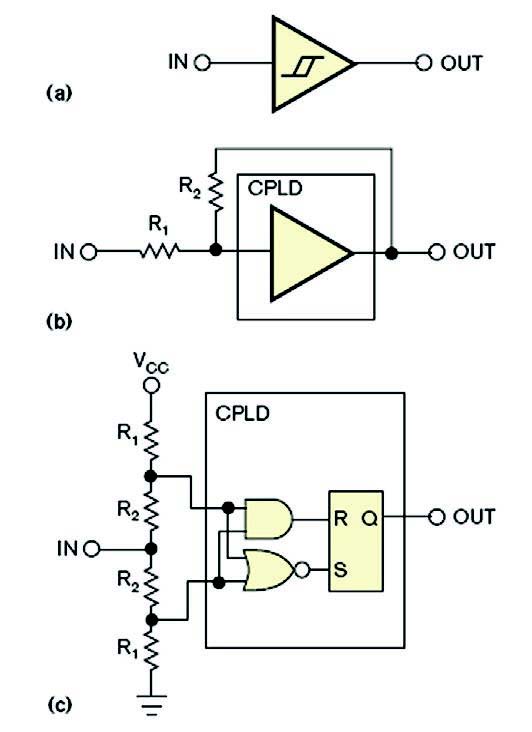

Se adesso al circuito base di Figura 4b aggiungiamo un’ulteriore resistenza e una capacità, possiamo ottenere il circuito di Figura 5 che è un oscillatore RC.

Figura 5: oscillatore RC con Schmitt-trigger

La resistenza R ed il valore di capacità C determinano la frequenza di oscillazione. Affinché tutto funzioni correttamente, è necessario che i valori di R1 e R2 siano comunque molto maggiori di R. Il codice VHDL per l’implementazione dell’oscillatore è estremamente semplice:

Entity Oscillator is Port ( A : in std_logic; B : in std_logic; OUT : out std_logic ); end Oscillator; architecture RTL of Oscillator is begin A <= B; OUT <= not A; end RTL;

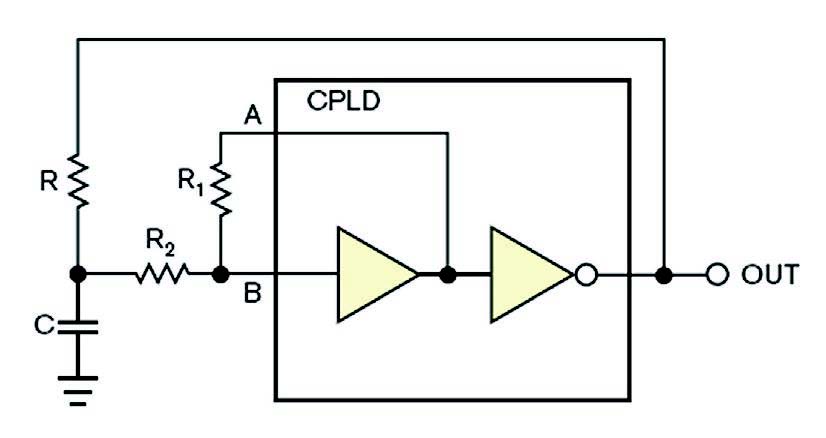

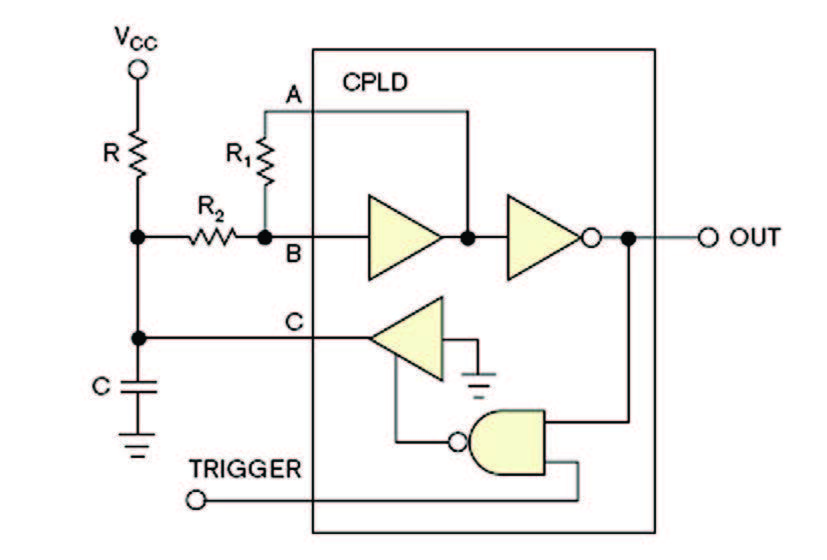

In Figura 6 un buffer open collector fornisce l’attivazione per un monostabile con Schmitt-trigger, intervenendo sulla scarica della capacità C.

Figura 6: multivibratore monostabile con Schmitt-trigger

L’impulso d’uscita del circuito ha una durata determinata dalla costante di tempo RC. Di seguito il codice VHDL per il monostabile:

Entity Monostable is Port ( A : in std_logic; B : in std_logic; Trigger : in std_logic; C : out std_logic; OUT : out std_logic ); end Monostable; architecture RTL of Monostable is begin A <= B; OUT <= not A; C <= ’0’ when Trigger= ’1’ else ’Z’; end RTL;

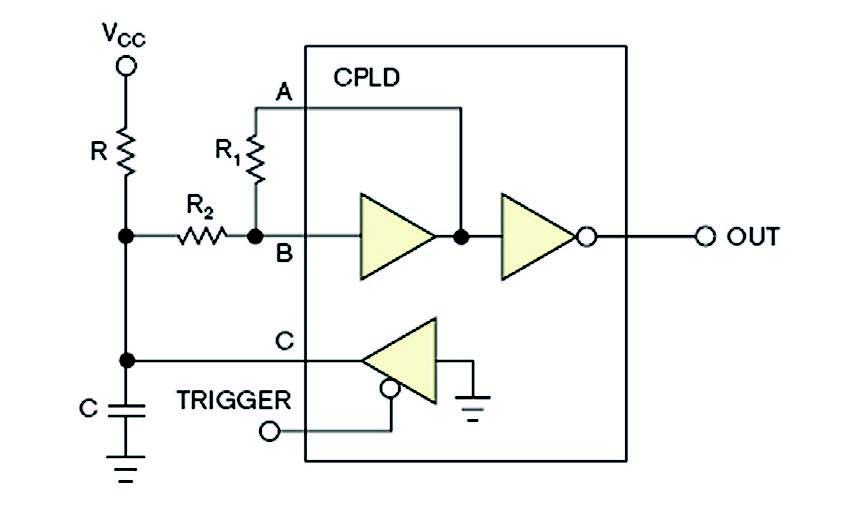

Con un minimo intervento sul monostabile di Figura 6 si può passare dalla configurazione retriggerabile a quella non-retriggerabile semplicemente aggiungendo una porta NAND open collector per scaricare la capacità C, come in Figura 7.

Figura 7: monostabile non retriggerabile con Schmitt-trigger

Di seguito la modifica al codice VHDL:

Entity Monostable is Port ( A : in std_logic; B : in std_logic; Trigger : in std_logic; C : out std_logic; OUT : out std_logic ); end Monostable; architecture RTL of Monostable is begin A <= B; OUT <= not A; C <= ’0’ when Trigger= ’1’ and A=’0’ else ’Z’; end RTL;

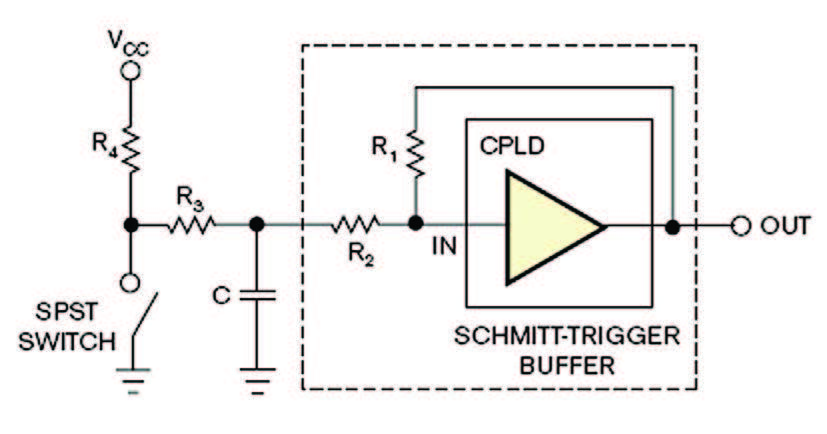

In molti casi l’utilizzo di un buffer con Schmitt-trigger ha la funzione di debouncing per un contatto o un pulsante, anche per questa funzionalità si può sfruttare la logica programmabile, realizzando il circuito di Figura 8. La resistenza R4 fornisce corrente al contatto, mentre R3 e C formano un filtro passa-basso per ridurre i disturbi che si possono generare al contatto.

Figura 8: utilizzo di un buffer con Schmitt-trigger per il debouncing