Benvenuti a un nuovo appuntamento con la Rubrica Firmware Reload. Vedremo in questo articolo come accedere ad una memoria SD su porta SPI.

I dispositivi di memorizzazione di massa SD (Secure Digital) hanno ormai diffusione quasi ovunque, dai telefoni cellulari ai PC, dai data logger per applicazioni di campo alle videocamere digitali. Bassi costi, disponibilità immediata, compatibilità ed interoperabilità, buone prestazioni, sono solo alcuni dei fattori che hanno determinato il successo di questa tecnologia nel settore embedded. Del resto, la gestione di una memoria SD richiede semplicemente una porta SPI ed un software di controllo (tutte risorse che si trovano facilmente sui microcontrollori moderni), eppure apre a molte interessanti applicazioni in diversi ambiti. Di seguito, ad esempio, vogliamo mostrare come interfacciare una memoria SD mediante un micro Zilog della serie ZNEO.

Lo standard SD

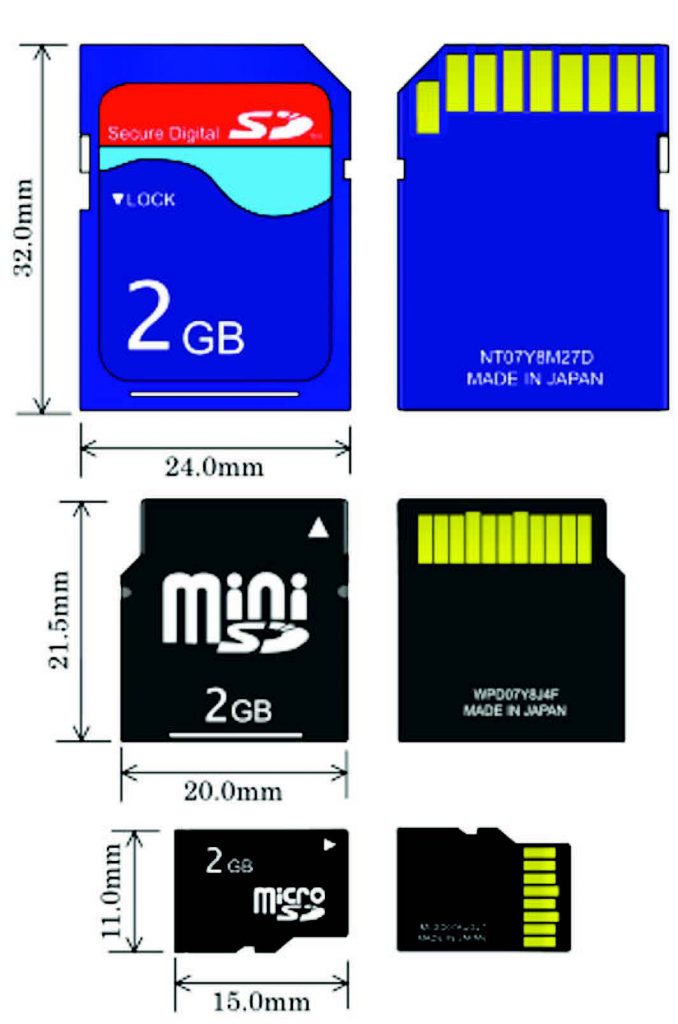

Lo standard SD (Secure Digital) definisce formato e protocollo di accesso per memorie non-volatili. E’ stato proposto nel 1999 da San Disk, Matsushita e Toshiba in risposta alla diffusione delle memory stick sviluppate da Sony. Le specifiche SD sono soggette a diversi brevetti ma una versione "semplificata" del physical layer (che ne definisce le modalità di accesso a più basso livello) può essere scaricata gratuitamente dal web. Le memorie SD hanno, dal punto di vista fisico, come mostrato in Figura 1, un formato standard; misurano 32 mm x 24 mm con uno spessore fino a 1,4 mm. Nel 2006 è stata emessa la specifica per la versione micro-SD che misura solo 11 mm x 15 mm e che ha trovato ampia diffusione, ad esempio, nei cellulari.

Figura 1. Memoria SD, mini-SD e micro-SD

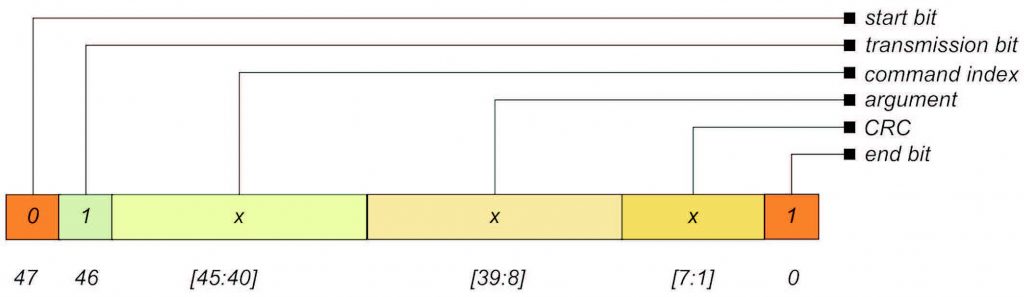

Figura 2. Formato del carattere di comando in modalità SPI

I contatti elettrici sono realizzati mediante pad disposti sul lato inferiore del dispositivo. Le memorie possono essere di tipo read/write o read-only. Richiedono una singola tensione di alimentazione compresa tra 2.7 V e 3.3 V; in realtà alcune versioni possono operare anche con una linea accessoria a più bassa tensione. Sono classificate di classe 0, 2, 4 e 6 in funzione della capacità di trasferimento dati; le schede di classe più elevata assicurano, ad esempio, data rate minimo di 6 MB/s. Il livello fisico definisce tre diverse modalità di accesso alla memoria SD: SD ad 1-bit, SD a 4- bit ed SPI. Le prime due adottano un protocollo comandi/dati proprietario e specifico; in modalità SPI implementano invece su bus SPI (Serial Peripheral Interface) un sotto-insieme delle istruzioni previste nei primi due casi.

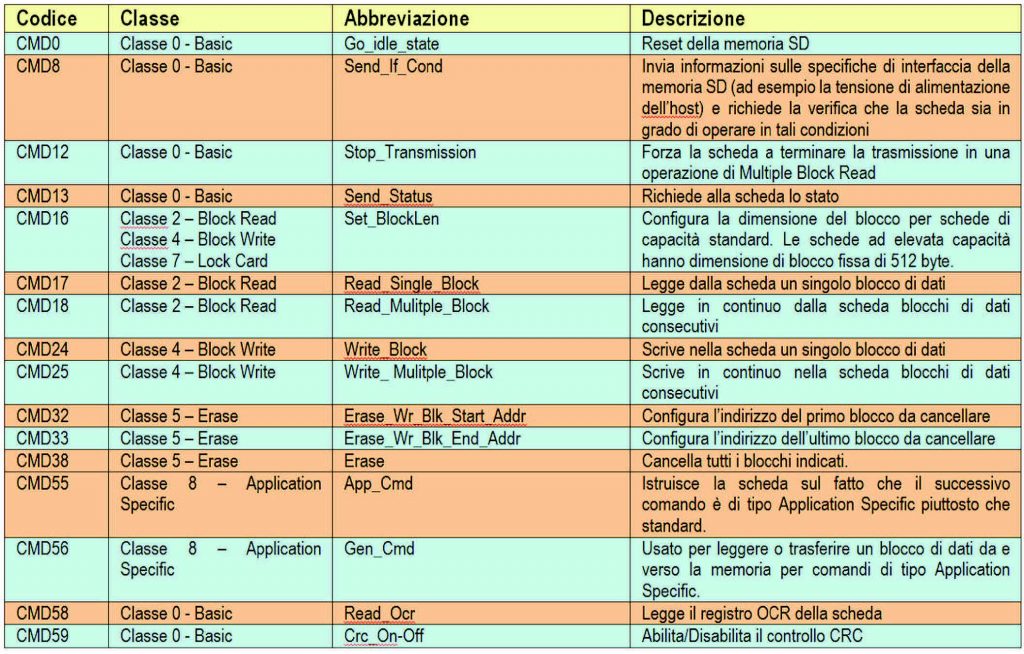

In questa modalità sono previsti comandi, risposte, controlli e dati. I comandi, ad esempio, sono inviati dall’host alla scheda SD per richiedere servizi o procedure. La Tabella 1 riporta i principali, insieme ad una loro breve descrizione. Ogni comando è codificato su 48-bit, inviati attraverso l’interfaccia SPI su 6 byte; la Figura 2 riporta l’interpretazione dei singoli campi del carattere. Il campo command index, ad esempio, specifica il comando mentre quello argument gli eventuali parametri di questo. Un campo dedicato (CRC7) include il controllo CRC del messaggio che consente di verificarne la corretta trasmissione; nelle applicazioni più semplici tale controllo può essere disabilitato mediante opportuna istruzione (CMD59 come da Tabella 1). Per l’accesso in lettura alla memoria SD sono previsti i comandi read_single_block (CMD17) e read_ multiple_block (CMD18). La Figura 3 mostra il corrispondente traffico sul bus SPI da e verso la memoria SD.

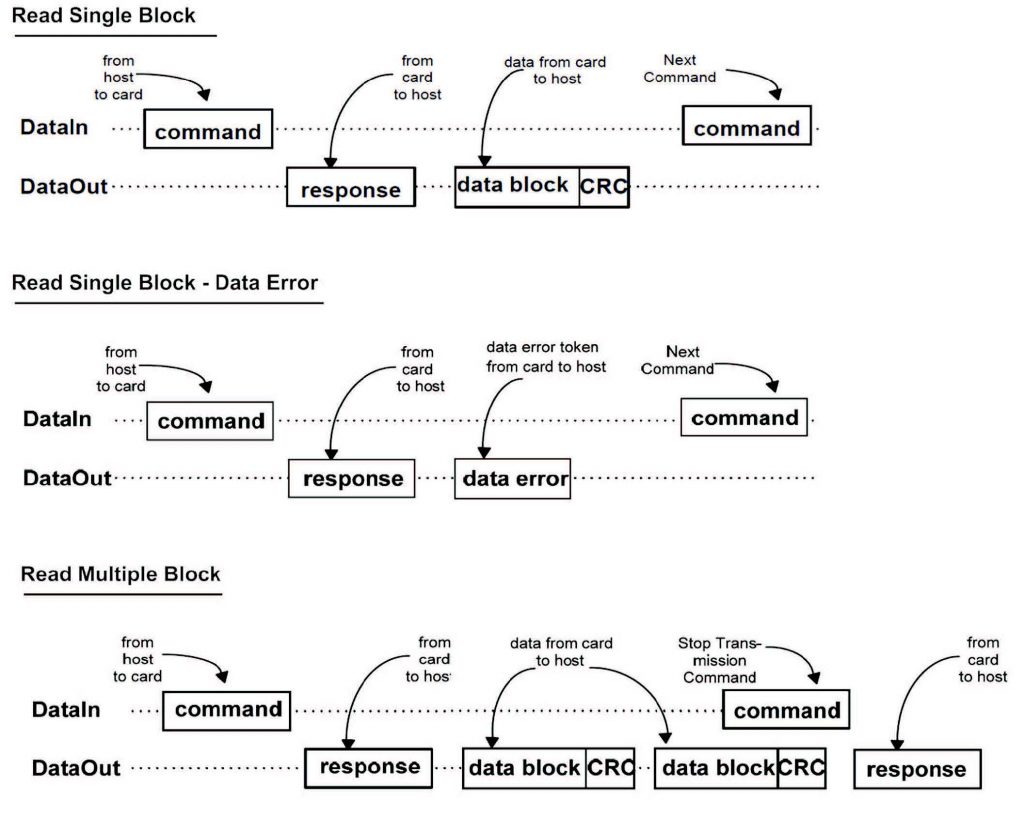

Figura 3. Traffico sul bus SPI per l’accesso in lettura alla memoria SD

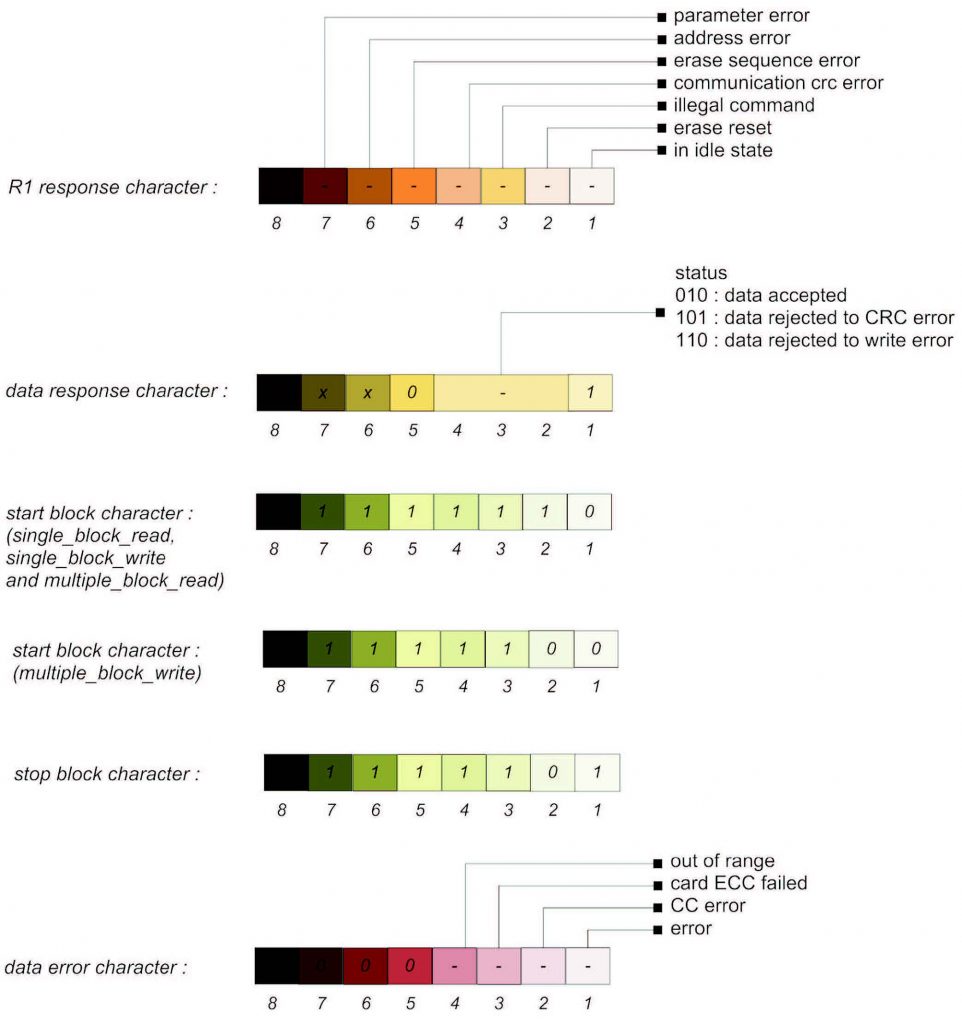

L’operazione read_single_block, ad esempio, è iniziata dall’host inviando il comando sul bus; in questo caso, il campo argument specifica l’indirizzo del blocco di dati che si intende leggere. La memoria SD replica con una risposta di formato R1 (vedi Figura 4) e, se il comando è stato riconosciuto correttamente e può essere eseguito, invia successivamente il blocco di dati richiesto, seguito da un controllo CRC a 16-bit. Se invece il comando non può essere eseguito, la memoria invia un carattere di tipo data_error (Figura 4).

Figura 4. Formato dei caratteri di risposta e di controllo in modalità SPI

Tabella 1

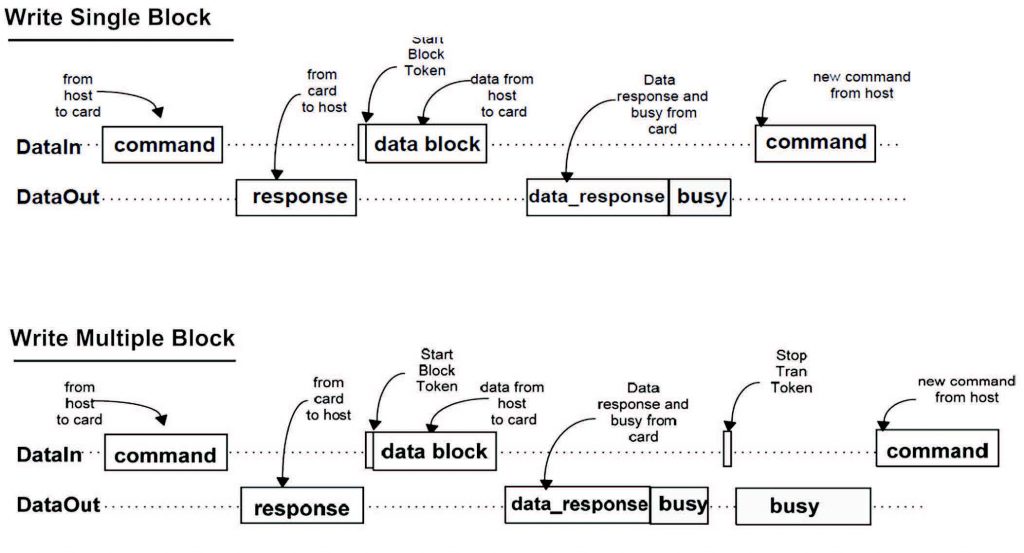

L’esecuzione del comando read_multiple_ block è analoga; nel caso in cui il comando sia ricevuto correttamente, la memoria invia blocchi di dati seguiti da CRC fino a che non riceve il comando di fine stop_transmission (CMD12). L’accesso in scrittura è gestito invece mediante le istruzioni write_block (CMD24) e write_multiple_block (CMD25). La Figura 5 mostra il corrispondente traffico dati sul bus SPI. Come per l’accesso in lettura, nel caso di accessi a singoli blocchi della memoria, l’host invia inizialmente il comando, che include l’indirizzo di pagina cui si intende accedere; quindi attende la risposta e, se questa è corretta, trasmette i dati preceduti dal token start_block (CMD24).

Figura 5. Traffico sul bus SPI per l’accesso in scrittura alla memoria SD

La memoria invia infine un carattere di tipo data_response per indicare l’accettazione dei dati ricevuti; quindi inizia la programmazione dell’area indirizzata. Durante la programmazione forza a zero la linea miso del bus SPI; l’host potrà quindi controllare tale linea per verificare che la fase di programmazione sia terminata. Infine potrà richiedere lo stato della memoria SD mediante opportuno comando. Nel caso di accessi di tipo write_multiple_block, il protocollo è del tutto analogo; i blocchi di dati possono essere inviati l’uno dopo l’altro, ognuno al termine della programmazione del precedente.

L’host può interrompere la sequenza inviando il comando stop_transmission (CMD12) successivamente alla programmazione dell’ultimo blocco di dati che aveva inteso trasferire. Sia per le operazioni di lettura che per quelle di scrittura, il singolo blocco di dati ha dimensione configurabile mediante il comando set_blocklen (CMD16); l’indirizzo usato nelle istruzioni dovrà però essere allineato alla dimensione del blocco configurata. In ogni caso, il blocco non può avere dimensione maggiore di 512 byte. Le schede di elevata capacità non supportano la configurazione della dimensione del blocco che è fissata in 512 byte. Ogni memoria SD si trova in modalità SD al power-up; per forzare la scheda in modalità SPI è necessario asserire la linea CS mentre si sta inviando il comando di Go_idle_state (CMD0). In questo caso, la scheda risponde al comando mediante una risposta di tipo R1 e si porta nella modalità richiesta; l’unico modo per ritornare in modalità SD è allora quello di eseguire un power cycle del dispositivo.

L’Application note di Zilog citata nei riferimenti [1] include il codice sorgente di riferimento per la implementazione delle procedure di inizializzazione della memoria SD e di lettura e scrittura di blocchi di dati come descritte nello standard ed accennate precedentemente. Riguardando il diagramma temporale della Figura 3 è piuttosto immediato riconoscere i diversi passi della procedura. Una volta che si hanno a disposizione le funzioni di base per la lettura e scrittura dei blocchi di una memoria SD a basso livello ci si può divertire a costruirci sopra delle applicazioni più estese, che vanno dalla semplice registrazione di dati in formato raw fino alla gestione di file e directory mediante file system standard. Le funzionalità del file system possono a loro volta essere usate per creare un applicativo più complesso.

Figura 6. La scheda di sviluppo ZNEO Z16F Series Development Kit