Analizziamo il microcontrollore AT91M55800A in particolare soffermandoci sul convertitore A/D.

AT91M55800A è un microcontrollore appartenente alla famiglia del Atmel AT91 16/32 bit basato su un processore ARM7DMI. Le CPU con architettura ARM sono utilizzate in milioni di dispositivi embedded, come microcontrollori, router, schede wifi, telefoni cellulari, smartphones, palmari, console portatili (GameBoy Advance, Nintendo DS), lettori DVD/DivX, lettori MP3/MP4 e tanti altri...

I processori ARM si differenziano dai più noti x86 (nda. i classici processori per PC) per diverse caratteristiche. Innanzitutto, la grossa distinzione è data dal tipo di architettura interna: i processori ARM sono di tipo RISC, mentre i processori x86 sono di tipo CISC; i processori di tipo RISC tendono a implementare istruzioni molto semplici, ma che vengono eseguite ad altissima velocità (tipicamente 1 solo ciclo di clock), mentre i processori CISC generalmente implementano una vasta gamma di istruzioni complesse che richiedono anche diverse decine di cicli di clock per essere eseguite. Queste istruzioni complesse in genere servono a facilitare il compito del programmatore di compilatori, a discapito dell’efficienza e della semplicità interna del chip. I processori ARM dispongono di 31 registri interni, ma in ogni momento sono visibili solo 16 di questi, che vengono selezionati in base alla modalità di funzionamento (modalità Utente, modalità Interrupt, modalità System, ecc...). Ciascuno di questi registri può essere utilizzato indifferentemente come registro sorgente o come registro destinazione di qualunque istruzione. Un’altra caratteristica molto apprezzata dei processori ARM risiede nella cosiddetta esecuzione condizionata. Quasi tutte le istruzioni dei processori ARM possono essere accompagnate da un codice di controllo, chiamato condition code, che modifica l’esecuzione dell’istruzione alla quale viene applicato. I processori ARM, inoltre, si distinguono per la loro capacità di eseguire codice con set di istruzioni misti. Tipicamente un processore ARM moderno supporta fino a 4 set di istruzioni diversi (il numero e il tipo cambiano in base al modello): il set ARM a 32 bit, il set Thumb a 16 bit, il Thumb-2 misto a 16 e 32 bit e il set Java ByteCode (Jazelle) a 8bit. Riassumiamo in breve di seguito alcune caratteristiche del ATM91M55800A:

- 8 kB di RAM

- 3 USARTs

- Master slave SPI

- Oscillatore e PLL

- Convertitore A/D 8 canali 10 bit, 2 canali 10 bit.

Analizziamo in dettagli la sezione relativa al convertitore A/D.

CONVERTITORE A/D: ASPETTI GENERALI

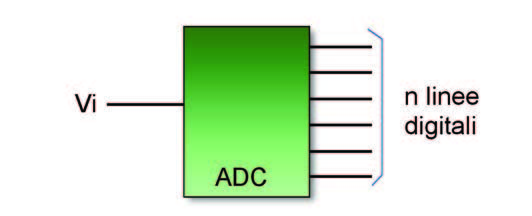

I convertitori analogico-digitali (convertitori A/D o ADC, Analog to Digital Converter) sono i dispositivi che permettono il collegamento fra i sistemi di tipo analogico, cioè interessati da grandezze variabili con continuità, e quelli di tipo digitale, in cui i segnali sono caratterizzati unicamente da 2 livelli di tensione. I fenomeni naturali sono chiaramente di tipo analogico ed anche le principali sorgenti di segnali che interessano i campi dell’elettronica e delle telecomunicazioni sono di tipo analogico (immagini, voci, suoni, misure di grandezze fisiche). D’altra parte, le potenzialità offerte dalle capacità di elaborazione dei sistemi digitali hanno notevolmente accresciuto la diffusione dell’elettronica digitale in tutti i settori. I convertitori A/D hanno per questo assunto una notevole importanza negli ultimi anni e si è assistito ad una grande crescita della loro diffusione commerciale, nonché delle loro prestazioni. Di seguito si presentano i principi che sono alla base della operazione di conversione analogico-digitale. Un convertitore A/D è un dispositivo che, ricevendo in ingresso una tensione analogica, fornisce in uscita un codice binario ad n bit legato all’ampiezza della tensione di ingresso (figura 1).

Figura 1: convertitore A/D.

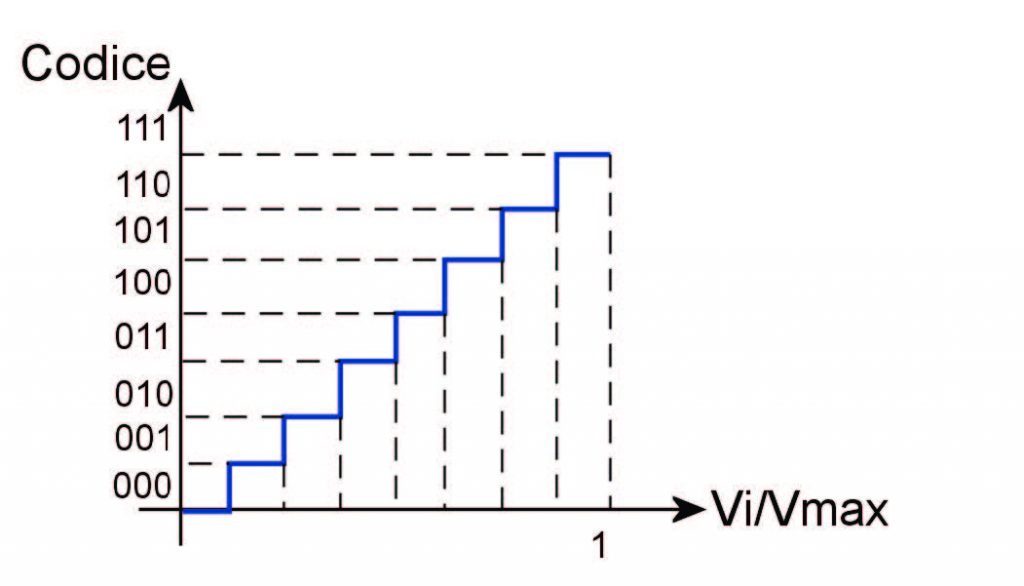

La definizione precedente evidenzia subito il principale aspetto di un convertitore A/D: i codici che possono essere rappresentati in uscita con n bit sono solo 2^n (ad es. con 3 bit possono essere rappresentate 2^3=8 codici), mentre la tensione analogica di ingresso può assumere con continuità un’infinità di valori diversi; i codici devono quindi essere associati ad un intervallo di possibili valori della tensione di ingresso. Si parla in tal caso di quantizzazione della grandezza analogica. L’operazione di quantizzazione implica ovviamente una perdita di informazione, dato che dal codice binario di uscita non è possibile risalire al valore preciso della tensione di ingresso, ma solo all’intervallo di valori associato a quel determinato codice. Ciò si traduce in un effetto chiamato rumore di quantizzazione. L’operazione di quantizzazione effettuata da un convertitore A/D può essere rappresentata graficamente dalla caratteristica di trasferimento (figura 2).

Figura 2: quantizzazione.

Dalla figura l’asse delle ascisse rappresenta la tensione di ingresso Vi normalizzata rispetto al valore massimo Vmax e divisa in 2^n intervalli uguali. Per ciascun intervallo di tensione viene ordinatamente associato uno dei 2^n codici ottenibili con n bit. L’ampiezza degli intervalli di tensione (Vmax/2^n) è comunemente indicata con il simbolo LSB (Least Significant Bit), mentre tale valore, normalizzato rispetto alla tensione massima Vmax è chiamato risoluzione del convertitore (R). Risulta chiaramente:

R=LSB/Vmax=(Vmax/2n)/Vmax=1/2n

pertanto, la risoluzione di un convertitore può essere espressa indicando semplicemente il numero n dei bit di uscita. L’operazione di conversione A/D associa ad un intervallo di valori della tensione in ingresso un unico codice binario. Per eseguire l’operazione inversa, a ciascun codice si associa un valore di tensione che è il valore centrale di ciascun intervallo, chiamato valore nominale del codice. L’operazione di quantizzazione fa quindi perdere di informazione: solo nel caso in cui la tensione Vi è esattamente uguale ad uno dei valori nominali associati ai codici, l’operazione può considerarsi trasparente, mentre in tutti gli altri casi si avrà un errore. L’ampiezza massima dell’errore commesso è pari a metà dell’intervallo di tensione , cioè

E=0.5(Vmax/2n)=Vmax/2n(n+1)

L’effetto di tale errore può essere considerato come un rumore aggiunto alla tensione di ingresso. Supponendo che la tensione Vi possa assumere con la stessa probabilità tutti i valori compresi fra 0 e Vmax, gli errori commessi dalla quantizzazione saranno uniformemente distribuiti fra + E e – E: l’effetto sarà quindi quello di un rumore casuale sommato a Vi e di ampiezza statisticamente distribuita in maniera uniforme nell’intervallo +E/-E. Complessivamente l’operazione di quantizzazione degrada il segnale di ingresso, peggiorando il rapporto segnale/rumore (S/N). Esistono diversi convertitore A/D ognuno con caratteristiche particolari. AT91M55800A è formato da un convertitore ad approssimazioni successive; concentriamoci su questo tipo di convertitore.

CONVERTITORE AD APPROSSIMAZIONI SUCCESSIVE

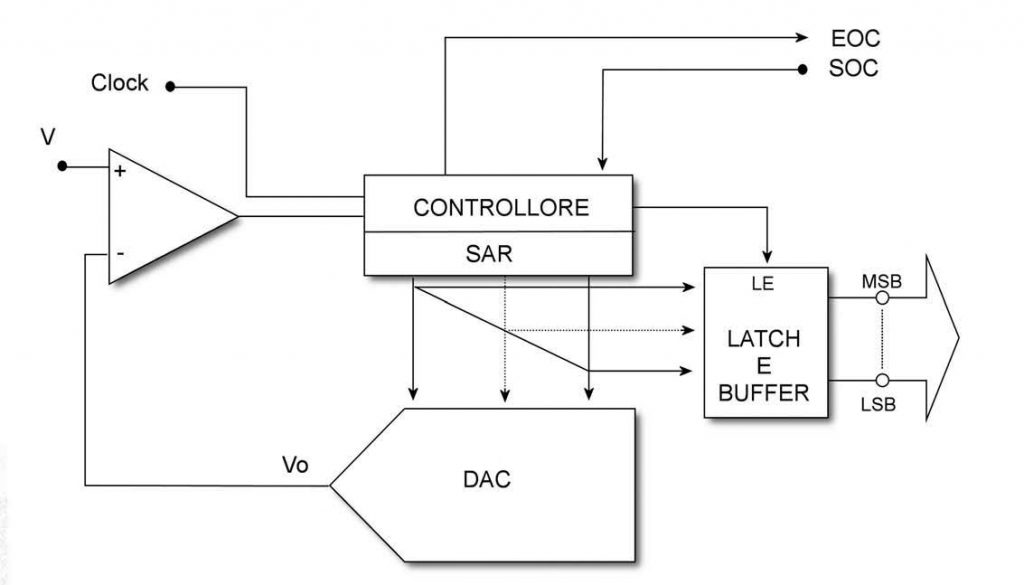

La struttura di questo ADC (Successive Approximation A/D Converter) è riportata in figura 3.

Figura 3: A/D ad approssimazioni successive.

Il compito del controllor è quello di implementare l’algoritmo di funzionamento dell’ADC. A questo scopo il codice digitale generato dal controllore viene depositato in un particolare registro chiamato SAR (Successive Approximation Register). Il contenuto di tale registro costituisce l’ingresso del DAC, la cui uscita, a sua volta, viene confrontata con il campione Vin mediante un comparatore:

- L’inizio della conversione viene attivato inviando al controllore il segnale SOC. In questo modo il controllore carica nel SAR a n bit una parola nella quale il solo MSB è posto a 1 (tutti gli altri bit sono a zero). L’uscita del DAC, pertanto, assume il valore corrispondente al suddetto codice.

- Se Vin > VD il controllore mantiene MSB (cioè Pn) a 1 e carica un altro 1 nel bit immediatamente successivo (cioè pone un i anche nel bit Pn-1).

- Se, invece Vin > VD il controllore pone MSB (cioè Pn) a 0 e carica un 1 nel bit immediatamente successivo (cioè nel bit Pn-1).

- La nuova parola così generata dal controllore viene caricata nel SAR. Di conseguenza, l’uscita del DAC viene aggiornata e assume un nuovo valore corrispondente alla suddetta parola.

- A questo punto l’algoritmo descritto per il bit MSB viene ripetuto in modo identico per il bit Pn-1. Così facendo si ottiene una nuova parola che, depositata nel SAR, produce un nuovo livello della tensione di uscita del DAC.

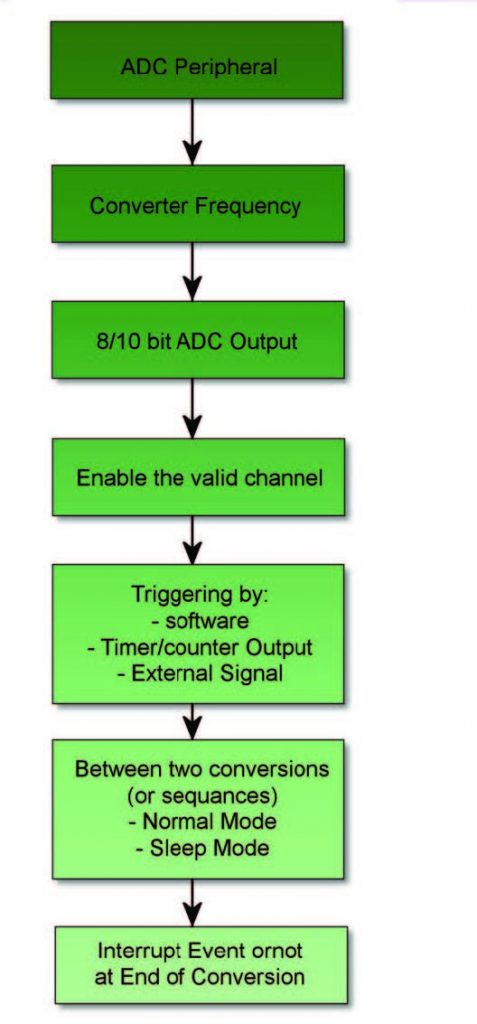

- L’algoritmo viene ora ripetuto per il bit bit Pn-2 e quindi per ciascuno dei rimanenti bit. Per il funzionamento dell’ADC, ATM91M55800A richiede alcuni step di settings visualizzati in figura 4.

Figura 4: settings dell’ADC.

L’inizio del processo di conversione, inoltre, può avvenire in differenti modalità:

- via software per mezzo del bit START del microcontrollore

- via hardware (uscita di un timer embedded)

- via hardware per mezzo di un pin dedicato (AD0TRIG).

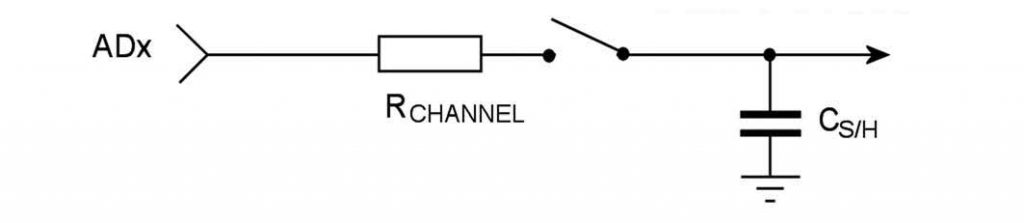

Nel ATM91M55800A, un circuito di sample and hold è integrato nel convertitore A/D (figura 5).

Figura 5: sample & Hold.

dove ADx è l’ingresso del ADC nel ATM, Cs/h è la somma delle capacità parassite presenti nel circuito e Rchannel è la resistenza equivalente del circuito. Il funzionamento è semplice; un condensatore a bassa capacità per conservare la tensione analogica, più un interruttore, che ha una piccola resistenza di ingresso intrinseca, il quale connette e disconnette il condensatore all’ingresso analogico. L’effetto di questo circuito è di mantenere il valore analogico costante per il tempo necessario al convertitore o ad altri circuiti successivi per compiere delle operazioni sul segnale.