Sul blog di Elettronica Open Source puoi leggere non solo tutti gli articoli Premium riservati agli abbonati Platinum 2.0 e inseriti nella rivista Firmware 2.0 (insieme ad articoli tecnici, progetti, approfondimenti sulle tecnologie emergenti, news, tutorial a puntate, e molto altro) ma anche gli articoli della Rubrica Firmware Reload. In questa Rubrica del blog abbiamo raccolto gli articoli tecnici della vecchia rivista cartacea Firmware, che contengono argomenti e temi evergreen per Professionisti, Makers, Hobbisti e Appassionati di elettronica. I convertitori AD rappresentano una pietra miliare dell’elettronica moderna senza la quale l’elaborazione numerica e la trasmissione digitale dei segnali non sarebbero nemmeno pensabili. In questo articolo ne discuteremo le architetture. Particolare enfasi sarà data ad una serie di considerazioni sui convertitori AD più diffusi nell’elettronica applicata: gli ADC ad approssimazioni successive (SAR).

ADC A PIPELINE (O SUBRANGING QUANTIZER)

E’ simile per filosofia all'ADC ad approssimazioni successive, tuttavia, non individua un bit alla volta del codice. In un primo passo avviene una conversione grezza del segnale che viene poi riconvertito da un DAC cui segue la quantizzazione della differenza.

CONSIDERAZIONI E APPROFONDIMENTI SUI CONVERTITORI AD-SAR

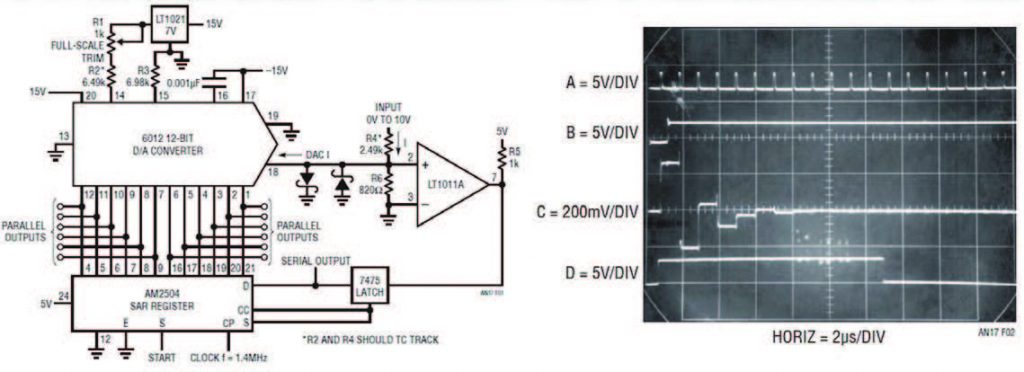

La tecnica più diffusa di conversione AD è oggi quella che fa uso del registro per approssimazioni successive (SAR) tanto che molti chip integrano convertitori AD-SAR. Le loro prestazioni sono via via cresciute parallelamente all’evoluzione delle tecnologie bipolari, CMOS e BiCMOS. Ovviamente, la velocità di conversione è dipendente dal numero di bit del convertitore ed incrementarla al massimo comporta accorgimenti e complicazioni circuitali ben precise. La Figura 1 mostra l’evoluzione temporale di un convertitore SAR a 12-bit, che si esaurisce in circa 12 s.

Figura 1: Esempio di ADC SAR a 12 bit e relativa evoluzione temporale del processo di conversione

Comprendere le limitazioni prestazionali di un simile circuito consente di individuare gli accorgimenti utili alla progettazione di convertitori AD-SAR più veloci. La traccia A rappresenta il clock che viene applicato al circuito integrato convertitore (SAR Register 2504) mentre la traccia B rappresenta l’impulso di start che da inizio alla conversione. In corrispondenza di questo impulso (fronte di salita) il circuito comincia ad elaborare uno ad uno i bit di codice a cominciare dal bit MSB. Il DAC a 12 bit 6012 genera il segnale applicato all’ingresso positivo del comparatore LT1011A (Traccia C). Questa forma d’onda converge progressivamente e con essa converge il codice del SAR. Dopo n colpi di clock (tanti quanti sono i bit di codifica) anche il bit meno significativo LSB risulta definito, il SAR attiva la linea CC (Traccia D) e questo determina la fine della conversione. Il latch 7475 fa sì che completata la conversione, quanto è a monte di esso non possa più avere effetti sul risultato della conversione. In occasione della successiva conversione il latch viene riattivato ed il processo si ripete su di un nuovo campione. I limiti principali, in termini di velocità, di questo circuito sono, come già accennato, da ricercare nel DAC e nel comparatore. Tipicamente un DAC bipolare richiede da 100 a 200ns per eseguire una conversione, ritardo cui è necessario aggiungere quello del comparatore.

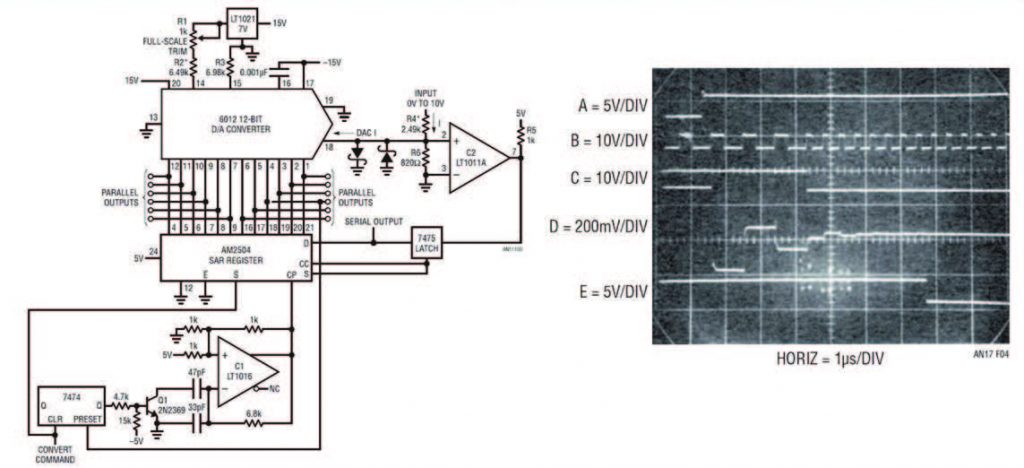

Il diodo di clamping e la resistenza di 820Ω che porta verso GND la capacità di uscita del DAC aiutano il circuito composto da comparatore e DAC ad avere un comportamento dinamico migliore, in sostanza a rispondere più rapidamente. Il circuito può essere tuttavia modificato al fine di incrementare ulteriormente la velocità di conversione. La Figura 2, per esempio, mostra un circuito che utilizza uno schema di modulazione del clock allo scopo di ottenere questo miglioramento. Rispetto al circuito di Figura 1, il terminale di clock (CP) è azionato da un oscillatore a due velocità. A parte questo dettaglio, il circuito funziona allo stesso modo; vediamo con quali miglioramenti. Un impulso di comando di conversione (CC-Convert Command-Traccia A) avvia la routine di conversione. Allo stesso tempo, l’uscita Q del flip-flop 7474 viene posta alta (Traccia C), cosa che determina la polarizzazione del transistor da cui consegue che il condensatore 47pF viene a trovarsi in parallelo al condensatore 33pF. La capacità complessiva entra a far parte del circuito oscillatore costruito intorno a C1 (LT1016) che fa da clock per il registro SAR (pin CP). Il terzo MSB è messo in retroazione con il preset del flip-flop 7474 per cui, ottenuto questo bit, il flip-flop viene resettato (Traccia C), il transistor Q1 si spegne e l’oscillatore che insiste su CP accelera (traccia B). Definiti i primi bit più significativi, il DAC può rispondere più rapidamente per cui la frequenza di clock può essere accelerata. La seconda parte della generazione del codice che codifica il campione procede quindi più rapidamente, il tutto a beneficio di una riduzione del tempo complessivo di conversione. Per convincersi di ciò è possibile confrontare l’evoluzione temporale di Figura 1 con quella di Figura 2.

Figura 2: Circuito di Figura 1 modificato con l’introduzione di un clock a due velocità e relativa evoluzione temporale del processo di conversione AD

Da circa 12us di tempo di conversione si è scesi a 7,5 us. La tecnica della modulazione della velocità di clock consente quindi un significativo miglioramento della velocità di conversione complessiva agendo sull’evoluzione del DAC ma non può in nessun modo ridurre il contributo dato al ritardo dal comparatore. Un certo miglioramento può essere ottenuto anche in questa direzione utilizzando un comparatore più veloce. Il problema è sentito soprattutto se si aumenta il numero di bit di codifica, da 8 a 12 per esempio. In queste condizioni, se si vuole la stessa rapidità di conversione è necessario aumentare il clock, cosa che è inutile se alcune parti del circuito presentano ritardi non sostenibili. Utilizzare per esempio, al posto dell’LT1011, che implica un tempo di ritardo di circa 150ns, un LT1016 consente di ridurre di 10ns il ritardo; questo tuttavia determina anche una diminuzione del guadagno disponibile sul comparatore. Nel tentativo di avere maggiore velocità di risposta, infatti, si finisce per dover accettare minore guadagno. L’LT1011 ha un guadagno minimo pari a 200.000 mentre con l’LT1016 si scende a 1400. Su una scala di 10V con 12 bit di codice, all’LSB corrisponde 10V/4096=2,44mV/LSB. Per pilotare con un livello TTL il latch in uscita in presenza di mezzo LSB di overdrive (1,22mV), il comparatore deve garantire un guadagno minimo pari a 5V/1.22mV=4096 per cui il comparatore non può svolgere il suo compito senza ulteriori accorgimenti. In sintesi è necessario un ulteriore stadio di guadagno prima del comparatore, stadio che, sebbene aggiunga un ulteriore ritardo, consente di ottenere il necessario overdrive (Figura 3).

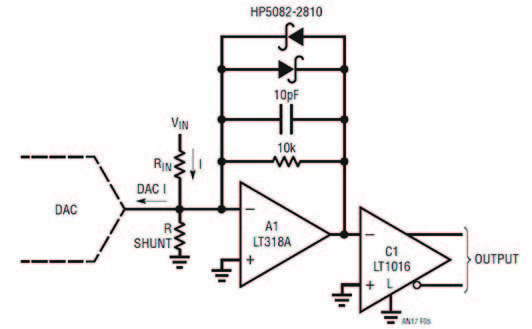

Figura 3: Preamplificazione in ingresso al comparatore dell’AD-SAR di Figura 2

I diodi Schottky prevengono l’eventuale saturazione dell’amplificatore, il condensatore da 10pF consente di compensare la capacità di uscita del DAC e di ottenere un miglior smorzamento sull’uscita dell’amplificatore mentre il resistore di retroazione da 10k consente di ottimizzare il prodotto guadagno-larghezza di banda. Sostituendo l’LT1011 è possibile ottenere tempi di conversione ancora più brevi, compresi tra 3 s e 5 s. La Figura 4 mostra un diverso preamplificatore, ancora più veloce, che fa uso di transistor veloci impiegati a formare uno stadio amplificatore differenziale cascode posto davanti a C1 (LT1016).

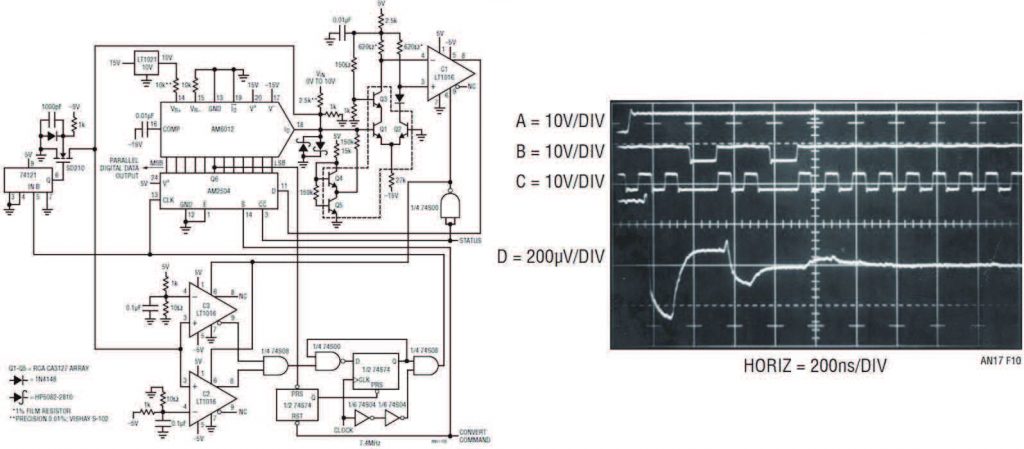

Figura 4: Circuito di Figura 2 modificato con l’inserimento di un preamplificatore differenziale cascode e di una logica di controllo digitale della modulazione del clock al fine di ridurre ulteriormente il tempo di conversione

Il circuito così ottenuto consente di ridurre ulteriormente il tempo della conversione a 12 bit a circa 1,8us. Rispetto al circuito di Figura 2, il controllo e la variazione della velocità del clock è ottenuto attraverso una logica digitale e la frequenza di clock è accelerata dopo la conversione del quinto MSB. La Traccia A è il comando di conversione (conversion command), la traccia B è l’uscita del comparatore a finestra C2-C3, la traccia C è il clock mentre la traccia D rappresenta l’errore.