Le applicazioni satellitari richiedono sempre più flessibilità in termini di capacità e prestazioni. Allo stesso tempo, le costellazioni satellitari diventano sempre più complesse per soddisfare le esigenze di flessibilità e accuratezza dati. I sistemi satellitari dovrebbero essere in grado di interfacciarsi efficacemente e velocemente con array di antenne. È quindi essenziale considerare diverse tecniche di ottimizzazione del circuito per garantire prestazioni elevate.

Introduzione

Il mercato dei semiconduttori è in forte crescita soprattutto quello del settore aerospace. Le risorse per le missioni spaziali necessitano di una forte gestione dati con elevata accuratezza. Nella sede di Teledyne E2V sono state presentate le ultime soluzioni nel campo Aerospace&Defense.

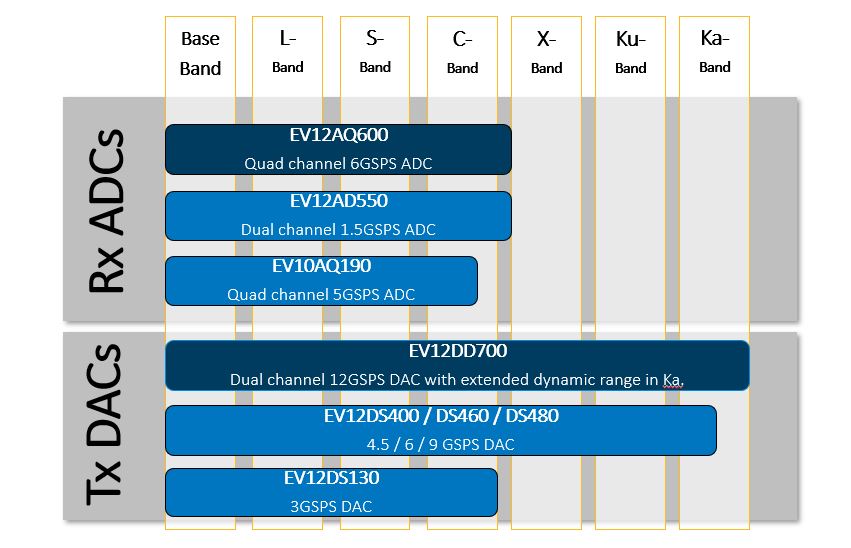

Teledyne ha sede a Grenoble per la produzione di componenti elettronici principalmente nel settore aerospaziale e della difesa. Grenoble è la quinta città più innovativa al mondo secondo la rivista forbes. Attualmente, Teledyne sta concentrando le proprie forze sullo sviluppo di tecniche che possano offrire una maggiore digitalizzazione del dominio RF nella banda Ka, consentendo così la semplificazione e l'operazione simultanea in bande multiple. Teledyne ha iniziato nel 1995 con le soluzioni TS8388 e TS83101, e successivamente con vari miglioramenti grazie a EV12AD550, EV12AQ600 e EV12DQ700. Quest'ultimo come DAC in tutte le bande, L, S, C, X, Ku e Ka. Le applicazioni riguardano principalmente l’imaging radar SAR e sistema di telecomunicazione a microonde. I dispositivi sono realizzati con il fattore di forma più piccolo e offrono una riconfigurazione immediata di tutto il sistema RF per beamforming; immagini radar migliorate con un ricco rilevamento di multi-bande (figura 1).

Il progetto Interstellar

INTERSTELLAR ha l’obiettivo di sviluppare nuove soluzioni di ADC e DAC ad alta velocità, con la garanzia di raggiungere una maggiore integrazione con più canali su una singola scheda, un minore consumo energetico, maggiore larghezza di banda e prestazioni dinamiche migliorate. L'obiettivo del progetto INTERSTELLAR è costruire la prossima generazione di convertitori di dati ad alta velocità per rafforzare competitività per lo spazio.

L'obiettivo del progetto è quello di tenere sotto controllo la salute della terra attraverso l’impiego di tecniche radar con l’obiettivo di mappare il terreno, prevenendo così eventuali tsunami e terremoti. Interstellar H2020 deve garantire la semplificazione della catena del segnale RF e la conversione diretta fino alla banda Ka.

All'interno del progetto due nuovi convertitori di dati sono stati sviluppati e maturati in una fase qualificata (Technology Readiness Level TRL6): ADC EV12AQ600 and DAC EV12DD700. Tali dispositivi facilitano soluzioni innovative per catene di segnali da Rx a Tx per telecomunicazioni satellitari, osservazione della terra, navigazione e missioni scientifiche.

Synchronization chaining

I complessi sistemi di campionamento digitale si basano su tecniche complesse di temporizzazione che provocano dalle latenze tale da non garantire l'allineamento del campione e quindi la perfetta conversione. Inoltre, gli ADC ad alta velocità sono complessi sistemi che richiedono circuiti di clock avanzati (in particolare i divisori di frequenza) che complicano oltretutto il lavoro di sincronizzazione.

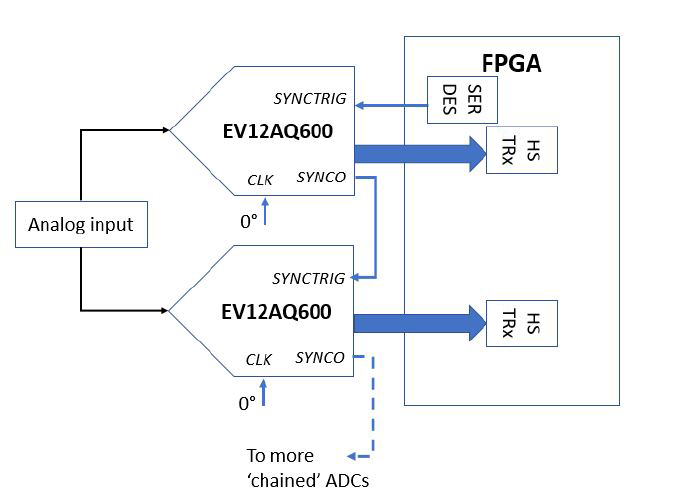

La sincronizzazione deterministica si basa attorno ad una coppia di segnali elettrici differenziali comandati da eventi, che assicurano il reset del sistema di temporizzazione relativamente al convertitore di destinazione e l’allineamento al master clock di riferimento. Inoltre, questo fa si che la sincronizzazione possa essere estesa a ulteriori ADC in tutto il sistema. Questo approccio garantisce la sincronizzazione su un gran numero di canali paralleli durante la vita del sistema.

L’approccio offre un miglior rapporto Signal to Noise Ratio (SNR) grazie alla notevole riduzione delle interferenze e l’impiego del multicanale. Inoltre, permette una maggiore direttività consentendo il riutilizzo della frequenza. Dal punto di vista meccanico, questo approccio riduce il numero di parti meccaniche e la relativa manutenzione. Oggi molte applicazioni usano già beamforming, ma poiché la richiesta di larghezza di banda aumenta inesorabilmente, la precisione del campionamento diventa importante. Alle frequenze dell’ordine dei gigahertz, i tempi di propagazione del segnale diventano importanti a livello di traccia PCB le quali fungono da linee di trasmissione.

La funzione di sincronizzazione chaining aiuta a ridurre la complessità in situazioni di multicanalità in sistemi phased array con tecniche beamforming e MIMO. I singoli ADC includono circuiti dedicati per rilevare e mitigare la metastabilità. La metastabilità descrive il comportamento di un sistema digitale

che, per un breve periodo di tempo, si trova in una posizione instabile. Nasce principalmente nei sistemi digitali complessi che dispongono di molti blocchi di elaborazione con più di un dominio di clock indipendente.

Il segnale di sincronizzazione fornito da un singolo convertitore analogico-digitale è un LVDS.

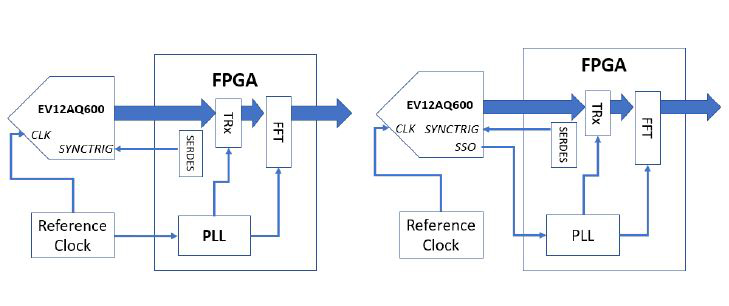

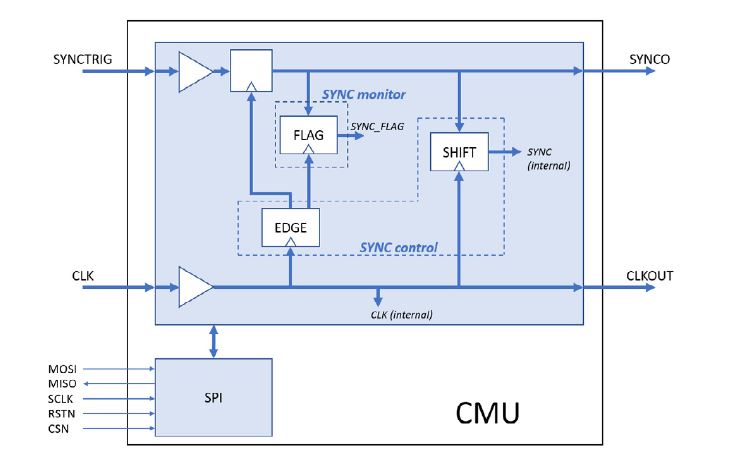

Un segnale differenziale viene generato dall'interno di un blocco di elaborazione del segnale digitale come un FPGA (Figura 2). L'ispezione dell'unità di gestione del clock su chip (CMU) segnala l'origine dei segnali SYNCTRIG e SYNCO insieme ai vari segnali di controllo associati all'interfaccia SPI (figura 3).

Una volta stabilita l'operazione deterministica all'interno di un singolo convertitore, SYNCO è allineato al master clock, mentre il segnale SYNCTRIG può arrivare al primo ADC in modo asincrono rispetto al master clock. La funzione della catena SYNC non ha un impatto diretto sul clock del sistema master, senza aggiungere jitter extra e garantendo una gamma dinamica ottimale. Teledyne-e2v ha dimostrato come questo approccio è solido per la sincronizzazione multicanale di vari sistemi. La latenza deterministica rimane robusta anche di fronte al cambiamento ambientale, o a variazioni di condizioni circuitali quali tensione e temperatura (figura 4).

Avionica & ARM

Al giorno d’oggi vi è un aumento del numero di piattaforme hardware disponibili in commercio grazie anche ai progressi nella disponibilità di processori avanzati ad alta efficienza. Inoltre, la maggiore densità elettronica e la crescente disponibilità di interfacce permettono alle nuove piattaforme embedded di non avere più preoccupazioni di risorse di memoria.

L'interesse crescente nell'esplorazione dello spazio ha aumentato la domanda di veicoli che possono raggiungere un'elevata velocità di calcolo utilizzando un basso consumo energetico. I microprocessori per applicazioni spaziali dimostrano una velocità sempre crescente, tuttavia le loro prestazioni rimangono molto più lente di quelle dei chip usati sulla terra.

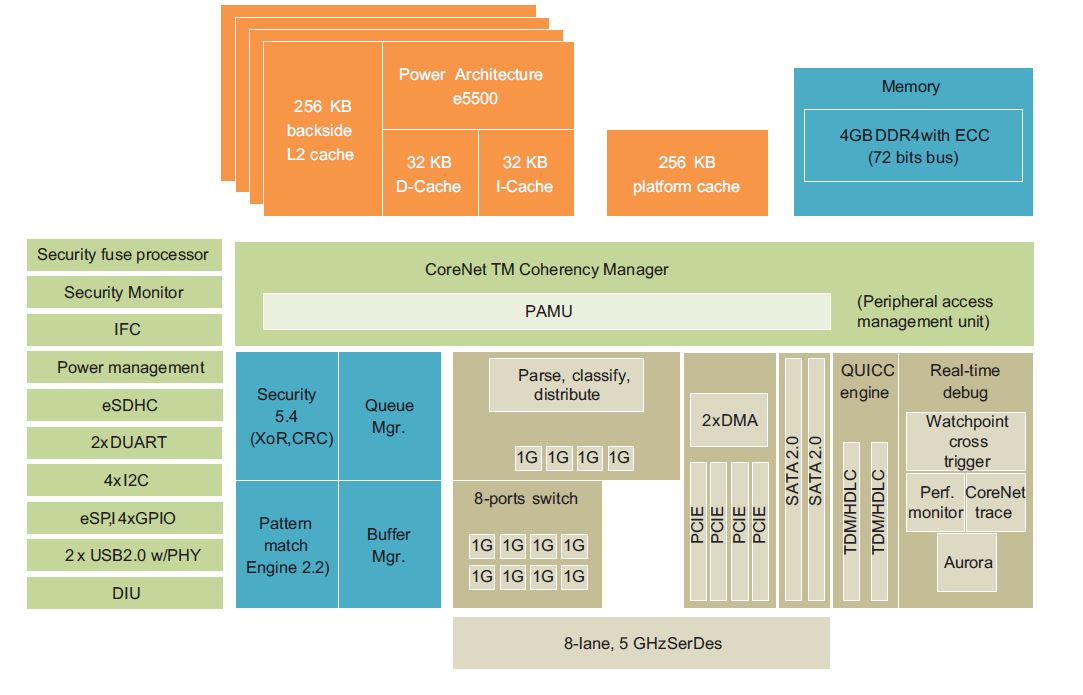

Qormino™ combina un processore e una memoria sullo stesso piccolo substrato che facilita la semplificazione dei progetti elettronici e consente di risparmiare spazio sul circuito stampato. Il primo prodotto della famiglia Qormino ™ è il QT1040-4GB che integra un processore QorIQ™ T1040 NXP con una memoria DDR4. Per contrastare i problemi di obsolescenza dei componenti comuni, le soluzioni vengono offerte con una garanzia di fornitura di almeno 15 anni. Il QT1040-4GB opera a livello commerciale e industriale per applicazioni di networking, assemblaggio e test, medicale, aerospaziale e sistemi embedded (figura 5).

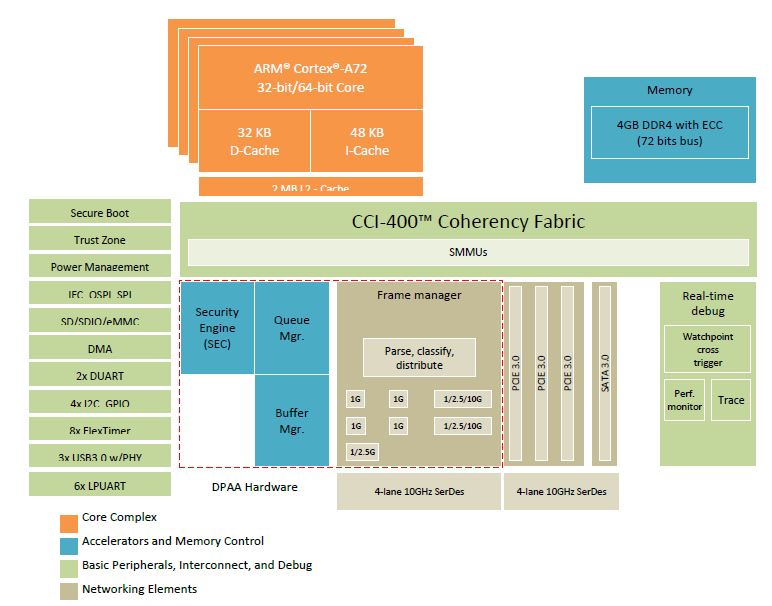

Il nuovo modulo Qormino QLS1046-4GB integra il QorIQ LS1046 di NXP che presenta un processore quad Arm Cortex A72 ed è inoltre combinato con una memoria DDR4 da 4 GB con 8 bit ECC. Il processore conserva le prestazioni di velocità, riducendo il fattore di forma di oltre 1000 mm². È fatto in modo da qualificarsi in più gradi di temperatura, per facilitare l'adozione nei programmi aerospaziali e sono pre-qualificati per gli standard dell'industria aerospaziale e militare (figura 6).

Conclusione

Con l'avanzare della tecnologia, la velocità operativa dei sistemi aumenta esponenzialmente: siamo ormain entrati nella regione sotto il nanosecondo. Con questo trend, anche il tasso di campionamento degli ADC aumenta. Essendo uno dei componenti critici che collegano il segnale analogico reale e quello digitale, è quindi importante studiare tecniche di progettazione circuitali e di PCB per garantire l'integrità del segnale ed elevate prestazioni generali del sistema.

Bibliografia

- Un video di presentazione sul synchornization chaining

- Articolo tecnico di apprfondimento

- Il processore Qorminio

Very Nice