Vediamo le caratteristiche dei microprocessori ARM. In particolare ci soffermeremo su quelli della NXP Semiconductors.

L'architettura ARM (precedentemente Advanced RISC Machine, prima ancora Acorn RISC Machine) indica una famiglia di microprocessori RISC a 32bit utilizzata in una moltitudine di sistemi embedded (figura 1).

Figura 1: microprocessore ARM.

Grazie alle sue caratteristiche di basso consumo (rapportato alle prestazioni) l’architettura ARM domina il settore dei dispositivi mobili dove il risparmio energetico delle batterie è fondamentale. Attualmente la famiglia ARM copre il 75% del mercato mondiale dei processori a 32 bit per applicazioni embedded ed è una delle più diffuse architetture a 32 bit del mondo. I processori ARM vengono utilizzati in PDA, cellulari, lettori multimediali, videogiochi portatili e periferiche per computer. Importanti rami della famiglia ARM sono i processori XScale e i processori OMAP prodotti da Texas Instruments. I dispositivi ARM presentano un’architettura RISC ‘load and store’ per parole di 16 e 32 bit, un set di istruzioni ortogonali, 37 registri di interi a 32-bit (6 registri di stato e 31 di uso generale) e 7 modi di operare (USR, FIQ, IRQ, SVC, ABT, SYS, UND). Una caratteristica curiosa dei processori ARM è che, con il tempo, il set di istruzioni incrementa. I primi processori ARM (prima dell’ARM7TDMI) per esempio non avevano istruzioni per caricare quantità a due bit. E quindi non erano in grado di gestire direttamente tipi di dati corti. I primi processori ARM di largo consumo come gli ARM7 erano basati su un disegno con pipeline a 3 stadi: fetch, decode e execute. I processori più moderni, come l’ARM11, per incrementare le prestazioni, sono passati a pipeline a 5 stadi. Altri cambiamenti per incrementare le prestazioni includono un sommatore veloce e un sistema di predizione dei salti. Altra interessantissima caratteristica dei processori ARM riguarda le instrunction set presenti. Oltre al nativo ARM a 32 bit ne esistono altri due molto interessanti: il Thumb e il Jazelle. Il codice Thumb, avente istruzioni di 16 bit, è più leggero del classico ARM ma è dotato di meno funzionalità. Per esempio solo i salti possono essere condizionati e alcuni opcode non possono essere utilizzati da tutte le istruzioni. Nonostante queste limitazioni, nel caso di sistemi dotati di limitata larghezza di banda verso la memoria, il Thumb fornisce prestazioni migliori del set di istruzioni completo. Molti sistemi embedded sono dotati di un bus verso la memoria limitato e sebbene il processore possa indirizzare con 32 bit spesso si utilizzano indirizzamenti a 16 bit o simili. In queste situazioni conviene creare codice Thumb per la maggior parte del programma e ottimizzare le parti di codice che richiedono molta potenza di calcolo utilizzando il set di istruzioni completo. Esistono anche due varianti del codice Thumb: il Thumb-2 il quale contiene particolari istruzioni a 32 bit, e il Thumb2EE specificamente progettato per gestire codice per applicazioni real time. Il primo processore dotato di Thumb è stato l’ARM7TDMI. Tutti gli ARM9 e le famiglie successive (incluso gli XScale) sono dotati di Thumb. Il codice Jazelle permette al processore di eseguire il Java byte code in modo nativo. Questa tecnologia è totalmente compatibile con il codice ARM standard e il Thumb. Il primo processore dotato di Jazelle è stato l’ARM926J-S, utilizzato sui telefoni cellulari per velocizzare l’esecuzione del software e dei giochi Java. Il Jazelle aumenta per oltre il 95% le prestazioni del codice java supportando 140 istruzioni java ed emulando le restanti 94 con routine ARM.

ARM della NXP

La novità annunciata da NXP nel 2009 è costituita dalla prima implementazione dell’architettura Cortex-M0, che si caratterizza per le piccole dimensioni e la semplicità, doti che si traducono in consumi bassi, alte prestazioni e facilità di programmazione. Nell’implementazione realizzata da NXP con il dispositivo LPC1100, la riduzione dei consumi è ottenuta anche tramite un largo ricorso alla modalità sleep, che determina un assorbimento medio di corrente inferiore a quello dei micro a 16 bit. A ciò contribuisce anche l’alta velocità di elaborazione: dopo aver completato rapidamente il proprio compito, il dispositivo può infatti rimettersi subito “a dormire”. L’architettura Cortex-M0 si caratterizza inoltre per varie particolarità che facilitano la programmazione: le routine degli interrupt possono essere codificate in C, i trasferimenti di dati a 8, 16 e 32 bit sono ottenuti tramite singole istruzioni, il numero delle istruzioni assembler è limitato a sessanta ecc. Tutta la complessità tipica dei 32 bit, inoltre, è stata eliminata. Il chip impiega un core semplificato funzionante a 50 MHz ed è dotato di DAC a 10 bit, una sofisticata unità per la gestione dell’alimentazione, un clock in tempo reale realizzato in hardware che non richiede aggiornamenti periodici in modalità sleep. Attualmente NXP Semiconductors (figura 2) ha presentato la famiglia LPC4000, la prima architettura di controller dual-core asimmetrici dei segnali digitali al mondo che incorpora i processori ARM Cortex-M4 e Cortex-M0.

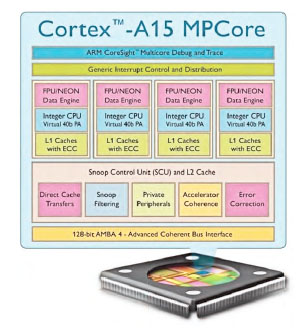

Figura 2: Cortex A15.

La famiglia di controller LPC4000 offre tutti i vantaggi derivanti dalla possibilità di sviluppare applicazioni DSP e MCU all’interno di un’unica architettura e di un solo ambiente di sviluppo. Grazie alla sua architettura dual-core e a un set di esclusive periferiche configurabili, la famiglia di controller LPC4000 facilita lo sviluppo di un’ampia gamma di applicazioni quali controllo motore, sistemi di gestione dell’alimentazione, dispositivi di automazione industriale sistemi robotici, apparecchiature medicali, accessori per il settore automotive e dispositivi audio embedded. I progettisti di microcontrollori alla ricerca di metodi più efficienti per gestire algoritmi matematici complessi e i designer di DSP non disposti a sottostare alle limitazioni imposte dalle periferiche beneficeranno in eguale misura dell’esclusiva architettura che caratterizza la famiglia di controller LPC4000. Questi sistemi sono ideali anche per i progettisti che desiderano effettuare l’upgrade da un processore DSC esistente. La famiglia NXP LPC4000 comprende i seguenti elementi:

- Processore Cortex-M4

Il processore Cortex-M4 unisce i vantaggi tipici di un microcontrollore, ovvero controllo integrato degli interrupt, low power mode, bassi costi di debugging e facilità d’impiego, con funzionalità DSP avanzate quali MAC singlecycle, tecniche SIMD (Single Instruction Multiple Data), aritmetica saturata e unità di calcolo in virgola mobile (FPU, Floating Point Unit).

- Architettura di memoria ottimizzata

La famiglia di controller LPC4000 è basata su un’architettura Flash con accesso a 256 bit che riduce i consumi di corrente attraverso fetch di memoria ridotti al minimo, ottimizzando nel contempo le performance del processore Cortex-M4. I controller LPC4000 adottano un’architettura dual bank che fornisce fino a 1MB di Flash per la riprogrammazione e il partizionamento flessibile della memoria in totale sicurezza. I dispositivi LPC4000 offrono.

inoltre 264 KB di SRAM, il valore più elevato di qualunque microcontrollore Cortex-M.

- Co-processore Cortex-M0.

Un sottosistema di elaborazione CortexM0 effettua in larga misura le operazioni di gestione dati e I/O che possono consumare preziosa capacità computazionale del core Cortex-M4. In questo modo il core può dedicarsi integralmente al supporto delle applicazioni di elaborazione dei segnali digitali. La disponibilità di una piattaforma dual-core asimmetrica offre agli sviluppatori i vantaggi in termini di consumi, costi e complessità minori-che sono propri di una soluzione basata su chip unico, permettendo di partizionare più facilmente il software.

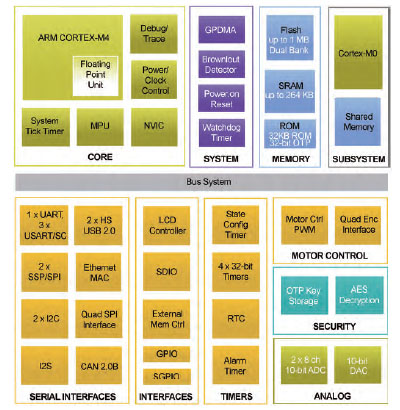

Figura 3: ARM della NXP LPC4000.

Esclusive periferiche configurabili

Le esclusive periferiche configurabili NXP disponibili sulla famiglia di controller LPC4000 includono uno State Configurable Timer, una Interfaccia SPI seriale (SPIFI) e una Serial GPIO Interface. Il State Configurable Timer Subsystem è composta da un array di timers e da una macchina a stati che supporta funzionalità complesse quali generazione di forme d’onda PWM pilotate da eventi, sincronizzazione ADC e controllo deadtime. L’interfaccia SPI seriale SPIFI fornisce una connessione trasparente memory-mapped ad alta velocità compatibile con SPI e quad-SPI di ogni produttore di flash seriali attualmente sul mercato. La Serial GPIO Interface di NXP, disponibile per la prima volta sulla famiglia LPC4000, offre agli sviluppatori la possibilità di collegarsi con qualunque interfaccia seriale non standard oppure di emulare molteplici interfacce seriali standard (quali I2S, TDM per l’audio multicanale, I2C e altre). Altre periferiche disponibili su alcuni componenti della famiglia LPC4000 comprendono due controller HS USB, un HS PHY on-chip, un controller Ethernet 10/100T con calcolo del checksum TCP/IP via hardware e un controller LCD a colori ad alta risoluzione.

Funzionalità standard

Tra le funzionalità standard comuni a tutti i componenti della famiglia LPC4000 figurano 32 KB di ROM contenente boot code e driver software on-chip, crittografia AES-128 (soltanto su alcuni componenti della famiglia), controller GPDMA (General-Purpose DMA) a otto canali, due ADC a 10 bit e un DAC a 10 bit con rate di conversione dati di 400k sample/s, una unità controllo motore PWM ed interfaccia per encoder in quadratura, 4 UART, 2 interfacce I2C Fast-mode Plus, interfaccia I2S, 2 interfacce SSP/SPI, un’interfaccia smart card, 4 timer, un watchdog timer “windowed”, un alarm timer, un RTC ultra-low power con 256 byte di register di backup alimentato a batteria e fino a 146 pin I/O general purpose.

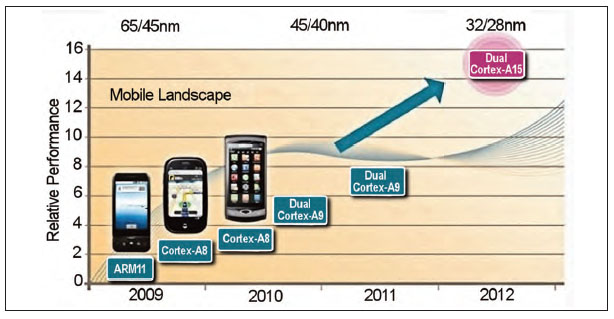

Figura 4: performance.

Sviluppi futuri dell'ARM

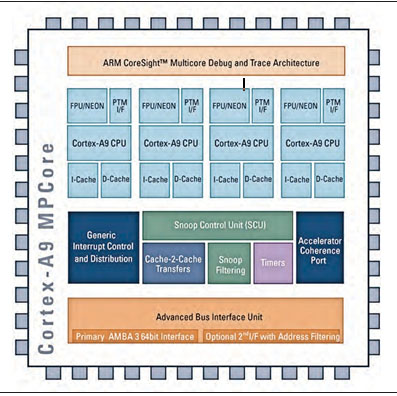

ARM (figura 2 e 4) ha presentato l’architettura multi-core Cortex A15 (Eagle), in grado di lavorare fino a una frequenza 2,5 GHz in configurazione quad-core, ma saranno possibili anche soluzioni a 8/16 core a seconda dell’ambito in cui verranno implementati i chip. Secondo l’azienda il nuovo system on chip è cinque volte più potente

di dual-core Cortex A8 a 1 GHz. Al centro dei questa architettura c’è Amba 4, bus integrato nel chip che permette a cluster di quattro core di comunicare tra loro. L’architettura integrerà diversi miglioramenti nell’ambito della virtualizzazione e nella gestione della memoria. I possessori di smartphone potranno così passare, se lo vorranno, tra due ambienti operativi, uno casalingo e uno lavorativo. Per quanto concerne la memoria l’architettura supporta fino a 1 terabyte di memoria fisica contro i 4 GB attuali. Il nuovo chip sarà pienamente compatibile con Android, Flash Player, Java Platform Standard Edition (Java SE), JavaFX, Linux, Windows Embedded Compact 7, Symbian e Ubuntu. La versione per smartphone di Eagle dovrebbe lavorare tra 1 e 1,5 GHz in configurazione dual-core, mentre quella per gli home server tra 1,5 e 2,5 GHz in versione quad-core. La differenza è chiaramente dovuta ai limiti di consumo imposti dagli smartphone. ARM a tal proposito non ha comunicato dati. Alcuni dirigenti si sono limitati a dire che A15 avrà “un’impronta energetica comparabile a quella degli attuali design”. Cortex A15 è la vera architettura ARM che punta a entrare nei server, come quelli per la stampa o quelli casalinghi. Tuttavia ha un punto negativo: si tratta di un’architettura a 32 bit e non a 64 bit. I primi chip ARM Cortex A15 sono attesi tra il 2012 e il 2013, prodotti da Texas Instruments, Samsung e ST Ericsson. I chip saranno realizzati con i processi a 32 o 28 nanometri.