La progettazione di una piattaforma hardware deve considerare parecchi aspetti e il gestore della piattaforma deve essere scelto con cura. Sempre più piattaforme utilizzano delle PLD per la gestione, il perché è facile da capire.

Il controllo della sequenza di powerup, le espansioni dei pin di input/output, le traslazioni di livello e gli adattamenti di interfaccia, sono solo alcune, ma tra le più diffuse, funzioni che trovano applicazione nei dispositivi per il mercato telecom, per i server e per le applicazioni industriali. Per queste e altre applicazioni, i progettisti si stanno sempre di più orientando all’utilizzo di logiche programmabili non volatili (PLD) per i loro progetti. I benefici sotto l’aspetto del time-to-market e della fles sibilità di progettazione nei confronti delle ASIC e degli ASSP sono innegabili. Utilizzando le PLD i progettisti possono rispondere rapidamente alle richieste del mercato, a cambiamenti di standard e requisiti di progetti mutati in corso d’opera. In più le PLD permettono la riduzione del costo complessivo del sistema, sostituendo componentistica discreta e minimizzando le dimensioni necessarie per i PCB.

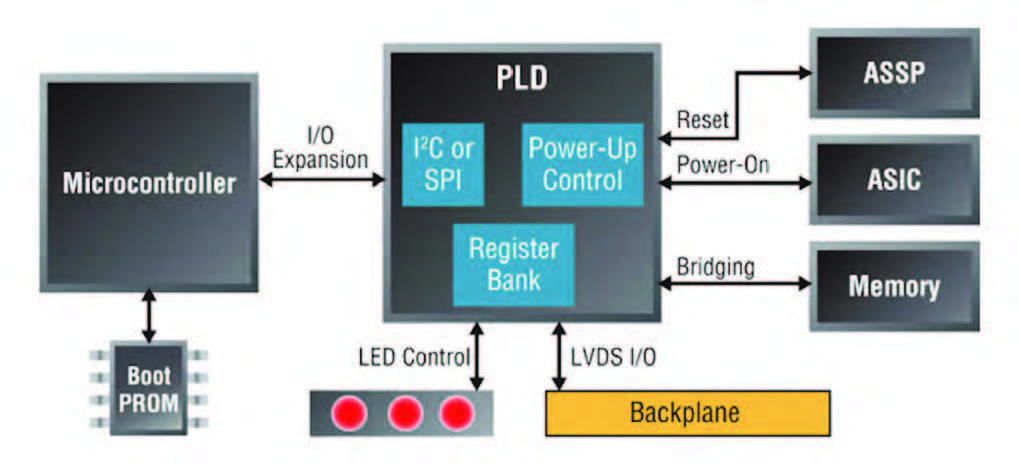

TIPICA APPLICAZIONE SERVER CON PLD

In figura 1 è rappresentato lo schema di una piattaforma server che utilizza una PLD.

Figura 1: la PLD funziona come gestore di una piattaforma server.

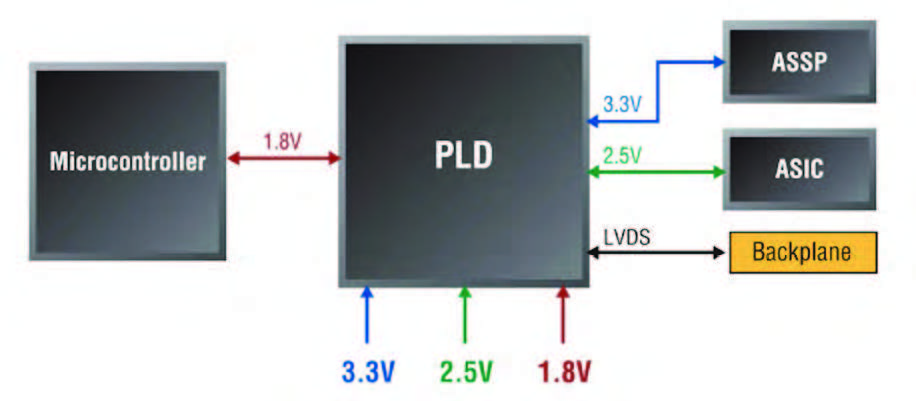

Il gestore della piattaforma in questo caso è proprio la PLD, questa comunica con microcontrollore, ASSP, ASIC, LED e il backplane. Il microcontrollore controlla lo stato del sistema attraverso il banco di registri della PLD comunicando via I2C o SPI. Attraverso i LED la PLD fornisce le informazioni sullo stato del sistema e si interfaccia sullo spazio di memoria per immagazzinare le informazioni di login o i dati di configurazione. La PLD comunica anche con i segnali di controllo sul backplane attraverso segnali LVDS, fornendo i necessari segnali di system reset e power-on alla ASSP e alla ASIC. Vediamo se l’utilizzo della PLD consente di poter gestire la piattaforma sotto tutti gli aspetti. Partiamo considerando la situazione di accensione della piattaforma, all’avvio si deve prevedere una situazione di “instant-on”. Il collegamento allo spazio di memoria e le funzioni di controllo della logica devono essere attive prima che tutti i dispositivi arrivino al power-up del sistema. Gestire questa funzionalità significa poter controllare la sequenza di accensione di tutti i dispositivi e assicurarsi che avvenga in maniera corretta. La memoria Flash, integrata nella PLD, consente a questa di “risvegliarsi” in meno di 1ms e di implementare tranquillamente questa funzione di “instanton”. Solitamente la PLD si alimenta da una tensione ausiliaria che deve essere la prima ad essere attiva e l’ultima a spegnersi. Tale tensione è solitamente di 3.3V, e, se la CPLD tollera tale tensione senza necessità di regolatori esterni, sicuramente ciò rappresenta un vantaggio. Al pari della crescita dei compiti assegnati alle PLD, crescono sempre di più anche gli I/O di cui queste necessitano per i loro compiti. Le PLD, dunque, permettono di gestire un numero elevato di segnali verso gli altri dispositivi della scheda, come da richiesta per la nostra piattaforma, in più le possibilità aumentano se si sfruttano anche i pin di microcontrollore e ASSP. I progettisti nel collegare tutti i dispositivi della piattaforma incontrano il problema delle diverse tesioni operative. Per esempio, il microcontrollore deve interfacciarsi con periferiche come ASSP, ASIC, memoria e LED che operano a tensioni differenti. Per rendere possibile l’interfacciamento, è necessario usare dei traslatori di livello, oppure si può sfruttare la PLD che in molti casi risulta più economica di parecchi traslatori di livello discreti. Infatti le PLD possono sfruttare differenti livelli di tensione nel range da 3.3V a 1.2V (figura 2).

Figura 2: traslazione di livello utilizzando la PLD.

Spesso in un sistema è necessario far dialogare dispositivi con differenti interfacce.

Per esempio, dispositivi I2C con dispositivi SPI, per far ciò l’ideale è utilizzare una PLD come ponte tra le interfacce. Si possono facilmente progettare o reperire blocchi già pronti per implementare le interfacce più popolari: I2C-bus controller, I2C-bus master controller, SPI-bus controller, UART, SRAM controller e compact Flash controller per la comunicazione tra un processore host e una periferica seriale tipo EEPROM o lettore di schede. La PLD ha diversi standard per gli I/O single ended, come LVTTL, LVCMOS e PCI in grado di operare a 3.3/2.5/1.8/1.2V e per gli I/O differenziali si può utilizzare lo standard LVDS in grado di effettuare un collegamento ad altissima velocità tipico di un backplane. Alcune PLD, poi, supportano l’emulazione di alcuni standard differenziali come LVPECL, RSDS e BLVDS. L’utilizzo di una PLD per la gestione di una piattaforma permette di incrementare il livello di integrazione della scheda, permettendo di integrare moltissima componentistica che altrimenti dovrebbe essere presente in forma discreta occupando spazio e incrementando i costi. Tutto questo senza privarsi del fatto di poter apportare modifiche senza necessariamente passare per il rifacimento della scheda. Molte PLD mettono a disposizione un meccanismo per realizzare un aggiornamento della loro programmazione da remoto, questo permette di apportare modifiche alla piattaforma, sopperire alle variazioni degli standard o inserire nuove funzionalità e, perché no, risolvere eventuali bug.

PLD LA SCELTA IDEALE PER LA GESTIONE DI UNA PIATTAFORMA HW

Messe a confronto con ASIC e ASSP, le PLD offrono significativi vantaggi di timeto-market e di flessibilità progettuale che li rendono ideali per essere impiegate per applicazioni di gestione delle piattaforme hardware. L’aspetto dei costi di NRE (Non-Recurring Engineering) è da tenere in considerazione se si utilizzano delle ASIC. Accade più di quanto non si pensi che un prodotto necessiti di essere modificato, anche solo perché è il mercato che lo richiede, se si utilizzano delle ASIC è necessario passare per una nuova progettazione con un incremento dei costi (costi di NRE). Utilizzare ASSP non ha costi di NRE elevati poiché lo stesso dispositivo è usato da parecchi utenti, tuttavia questi chip sono caratterizzati da specifiche molto restrittive necessarie per differenziare tra loro i vari prodotti sul mercato e non sempre soddisfano a pieno le richieste dei progettisti. Questi aspetti sono facilmente superabili con le PLD che possono essere agevolmente riprogrammate, garantendo anche la possibilità di introdurre modifiche dell’ultimo minuto o quando il prodotto è gia sul mercato.

TEMPI DI SVILUPPO E DI PROTOTIPAZIONE

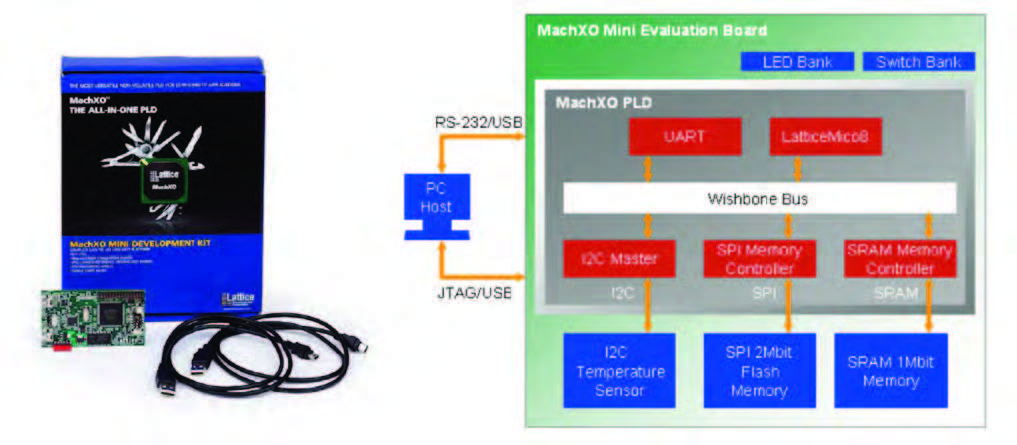

Ad aiutare i progettisti nello sviluppo con le PLD, la maggior parte dei produttori di questa tipologia di componentistica mette a disposizione kit di sviluppo e progettazione di riferimento. Questi strumenti forniscono al progettista la possibilità di accelerare i tempi di sviluppo richiesti per lo sviluppo della scheda. I kit di sviluppo (un esempio in figura 3) sono caratterizzati da schede di valutazione equipaggiate con una PLD e le più diffuse periferiche solitamente utilizzate: memorie, generatori di clock, display, ecc. Nel kit sono compresi cavi di programmazione e svariati progetti di esempio da cui trarre ispirazione. La maggior parte dei progetti è scritta in HDL e sono solitamente accompagnati da documentazione, file di progetto e sorgenti.

Figura 3: MachXO Mini Development Kit e scheda di sviluppo.

FACCIAMO UN ESEMPIO

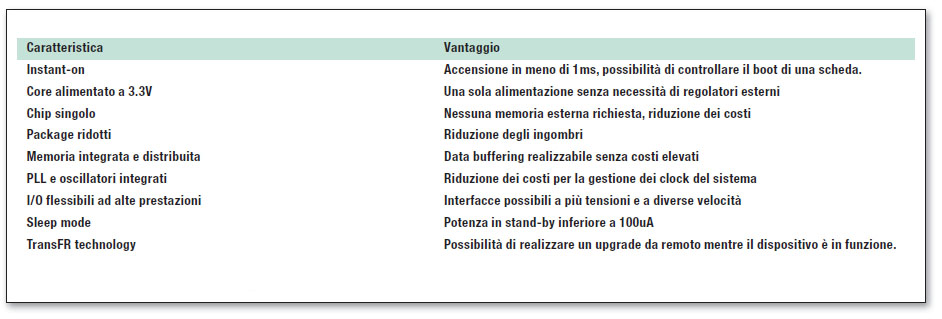

Torniamo alla nostra piattaforma server trattata in precedenza. Una PLD che si presta in maniera ottimale per questa applicazione è la famiglia MachXO della Lattice Semiconductor. Questa PLD combina una architettura ottimizzata a look-up table (LUT) con una tecnologia per la flash integrata a basso costo. Queste caratteristiche la rendono un componente ampiamente utilizzato nelle applicazioni dove è richiesta una PLD a bassa densità. Questa famiglia combina memoria Flash e SRAM permettendo il meccanismo dell’upgrade da remoto e permettendo, allo stesso tempo, un tempo di operatività dopo l’accensione bassissimo. Le diverse versioni della famiglia permettono di poter lavorare con tutte le tensioni da 3.3V a 1.2V. Nella tabella 1 sono riportati i punti chiave delle PLD della famiglia MachXO. Lattice mette a disposizione dei progettisti un kit denominato “MachXO Mini Development Kit”, una facile piattaforma a basso costo per sviluppare con questa PLD. Il kit arriva con la PLD già preprogrammata con un system-onchip che prevede anche un microcontrollore integrato, il LatticeMico8 (LM8). È possibile progettare o integrare IP con interfaccia Wishbone e le periferiche più diffuse SPI, SRAM e I2C. La scheda si può controllare agevolmente con sistemi Windows o Linux tramite un terminale su collegamento RS-232 o USB.

Tabella 1: caratteristiche della famiglia MachXO.