In questo articolo si proporrà una soluzione completamente digitale per estrarre il clock da un flusso di dati seriali codificati con un protocollo NRZ. Ovviamente, essendo completamente digitale potrà essere implementata agevolmente su FPGA.

La maggior parte dei collegamenti seriali integrano il segnale di clock nella trasmissione dei dati. Fondamentalmente è compito del ricevitore estrarre e riprodurre il segnale di clock. Nel corso dell’articolo approfondiremo il discorso su una realizzazione digitale dell’algoritmo di recupero dei dati e del clock per un segnale NRZ ad 1.5 Mbps.

Per realizzare l’estrazione del clock per la sincronizzazione del ricevitore, l’algoritmo viene implementato su FPGA, in particolare il dispositivo scelto è la Spartan XC3S200 (figura 5). La scelta del dispositivo non è stata fatta a caso in quanto Xilinx integra sui prodotti Spartan e Virtex i blocchi DCM (digital-clock manager), ottimizzati per applicazioni di questo tipo. Tuttavia, per rendere l’applicazione più generica possibile, si è deciso di utilizzare un algoritmo semplificato in grado di confrontare i fronti sul segnale dati con il clock generato internamente. Questo consente al progetto di essere integrato anche in una piccola CPLD o in una FPGA che non dispone dei blocchi DCM. In figura 1 si può vedere la rappresentazione grafica del funzionamento del blocco di estrazione del clock.

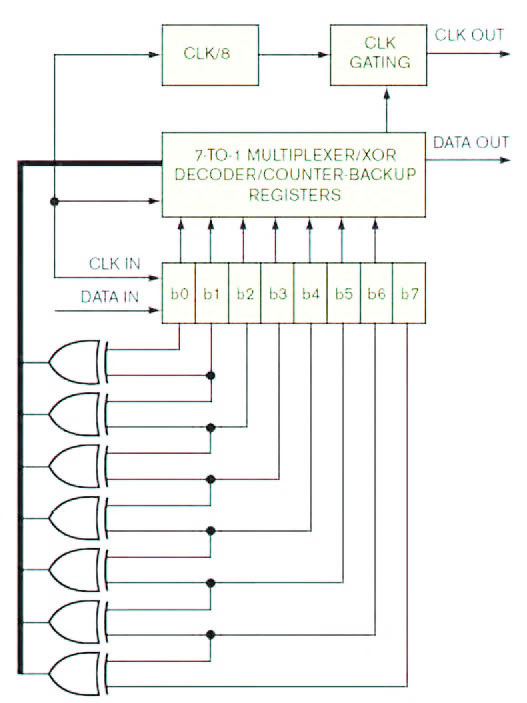

Figura 1: circuito di recupero del clock implementato in FPGA.

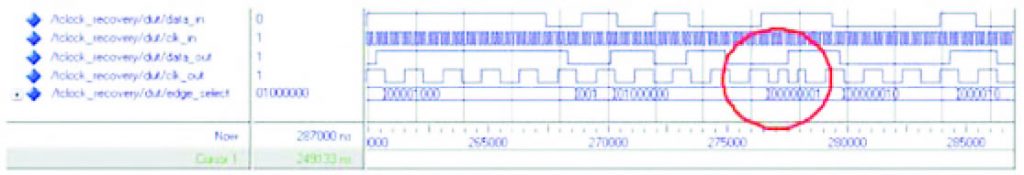

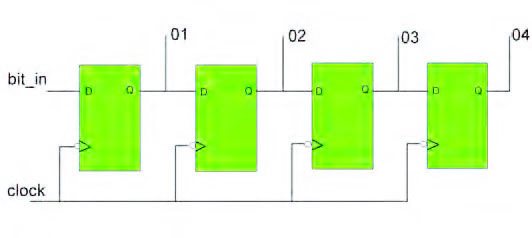

L’algoritmo utilizza un contatore freerunning a 3 bit per generare il clock di uscita, uno shift register a 8 bit (figura 6) per campionare il dato seriale in arrivo, 7 porte XOR per rilevare le commutazioni di livello ed infine un multiplexer con decodifica per portare l’ultimo bit dello shift register in uscita; questo blocco logico viene addizionato con alcuni registri con funzione di buffer. L’algoritmo lavora ad una velocità otto volte superiore allo strema di dati in ingresso, senza una relazione di fase tra il segnale di clock interno della logica ed il segnale dati in ingresso. Quanto detto si traduce nel fatto che dopo otto cicli di clock lo shift register contiene un fronte di salita del segnale dati oppure un fronte di discesa o ancora nessun fronte se i dati rimangono costanti in ingresso. Il multiplexer non contempla i casi in cui non si verifichino fronti o nei quali i fronti siano più di uno. Il piazzamento esatto del fronte viene individuato nello shift register utilizzando le porte XOR, che confrontano rispettivamente bit 0 e bit 1, bit 1 e bit 2, e così via fino a bit 6 e bit 7. Quando tra i due bit in ingresso alla porta XOR c’è una differenza di livello, allora il segnale d’uscita è a livello logico alto, permettendo così di individuare il verificarsi di un fronte sul segnale d’ingresso. In base a quale segnale delle porte XOR pilota il multiplexer, un determinato bit dello shift register viene multiplexato in uscita. Quest’azione assicura che il clock in uscita commuti sempre in corrispondenza della metà del bit di dati in entrata. Quando esistono differenze di velocità tra i segnali di clock e i segnali dati in ingresso, per esempio nel caso di bitter sul clock o di tolleranze abbondanti sugli oscillatori, la fase del segnale d’ingresso cambia rispetto alla fase del clock in uscita. Questo algoritmo individua queste situazioni e tenta di seguire la variazione di fase del segnale dati. In alcuni casi il multiplexer può ritrovarsi in una situazione di overflow, ossia quando il bit 7 dello shift register viene proposto in uscita dal multiplexer. In seguito ad una variazione di fase del segnale in ingresso, il multiplexer potrebbe commutare in uscita il bit 1, o viceversa. Se il bit 7 è il primo ad essere fornito in uscita (significa che l’array di XOR produce il byte 0100 0000) e successivamente si passa a fornire il bit 1 (con l’array di XOR che genera 0000 0001) un improvviso cambiamento di fase si determina sull’uscita dati. Tale cambiamento di fase è pari a –315° (ossia 360° x 7/8). Poiché il bit successivo di dati in ingresso deve essere ancora shiftato completamente, all’interno dello shift register è necessario generare un doppio clock in uscita, evitando così che il registro perda l’arrivo di un bit. Questa situazione è raffigurata in figura 2.

Figura 2: il raddoppio del clock in uscita previene una variazione di fase all’indietro.

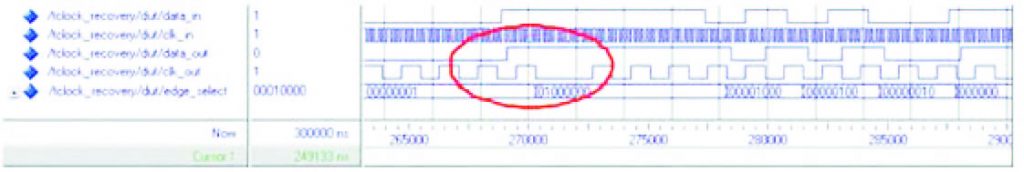

Al contrario, quando la fase del segnale in ingresso cambia il suo segnale d’uscita, imponendo al multiplexer di passare dal bit 1 al bit 7, il cambiamento di fase è di 315° (in questo caso positivo). Poiché il bit 7 dello shift register è una versione ritardata dell’ultimo bit b1 appena portato in uscita allineato al clock, sarà necessaria una situazione di stallo per un ciclo, altrimenti ci si ritroverà un bit in più in uscita. La situazione è riprodotta in figura 3.

Figura 3: un ciclo di riposo del clock previene una variazione di fase in avanti.

Per le due situazioni di gestione dell’overflow, la manipolazione del segnale di clock si può realizzare con della semplice logica combinatoria. Sul sito della Xilinx è disponibile l’application note xapp224 che discute un metodo molto simile a quello qui applicato. Rispetto all’algoritmo appena discusso, quello proposto da Xilinx non utilizza un contatore a 3 bit per suddividere il periodo del segnale dati in ingresso, ma genera semplicemente due segnali di clock sfasati di 90° sui quali, in corrispondenza dei 4 fronti (salite e discese), si va a campionare il segnale d’ingresso e lo si immette in una sequenza di flip-flop (shift register); i fronti vengono sempre individuati con delle porte XOR e una logica realizza in vhdl il data recovery. Il progetto può essere scaricato dal sito web della Xilinx al seguente indirizzo: ftp://ftp.xilinx.com/pub/applications/xapp/xapp224.zip .

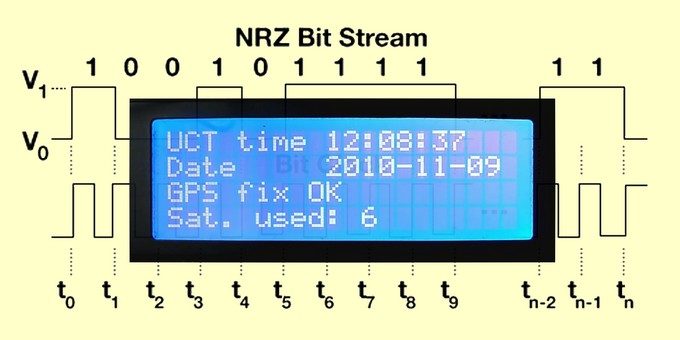

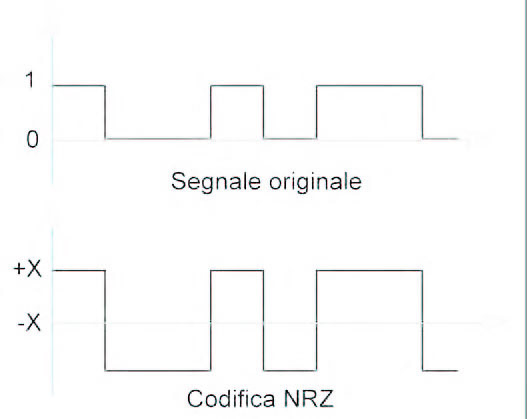

Figura 4: codifica NRZ.

Figura 5: uno Spartan XC3S200.

Figura 6: shift register.

Codifica NRZ

La codifica NRZ (figura 4) significa No Return to Zero, ossia Non Ritorno a Zero; è stato il primo sistema di codifica, ed anche il più semplice. Esso consiste semplicemente nel trasformare gli 0 in -X e gli 1 in +X; in questo modo si ha una codifica bipolare nella quale il segnale non è mai nullo. Di conseguenza, il ricevente può determinare la presenza o meno del segnale. L’impulso così ottenuto contiene molta più energia di un segnale con codifica RZ, costretto invece a ritornare al valore logico –X dopo il fronte del segnale di clock sincronizzato con i dati. Per il segnale NRZ non esiste uno stato di reset ed è tipicamente utilizzato per codifiche auto sincronizzanti, ossia si trasmette il solo segnale di dati ed il ricevitore ne estrae il clock.

Grazie per l’articolo, è interessante avere una dimostrazione di come agisce un algoritmo di clock recovery da dati seriali, nonché informazioni su altro materiale reperibile. Nei sitemi embedded, forse uno dei principali bus dati che utilizza un clock “embeddato” nella serie dati è il PCIe; sulla linea di questo articolo, sarebbe bello avere altri articoli su questo tipo di bus, magari con progetti VHDL, che come in questo caso aiutano notevolmente l’apprendimento!