La crescente diffusione di applicazioni di imaging e infrastrutture wireless nel mercato consumer ed industriale richiede lo sviluppo di soluzioni hardware ad elevate prestazioni. Il TMS320C64+, in particolare, è il modello di punta della famiglia C6000 di processori DSP fixed-point di Texas Instrument.

Basato sulla terza generazione dell’architettura VLIW VelociTI di TI, realizzato in tecnologia a 65 nm e dotato di una capacità di calcolo di 9600 milioni di istruzione per secondo ad una frequenza di clock di 1.2 GHz, disponibile in range di temperatura esteso [-40;+100] °C, costituisce una soluzione interessante ed economica per applicazioni DSP high-end.

ARCHITETTURA INTERNA

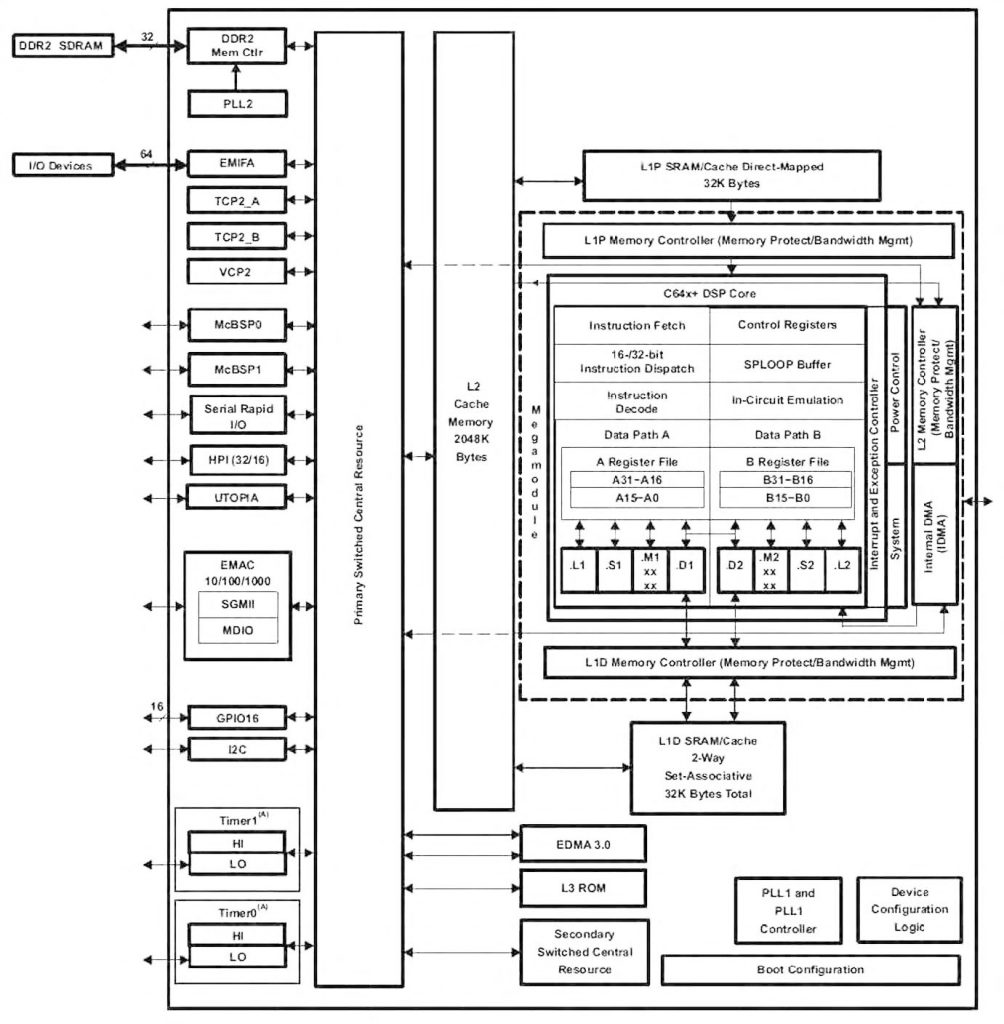

La figura 1 mostra uno schema di principio dell’architettura dei DSP TMS320C64+.

Figura 1: architettura dei DSP TMS320C64+.

Il cuore del dispositivo è la CPU C64x+, dotata di otto unità di processing, due register files e due data path distinti, porta di configurazione, controller DMA interno, reset/boot controller (sono supportate le modalità public e secure), interrupt/exception controller, power-down controller e timer free-running a 32-bit; una descrizione dettagliata della struttura della CPU e delle sue funzionalità è riportata nel paragrafo seguente. Tra le periferiche principali presenti a bordo dei DSP TMS320C64+, vi sono poi un controller EMAC/MDIO con interfaccia SGMII per applicazioni Gigabit Ethernet, una porta UTOPIA, interfaccia Serial RapidIO, due porte seriali multi-canali McBSP, una porta I2C, un controller EMIFA a 64 bit per dispositivi di I/O asincroni e sincroni, una porta HPI configurabile per l’accesso di un processore host esterno alle risorse interne del dispositivo, un controller per memoria DDR2 a 32 bit. L’interfaccia Serial RapidIO, in particolare, è compatibile con le specifiche RapidIO Interconnect Specification V1.2 (Errata 1.2) e Physical Layer 1x/4x LP-Serial Specification V1.2 adottando un livello di segnale CML differenziale e supportando un data rate di fino a 3.125 Gbps nelle modalità 1x/4x. Sono supportate (come unità slave) le operazioni di read, write, write con risposta, streaming write ed atomiche previste dallo standard con device ID ad 8 e 16-bit, indirizzamento a 34 bit e payload dati di fino a 256 byte. La porta UTOPIA (compatibile con la specifica Level 2) implementa invece un controller ATM con supporto per funzionalità slave con interfaccia ad 8-bit e clock di 50 MHz per applicazioni di trasmissione e ricezione dati high-speed. L’interfaccia McBSP supporta comunicazione sincrona fullduplex, con schemi di framing e clocking indipendenti per le sezioni di trasmissione e ricezione; compatibile con i dispositivi, ad esempio, AC’97, SPI, IIS ed IOM-2 supporta fino a 128 canali e larghezze di parola da 8 a 32 bit. Tre coprocessori dedicati presenti nei DSP TMS320C64+ assicurano prestazioni elevate per le funzionalità di decodifica di canale nelle applicazioni in ambito telecomunicazioni, audio/video e wireless. VCP2 è un decoder Viterbi con supporto per lunghezze di vincolo k = 5,6,7,8, 9 e rate R= 3/4, 1/2, 1/3, 1/4 ed 1/5 in grado di decodificare in tempo reale oltre 694 canali audio adattativi multi-rate a 7.95 Kbps. TCP2_A e TCP2_B sono invece decoder Turbo con supporto per applicazioni 3GPP e 3GPP2. La memoria on-chip dei DSP TMS320C64+ include due cache (configurabili anche come RAM mapped) di livello 1 di 32 Kbyte, distinte per dati e programma, accessibili alla sola CPU; la prima è di tipo 2-way set-associativa mentre la seconda di tipo direct-mapped. La cache di livello 2 di capacità 2048 Kbyte è invece comune ed accessibile anche alle altre periferiche, come pure una ROM L3 da 64 Kbyte. Un controller DMA dedicato EDMA con supporto per fino a 64 canali indipendenti assicura trasferimenti memoria-memoria senza intervento della CPU. Periferiche, unità di elaborazione e banchi di memoria sono connessi mediante una matrice di routing on-chip che assicura trasferimenti dati concorrenti, ridotta latenza, arbitraggio nell’accesso alle risorse. La matrice, che opera a una frequenza pari ad un terzo di quella della CPU, consiste di una Data SCR (Switched Central Resource) bus ed un Configuration SCR bus. Il primo, con parallelismo di 128 bit, è usato prevalentemente per trasferimenti dati mentre il secondo, a 32-bit, per la configurazione delle periferiche. La CPU C64x+, i controller Serial RapidIO, HPI, EMAC ed EDMA3 accedono alla matrice SCR come master, mentre le restanti periferiche dispongono di sola interfaccia slave.

CPU MEGAMODULE C64X+

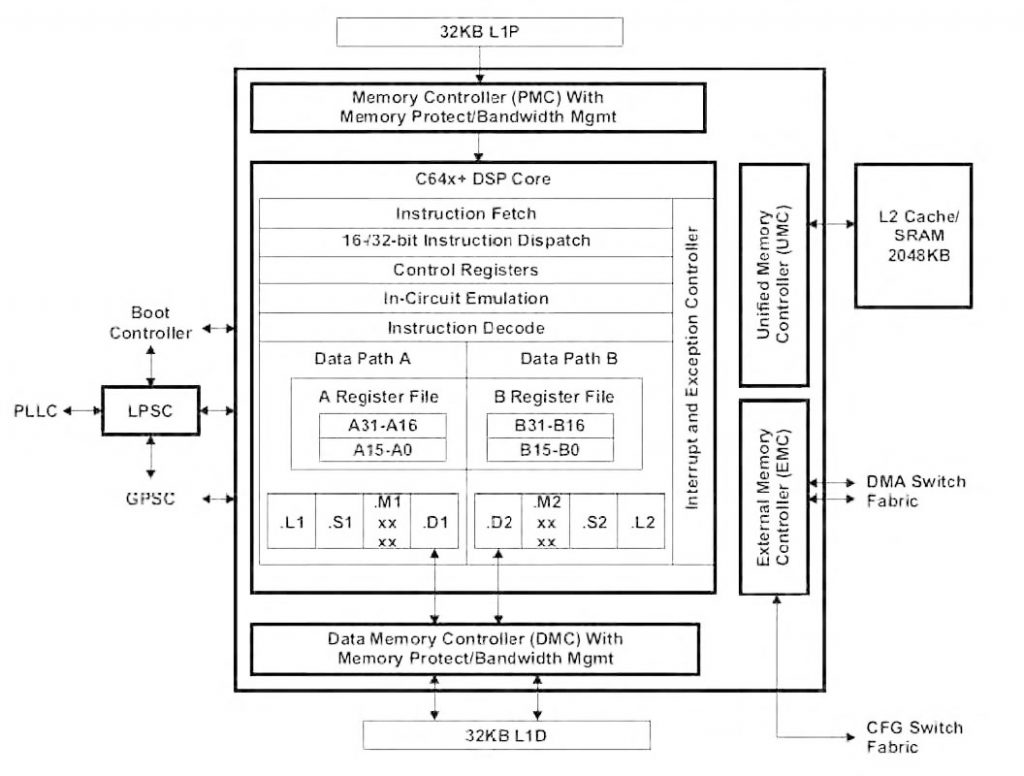

La figura 2 mostra uno schema di dettaglio della struttura interna della Megamodulo C64x+ dei DSP TMS320C64+.

Figura 2: dettaglio dell’architettura della CPU Megamodule C64x+.

La CPU C64x+ include due sezioni, ognuna avente quattro distinte unità funzionali ed un register file indipendente. I due register file sono quindi connessi mediante un cross path che consente ad una qualsiasi unità in una sezione di accedere ad un operando sorgente correntemente presente nel register file della seconda. Ogni register file consiste di 32 registri a 32-bit. E’ implementato un insieme VLIW di istruzioni a 32-bit che include operazioni aritmetiche fixed-point su tipi con risoluzione fino a 40 bit, istruzioni dedicate a 64 bit, operazioni di moltiplicazione complessa, packing, sorting e manipolazione di bit. I dati supportati sono di tipo 8-bit packed, 16-bit packed, 32-bit, 40-bit e 64-bit; per i tipi a 32/64 bit è consentito accesso in memoria in modalità non alligned. La CPU dispone di porta a 256 bit per l’accesso in sola lettura alla memoria programma interna e di due porte a 256 bit per l’accesso in lettura ed in scrittura alla memoria dati. Integra un buffer dedicato per la gestione del pipeling in software dei loop dell’applicativo che permette l’esecuzione in parallelo delle diverse istruzioni del ciclo. La pipeline è strutturata in tre stadi : fetch, decode ed execute. Gli stadi di fetch e decode richiedono, rispettivamente, quattro e due cicli per una qualsiasi istruzione mentre il tempo di esecuzione della stessa (fino ad un massimo di 5 cicli) dipende dalla particolare ope-razioni. Le unità funzionali possono comunque eseguire istruzioni in parallelo. Sono di tipo .M, .L, .D ed .S. Le unità di tipo .M, ad esempio, supportano istruzioni standard per l’esecuzione di una sola moltiplicazione tra operandi a 32 bit (o di fino a 4 moltiplicazioni in parallelo tra operandi a 16 bit) ed istruzioni dedicate di moltiplicazione sui campi di Galois per applicazioni nel settore della comunicazione digitale. Oltre alla CPU C64x+, come si vede dalla figura 2, il Megamodulo C64x+ dei DSP TMS320C64+ di TI include il controller delle cache di livello 1 e 2, un controller DMA interno per i trasferimenti dati tra queste e verso la porta di configurazione, l’interrupt controller, un controller per la modalità di power-down e l’Extended Memory Controller per l’accesso alle restanti periferiche presenti all’interno del dispositivo. I controller di memoria cache supportano funzionalità di controllo di banda (al fine di evitare che un agente monopolizzi l’accesso alla risorsa) e di protezione della memoria. La memoria è partizionata in pagine ad ognuna delle quali è associato un insieme di permessi che ne determinano le modalità di accesso; i diversi processi software possono essere quindi eseguiti in modalità supervisor od utente. Nella particolare modalità freeze, poi, è in generale preclusa l’allocazione di nuove linee in memoria cache in caso di read miss ed è inibita l’invalidazione di linee presenti nella cache stessa; tale funzionalità è spesso utile in applicazioni realtime, ad esempio, nel contesto della gestione delle interruzione. A livello 1, la cache istruzioni supporta operazioni di coerenza program-initiated; la cache dati risulta invece sempre coerente con l’attività del controller DMA sulla RAM L2. La cache di livello 2 è di tipo 4-way set-associative. L’Interrupt Controller supporta fino a 128 diverse sorgente di interruzioni, vettorizzate e mascherabili oltre agli eventi non mascherabili e di reset. La CPU C64x+ dispone di 12 linee di interruzione associabili direttamente ad altrettanti ingressi dell’Interrupt controller od a combinazioni di questi (fino ad un massimo di 4 combinazioni diverse di 32 interruzioni) e di una linea di eccezione, anch’essa associabile a combinazioni di eventi nell’Interrupt Controller. Il power-down controller assicura una gestione dinamica della potenza assorbita dal DSP TMS320C64+, consentendo di disabilitare sezioni del Megamodulo non utilizzate; ovviamente, le periferiche presenti nel dispositivo possono a loro volta essere disabilitate mediante istruzioni dedicate. La memoria cache L1 è disabilitabile in fase di configurazione hardware ed è disabilitata dinamicamente durante l’esecuzione dell’istruzione SPLOOP. La memoria cache L2 è disabilitabile mediante istruzione software come lo sono pure la sola CPU e l’intero Megamodulo.

PIATTAFORME DI SVILUPPO

Per valutare prestazioni e caratteristiche dei DSP TMS320C64+, TI rende disponibili a costi contenuti la scheda di sviluppo TMS320C6457 Lite EVM (figura 3).

Figura 3: la scheda di sviluppo TMS320C6457 Lite.

Realizzata con fattore di forma AMC single wide, il kit include il processore DSP C6457 (nella versione con frequenza di clock massima 1 GHz) con 256 MByte di memoria DDR2 ed emulatore JTAG on-board (accessibile mediante connettore mini-USB). Sono disponibili, per connessioni esterne, le porte Ethernet, McBSP e GPIO, oltre ad un header per Trace Pod. Il kit è distribuito unitamente ad una versione specifica per esso dell’IDE Code Composer. Una libreria di supporto software consente lo sviluppo di applicazioni in breve tempo; la disponibilità degli schemi elettrici e dei file gerber del circuito stampato semplifica la realizzazione di schede proprietarie. Per applicazioni più complesse è anche disponibile la versione TMDXEVM6457 EVM, che dispone a bordo di due dispositivi DSP C6457 interconnessi mediante interfaccia Ethernet e Serial RapidIO.