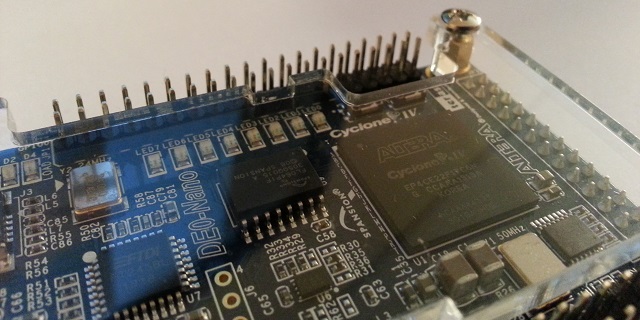

Ci siamo immersi in un mondo meraviglioso chiamato FPGA. Abbiamo conosciuto i linguaggi HDL (VHDL e Verilog). Abbiamo chiamato in causa i maggiori vendor di FPGA e i loro tool di sviluppo. Abbiamo esplorato un po’ più nel dettaglio Quartus II, Megawizard, QSys e Nios II. Abbiamo acquistato ed acceso la De0-Nano board. Ora non manca che una cosa: mettere insieme i pezzi e porre le basi per iniziare a creare qualcosa di davvero divertente!

ATTENZIONE: quello che hai appena letto è solo un estratto, l'Articolo Tecnico completo è composto da ben 1979 parole ed è riservato agli ABBONATI. Con l'Abbonamento avrai anche accesso a tutti gli altri Articoli Tecnici che potrai leggere in formato PDF per un anno. ABBONATI ORA, è semplice e sicuro.

A breve mi arriverà una nuova fpga (la stesa tua). Non vedo l'ora di applicare tutto quello che ho letto.

Bellissimo articolo, come sempre.

Grazie mille!!!!

Grandioso, sono felice di averti invogliato a tal punto 🙂 Fammi avere aggiornamenti, mi raccomando!

Sempre più voglia di avere un mio FPGA!

Grazie mille Tiziano per l’articolo, sto seguendo i tuoi articoli sulle FPGA. Però non trovo i sorgenti “in allegato” devo andare dall’oculista oppure durante il travaso di piattaforma son spartiti alcuni link? E’ possibile che vengano resi disponibili nuovamente per favore? Perché ci sono alcune cose non chiare, che magari basta avere il progetto quartus davanti per capire al volo.

Comunque ho provato a svolgere l’esercizio dello scorso articolo (Prequel di questo, dove abbiamo generato il file in Verilog dal System Builder) e fin qui tutto bene. Ora però vorrei sollevare un piccolo problema, magari si tira fuori qualcosa di buono 🙂

Oltre alla de0-nano ho ordinato anche la famosissima ed appetibile Camera D5M. L’intento è quello di approfondire la branca della Computer Vision attraverso un FPGA. Come primo progettino da cui partire volevo catturare l’immagina dalla camera per vedere se nella matrice ottenuta ci fosse una cifra da 0 a 9 e, una volta riconosciuta, “stamparla” mediante gli 8 led che ho a disposizione. Ma qui nascono i problemi:

1) nei listati dimostrativi della D5M non sono presenti quelli per la DE0-NANO

2) I listati disponibili sono tutti scritti in verilog 🙁 e siccome vorrei scrivere tutto in VHDL la domanda che sorge spontanea è: Come diamine faccio a leggere lo stream in VHDL?

Scusa il testamento, ma ho proprio perso la bussola, spero di cavarne piede, anche perchè secondo me potrebbe essere un bel vaso di pandora 🙂

Allegati inseriti. Grazie della segnalazione 🙂

Mi sembra di capire che i tuoi problemi siano di difficile risoluzione… Terasic, da quel che ho potuto capire, rilascia solo codice Verilog. Questo vuol dire che potresti tradurlo tu in VHDL. Sarà certamente un’esperienza che di dona un’arma in più per il futuro. Per quanto riguarda la CAM, ho come l’impressione che sia cambiato qualcosa nelle specifiche… Non trovo la compatibilità con la De0-nano. Eppure ricordo di averla vista. Hai verificato sul sito di Terasic prima dell’acquisto?

Si Tiziano, allora sul sito la d5m (che sarebbe la camera) risulta compatibile. Addirituttura su youtube circola un video della terasic proprio, dove fanno vedere “quanto è figa” la de0-nano. infatti colegano ai due GPIO sia la camera che il monitor di cui tu parlavi. Ma sia sul CDROM con gli esempi della DE0-nano sia su quello della D5M non ci sono esempi con la DE0-nano. Però nel SystemBuilder della DE0-nano mi fa configurare (per la piedinatura) la D5M senza alcun tipo di problema. L’unica fregatura stà nel verilog 🙁 Da un punto di vista di progettazione, credo di aver capito che bisogni leggere dai piedini D[11:0] seguendo il fronte di salita del clock della camera.. Un frammento del codice verilog è questo

//D5M image capture

CCD_Capture u3 ( .oDATA(mCCD_DATA),

.oDVAL(mCCD_DVAL),

.oX_Cont(X_Cont),

.oY_Cont(Y_Cont),

.oFrame_Cont(Frame_Cont),

.iDATA(rCCD_DATA),

.iFVAL(rCCD_FVAL),

.iLVAL(rCCD_LVAL),

.iSTART(!KEY[3]|auto_start),

.iEND(!KEY[2]),

.iCLK(~D5M_PIXLCLK),

.iRST(DLY_RST_2)

);

però non capisco la notazione col punto. Vuol dire che chiama delle specie di funzioni? e poi da un punto di vista logico, visto che il flusso dati mi arriva in pacchetti che poi devo convertire in RGB e riassemblare, l’image recognition on demand conviene farla riga per riga o solo una volta che ho il frame completo?

Guarda, solo con un frammento mi resta un po’ difficile capire il codice, ma quello che vedo mi sembra un’istanza di un component, cioè di un modulo che si chiama CCD_Capture e si dovrebbe trovare nella cartella di progetto. Quelle istruzioni con il punto dovrebbero essere le assegnazioni delle varie porte. Spero di esserti di aiuto, altrimenti mandami una parte di codice più grande, e vedrò di aiutarti meglio.

Per il resto, premetto che non sono esperto in imaging, però mi viene in mente che conviene farla una volta che si ha il frame completo, a meno che non sia una quantità eccessiva di informazione. Ma dipende anche da che tipo di operazione devi fare sull’immagine.

Ciao

Tiziano