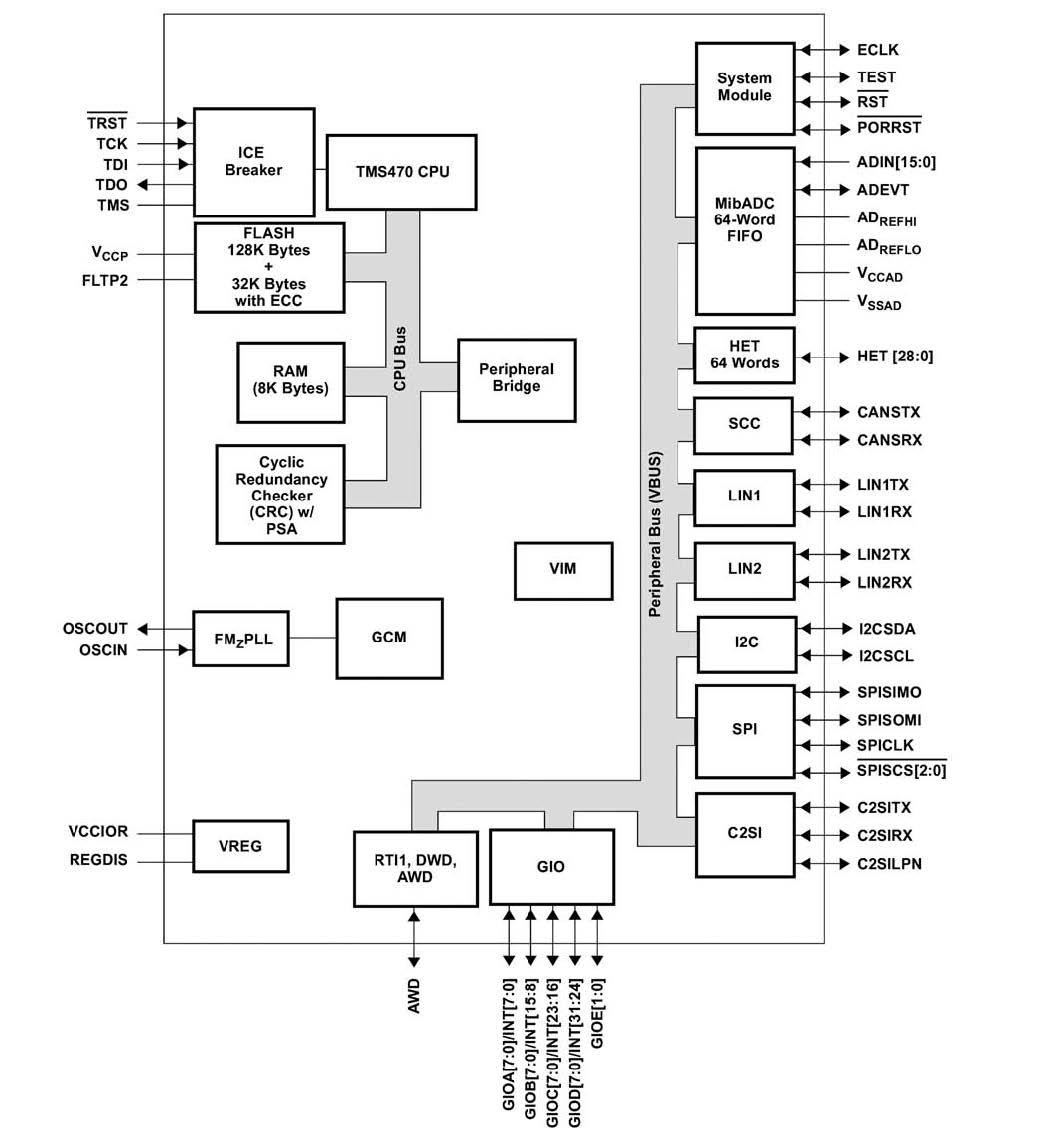

TMS470 è la famiglia di microcontrollori per applicazioni automotive sviluppata da Texas Instruments. Basati su processore RISC ARM7TDMI a 32 bit, disponibili nelle versioni con memoria ROM o flash, i dispositivi integrano una serie di periferiche intelligenti che includono un coprocessore timer, convertitori analogico/digitali a 10-bit, interfacce di comunicazione seriali, watchdog.

La serie TMS470M, orientata ad applicazioni costsensitive, ad esempio, nel settore della sicurezza - come per la realizzazione di ABS e air-bag - si basa su CPU Cortex M3 ed utilizza un insieme di istruzioni Thumb2 che permette di avere la stessa densità di codice di un sistema a 16-bit con le prestazioni tipiche di una piattaforma a 32bit. Integra lo stesso insieme di periferiche della versione TMS470 per facilitare il riutilizzo di software ed applicativi. Di seguito è riportata la descrizione del coprocessore timer HET (High-End Timer) disponibile all’interno dei micro di queste famiglie.

Un coprocessore programmabile via software

L’High-End Timer è un coprocessore con funzionalità di timer intelligente per applicazioni real-time. Dotato di 32 canali di ingresso/uscita di cui 24 con supporto per applicazioni ad alta risoluzione temporale (HR) è basato su una micro-machine programmabile via software; supporta un insieme ridotto di istruzioni che include tra l’altro operazioni di comparazione, input capture, output compare, addizione e shift. L’HET esegue ciclicamente una sequenza predefinita di istruzioni per generare forme d’onda più o meno complesse sulle porte di uscita. Semplici istruzioni di conteggio, ad esempio, consentono di creare timer virtuali multipli; combinazioni opportune di queste e di operazioni di confronto realizzano invece controlli PWM. La sequenza di istruzioni è contenuta in una memoria dedicata inizializzata al power-up dalla CPU. Le istruzioni sono di tipo VLIW (Very Long Instruction Word), codificate in parole da 96 bit che includono i campi program, control e data che specificano rispettivamente il codice dell’istruzione da eseguire e l’indirizzo della successiva operazione, i parametri di configurazione dell’istruzione e l’eventuale operando sorgente in memoria. La micro-machine dell’HET preleva l’istruzione da eseguire dalla memoria, decodifica ed esegue questa, opera un accesso write-back in memoria ove previsto e contemporaneamente precarica l’istruzione successiva. Le istruzioni operano su operandi sorgente e destinazione in memoria e nel registro; sono previsti due registri a 20 bit ed 1 a 25 bit. L’insieme di istruzioni include 21 operazioni descritte brevemente nel box di pagina 45.

Il numero medio di cicli di clock per istruzione (average CPI time) è 1.3, misurato su diversi complessi benchmark; la maggior parte delle istruzioni esegue in un singolo ciclo di clock. La sequenza di istruzioni che l’HET esegue è auto-controllata, come visto in precedenza, grazie alla definizione dell’indirizzo della successiva operazione da eseguire in uno dei campi di quella attuale; l’HET non prevede quindi un registro Program Counter ma supporta comunque semplici istruzioni di salto condizionato oltre alla possibilità di salto ad una definita locazione in corrispondenza di eventi su una delle porte di ingresso. L’HET esegue ciclicamente la sequenza di istruzioni con un periodo configurabile mediante programmazione opportuna di prescaler interni; tale periodo viene definito ‘loop resolution clock cycle’. Ovviamente, perché il sistema sia stabile, è necessario che il tempo di esecuzione della sequenza sia inferiore al periodo di ripetizione; questo impone delle costrizioni sulla lunghezza della sequenza e sulla risoluzione temporale del controllo. E’ possibile definire breakpoint in corrispondenza dell’esecuzione di una particolare istruzione per scopi di debug. In presenza di breakpoint l’esecuzione della micro-machine viene interrotta e viene inoltrata un’opportuna richiesta alla CPU. In tale modalità è possibile accedere ai registri di controllo dell’HET per determinare l’istruzione che ha causato l’interruzione. Sono previste fino a 32 diverse sorgenti di interruzione ognuna configurabile con uno tra due diversi livelli di priorità. In presenza di interruzioni multiple con lo stesso livello di priorità all’interno di un ciclo di esecuzione, viene eseguita la routine di interrupt corrispondente alla sorgente con identificativo più basso. In alternativa l’HET può essere forzato in modalità debug, arrestando così l’esecuzione delle istruzioni, direttamente da parte della CPU mediante segnale di controllo opportuno. L’HET è programmato in linguaggio assembler usando direttamente l’insieme di istruzioni. Quindi il listato viene compilato e tradotto in un codice C con il relativo file header che vengono infine inclusi nel progetto dell’applicativo per il microcontrollore. Il programma principale deve ovviamente prevedere una routine che inizializza la memoria dell’HET con la sequenza di istruzioni da eseguire.

Figura 1: struttura interna del TMS470.

Il seguente listato 1 mostra l’esempio di un semplice programma in assembler che, in una applicazione a bordo di un veicolo, genera un impulso in corrispondenza di una precisa posizione di una ruota (verificata mediante l’istruzione ACMP) ed avente una durata costante (specificata mediante l’istruzione MCMP) indipendentemente dalla velocità.

; Time Counter in register A

A0CNT{reg=A, max=0x0fffff}

; Angle Counter (320 degree) in register B

A1CNT{reg=B, max=0x3C00, irq=OFF, angle_count=ON, data=0x400}

; Angle compare to set pulse on CC23 when match X flag is set

A2ACMP{next=A3, en_pin_action=ON, cond_addr=A3, pin=CC23,action=SET, reg=B, irq=OFF, data=0x0220}

; Transfer match angle into time, when X is set transfer A into DF, switch in time mode and jump to MCMP else

next ; ACMP (next loop resolution)

A3SCMP{next=A6, en_pin_action=ON, cond_addr=A5, pin=CC23, action=SET, restart=ON, irq=OFF, data=0x0230}

; restart the sequence compare and jump to next resolution

A4MOV64{next=A6, remote=A3, en_pin_action=ON, cond_addr=A4, pin=CC23, comp_mode=SCMP, action=SET, reg=B, data=

0x0230}

; When T (= Reg. A - SCMP Data field) > compare value then reset the pin and jump to MOV64 to re-initialize

the SCMP Control and Data field.

A5MCMP{next=A6, en_pin_action=ON, pin=CC23, hr_lr=LOW, action= CLEAR, order=REG_GE_DATA, cond_addr=A4, reg=T,

data= 0x214, hr_data=0x10}

; Branch to first instruction (end of the loop)

A6BR{next=A0, cond_addr=A0, pin=CC25, event=NOCOND}

| Listato 1 |

Architettura

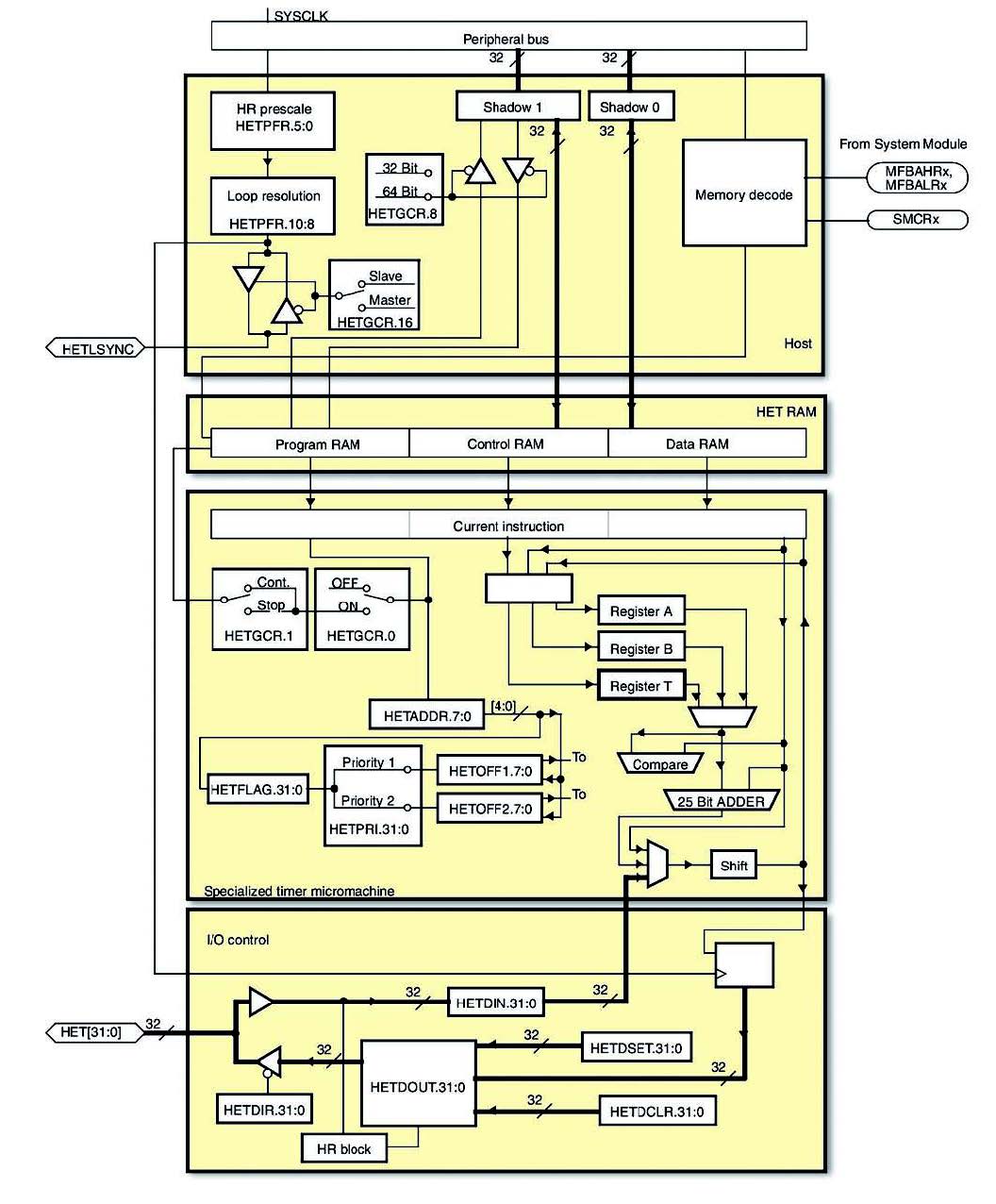

La figura 2 mostra uno schema di principio dell’architettura dell’HET che comprende le seguenti sezioni principali:

» interfaccia host

» timer RAM

» Micromachine

» Controller I/O

Figura 2: architettura dell’HET.

L’interfaccia host consente la comunicazione tra la CPU e la timer RAM dove è presente il codice che deve essere eseguito. Include una interfaccia dedicata verso il System Module, l’unità che consente alla CPU del microcontrollore di accedere alle periferiche mediante il bus di espansione (nell’architettura dei TMS470 un secondo bus è dedicato invece alla memoria dati e programmi). Dispone di 2 shadow register a 32-bit che permettono di accedere alla timer RAM senza interrompere l’esecuzione dell’HET; diversamente un accesso diretto alla memoria ferma l’esecuzione della micro-machine per due colpi di clock. Implementa il register file con i due registri a 20 bit e quello a 25 bit indicati in precedenza. Due prescaler di clock sono programmabili indipendentemente dall’utente; il primo, con risoluzione 6-bit, consente di derivare la frequenza di clock per i canali HR mentre il secondo, con risoluzione 3-bit e connesso in serie al primo, serve per definire il ‘loop resolution clock cycle’. L’HET è in grado di funzionare in modalità master o slave nel caso di applicazioni che utilizzino HET multipli e richiedano la sincronizzazione di questi. In modalità master il modulo genera in uscita un segnale di sincronizzazione per i prescaler delle periferiche slave. La timer RAM è una memoria a due porte in grado di sostenere accesso simultaneo in lettura e scrittura ad indirizzi differenti rendendo possibile il prefetch della successiva istruzione da eseguire durante l’ultima fase dell’operazione corrente anche nel caso in cui questa richieda un accesso write-back. Il parallelismo è di 96-bit corrispondente alla dimensione delle istruzioni; la CPU accede indipendentemente ai tre campi program, control e data. La profondità della timer RAM - corrispondente al numero massimo di istruzioni della sequenza - è 64 locazioni (espandibile fino a 256 in funzione del modello selezionato). L’HET è connesso, come abbiamo visto in precedenza, ad una porta a 32-bit; è possibile accede indipendentemente ad ogni linea in ingresso od uscita in funzione della istruzione correntemente eseguita. Mediante accesso ai registri di I/O dell’HET la stessa CPU può operare sulla porta. Le operazioni di I/O sono sincronizzate rispetto al periodo di esecuzione della sequenza così da evitare variabilità nelle modalità di aggiornamento delle uscite in funzione del ciclo di clock all’interno del loop (e quindi della posizione all’interno della sequenza) in cui l’istruzione viene eseguita.

L’INSIEME DI ISTRUZIONI DELL’HET

CMP (Angle Compare)

set/reset di un pin specifico quando il valore di confronto dell’angolo si trova tra il valore precedente del contatore e quello attuale.

ACNT (Angle Countde)

finisce un timer virtuale usato dopo le istruzione SCNT e APCNT per generare un base dei tempi angolare sincronizzata con un segnale esterno.

ADCNST (Add Constant)

estensione di ADM32.

ADM32 (Add Move 32)

modifica il registro dell’HET od il campo data all’indirizzo in memoria specificato. Il valore modificato risulta dall’addizione del campo data immediato o remoto e del registro o del campo data remoto. APCNT (Angle Period Count) usata prima delle istruzioni SCNT ed ACNT genera una base dei tempi angolare sincronizzata ad un segnale esterno.

BR (Branch)

esegue un salto all’indirizzo condizionale specificato in presenza di una determinata condizione di pin o flag. CNT (Count) definisce un timer virtuale in uno dei registri.

DADM64 (Data Add Move 64)

modifica i campi dato e controllo all’indirizzo remoto con i valori specificati; il nuovo campo dato viene calcolato sommando quello attuale a quello remoto.

DJZ (Decrement and Jump if - zero)

definisce un contatore virtuale di tipo down usato per l’esecuzione ritardata di certe istruzioni.

ECMP (Equality Compare)

esegue una specifica operazione su un determinato pin in funzione del risultato del confronto tra il valore specificato nel campo dato ed un certo registro.

ECNT (Event Count)

definisce un contatore virtuale usato come contatore di evento o accumulatore di impulso. MCMP (Magnitude Compare) confronta il valore specificato nel campo data con quello presente in uno dei registri. MOV32 (Move 32) sostituisce il valore di un registro e/o il campo dato all’indirizzo remoto specificato con un valore corrente.

MOV64 (Move 64)

modifica campo dato e controllo all’indirizzo remoto.

PCNT (Period/Pulse Count)

rileva un fronte su un pin esterno e misura periodo o durata.

PWCNT (Pulse Width Count)

definisce un timer virtuale usato per generare un impulso di durata variabile.

RADM64 (Register Add Move)

modifica campo dato, campo dato HR e campo controllo all’indirizzo remoto.

SCMP (Sequence Compare)

realizza alternativamente operazioni angle-based e timebased per generare sequenze di impulsi usando la base dei tempi angolo-riferita.

SCNT (Step Count)

definisce un timer virtuale usato dopo di APCNT e prima di ACNT per generare una base dei tempi angolo-riferita sincronizzata ad un segnale esterno.

SHFT (Shift)

esegue lo shift del campo dato dell’istruzione.

WCAP (Software Capture Word)

memorizza il registro selezionato all’interno del campo dato se la condizione specificata è verificata sul pin selezionato.