Il modulo Master Synchronous Serial Port di Microchip è utilizzato, nel nostro caso, per implementare due protocolli seriali utilizzati nella maggior parte delle applicazioni di tipo embedded: I2C bus e Serial Peripheral Interface, meglio conosciuto come SPI. In questo articolo, ultimo della serie "I2C Bus con Master Synchronous Serial Port" vediamo nei dettagli come il primo di questi diffusissimi protocolli sia stato integrato nella nuova famiglia di micro, l’Enhanced-Mi. Questo articolo, tratto dal numero 107 di Firmware, anno 2014, rientra tra i contenuti della Rubrica Firmware Reload contenente approfondimenti e articoli tecnici della passata rivista cartacea Firmware.

IMPLEMENTAZIONE IN MICROCHIP

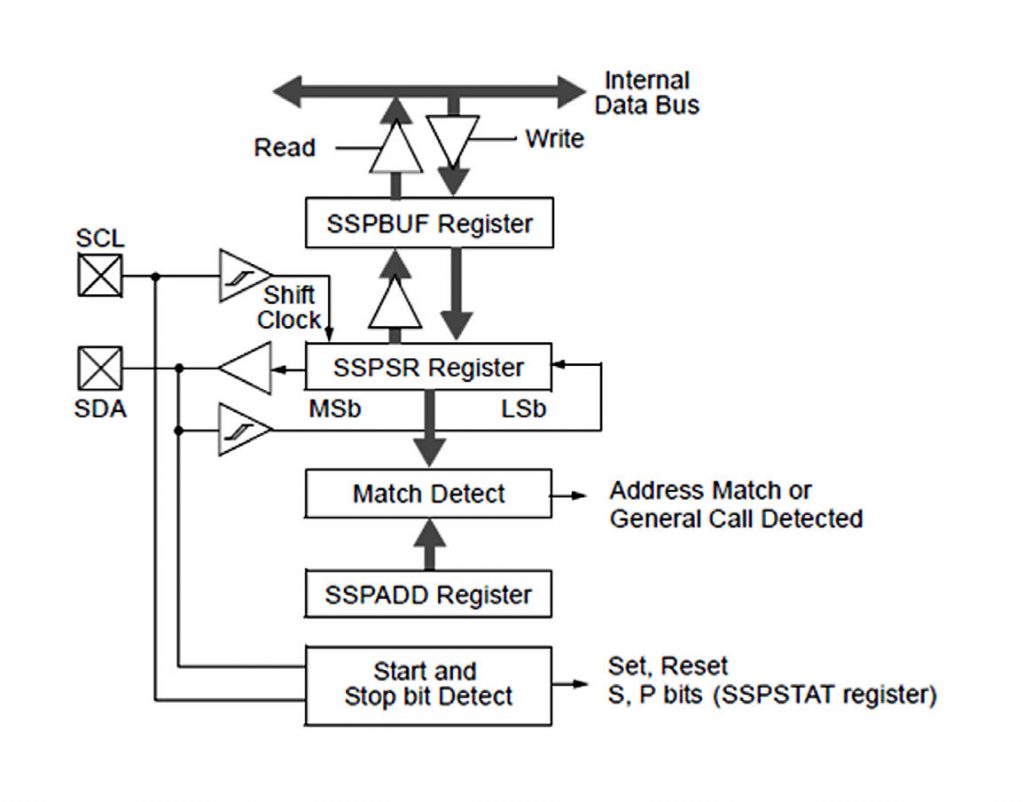

L’I2C bus è implementato nel microcontrollore Microchip tramite il modulo hardware definito come MSSP (Master Synchronous Serial Port), vedi Figura 1.

Figura 1: Schema a blocchi dell’MSSP

Dal diagramma riportato in figura si nota la presenza del registro di lavoro SSPBUF che ha lo scopo di fare da buffer tra il bus interno del microcontrollore e lo shift register SSPSR, necessario al trasferimento dei dati in modo seriale attraverso la linea SDA. Il clock che sincronizza la comunicazione è gestito dal modulo denominato Baud Rate Generator. Ricordiamo poi, dal momento che l’I2C bus è un protocollo bidirezionale, entrambe le linee di clock SCK e dati SDA sono predisposte per il passaggio di segnali in entrambi i sensi. La gestione della modalità I2C bus in ambito Microchip prevede l’uso di diversi registri identificati come SSPCON (registro di controllo del modulo MSSP, a volte anche denominato come SSPCON1), SSPCON2 (secondo registro di controllo e stato), SSPSTAT (registro di stato e controllo), SSPBUF (buffer bidirezionale), SSPADD (registro di indirizzamento, in slave, e impostazione velocità di trasmissione, Baud Rate Generator, in modalità master). Esiste anche un registro non accessibile al software denominato come SSPSR utilizzato come shift register per il registro SSPBUF.

Le condizioni di lavoro - start, stop e acknowledge - sono generate da un blocco la cui uscita risulta multiplexata con l’uscita dello shift register SSPSR verso la linea di uscita dati SDA. Un altro blocco si preoccupa di rilevare le condizioni di start, stop e collisioni all’interno del bus mandando a livello logico 0 o 1 alcuni bit dei registri di controllo e impostazione SSPSTAT, SSPCON e SSPCON2. Una tipica sessione di trasmissione in ambito I2C bus può essere così riassunta. Per prima cosa, il master controlla che le linee SDA e SCL per un tempo superiore al massimo periodo di trasmissione consentito dall’hardware, non sono attive (livello logico alto): in caso affermativo, lo stesso master invia alle periferiche il messaggio di start, SDA a livello basso quando SCL è alto. In seguito, il segnale per la sincronizzazione sulla linea SCL, il master invia l’indirizzo della periferica con la quale vuole comunicare e contestualmente richiede la tipologia di servizio, in altre parole lettura o scrittura. Il master attende poi la risposta da parte della periferica che nella chiamata ha riconosciuto il proprio indirizzo. Si ricorda che il bus deve essere però liberato se nessuna periferica risponde al segnale. In caso di periferica rilevata, il master inizia lo scambio dei dati con pacchetti da 8 bit di dati con un acknowledge per ogni pacchetto. Al termine della trasmissione, il master libera il bus inviando un segnale di stop. Per inizializzare il modulo SSP in modalità master, occorre interagire sui pin del registro SSPCON. Infatti, occorre lavorare sul bit 5, SSPEN, o Synchronous Serial Port Enable e Synchronous Serial Port Mode sui bit SSPM3:SSPM0. Intervenendo sul bit SSPEN si ottiene l’abilitazione della porta seriale e la configurazione dei pin SCL e SDA. Invece, intervenendo sui bit SSPM si decide la modalità di funzionamento del modulo I2C bus (con il binario 1000 si decide di selezionare la modalità master).

Nello standard I2C bus è il master che pilota e seleziona il clock e per farlo dobbiamo ricorrere al registro SSPADD che, oltre a definire l’indirizzo della periferica, è utilizzato in fase d’inizializzazione per fissare la frequenza di funzionamento del clock. Il registro SSPSTAT è di fondamentale importanza per utilizzare il bus correttamente; in effetti, occorre anche intervenire sul bit 7, SMP o slewrate control, con un valore pari a 1: in questo modo si disabilita il controllo dello slew rate e si costringe il componente a lavorare a 100 kHz (se volessimo lavorare a 400 kHz questo bit deve essere impostato a zero). Non solo, occorre anche intervenire sul bit 6, CKE o SMBus select, utilizzato per lavorare o meno in modalità compatibile SMBus. Terminata l’inizializzazione, occorre predisporsi per iniziare una sessione di lavoro. Per lavorare in I2C bus, il bus deve trovarsi in una condizione di idle o, in altre parole, non deve essere coinvolto in trasmissioni o ricezioni. Ecco perché abbiamo la necessità di controllare il registro SSPSTAT, bit 2, e SSPCON2, sui bit ACKEN, RCEN, PEN, RSEN e SEN. Qualora il bus fosse libero, allora il master può iniziare una sessione di lavoro, in altre parole deve occupare il bus e manifestare la sua intenzione a scrivere o leggere verso una periferica. Per occupare il bus, il master deve inviare una sequenza di start (impostando a 1 il bit 0 del registro SSPCON2): la linea SDA è portata a livello logico basso mentre SCL è a livello alto. A questo punto, il master deve comunicare con chi intende instaurare la comunicazione in scrittura o in lettura. Per farlo, occorre inserire l’indirizzo della periferica, su 7 bit, e impostare l’ottavo bit a 0 per segnalare se si intende scrivere un dato verso la periferica o con 1 se si manifesta la volontà di leggere. Il tutto è inserito nel registro SSPBUF. Il master, una volta inviato il tutto, deve ora attendere la risposta. La periferica che ha riconosciuto il suo indirizzo invierà un segnale di acknowledge sulla linea.

Questo segnale deve essere verificato controllando lo stato del bit 6 (ACKSTAT - Acknowledge Status) del registro SSPCON2: con un valore pari a zero si assume che la periferica ha gestito correttamente la richiesta e il master può proseguire la comunicazione. È chiaro che se il master intendesse utilizzare una periferica in scrittura, questo deve preoccuparsi, una volta ottenuto dallo slave il proprio acknowledge, di inviare il dato da scrivere, così come in lettura deve aspettare il dato dallo slave. È bene ricordare che il registro SSPBUF è utilizzato per ogni comunicazione con la periferica e che i dati sono sempre gestiti in pacchetti da 8 bit con un acknowledge tra gruppi di otto. È importante anche notare il ruolo del flag d’interrupt SSPIF: questo deve essere controllato nel processo di scambio dei dati per evitare conflitti in trasmissione. Per concludere la sessione di lavoro (bus in condizione idle), il master deve inviare la condizione di stop: questo è svolto intervenendo sul bit 2 del registro SSPCON2 seguito dall’acknowledge impostando a 1 il bit 4 sempre del registro SSPCON2. La condizione di re-start in Microchip può essere gestita impostando a 1 il bit 1 (RSEN) del registro SSPCON2.

CONCLUSIONI

È bene ricordare che il mondo Microchip è abbastanza variegato, con differenti proposte all’interno di ciascuna famiglia. Infatti, alcuni processori della serie 16 e appartenenti alla serie Enhanced possono vantare due registri aggiuntivi (SSPCON3 e SSPMSK) utilizzati per impostare caratteristiche avanzate. Altri, sempre inseriti nella famiglia Enhanced, vantano la presenza di due moduli MSSP (MSSP1 e MSSP2), indipendenti tra loro e configurabili individualmente. Insomma, le possibilità sono tante e consentono di configurare in modo flessibile ciascuna piattaforma di lavoro.

Leggi anche le puntate precedenti:

I2C Bus con Master Synchronous Serial Port - Parte 1 | Elettronica Open Source

I2C Bus con Master Synchronous Serial Port - Parte 2 | Elettronica Open Source