L’I2C è senza ombra di dubbio un’interfaccia digitale molto diffusa, utilizzata per la comunicazione a corto raggio tra differenti tipi di circuiti integrati. Basata su un bus composto da due soli fili, l’I2C è relativamente semplice da implementare e consente di raggiungere rate di trasmissione fino a 400kHz nella modalità fast. Tuttavia, come del resto avviene per qualunque altro tipo di standard, possono sorgere delle problematiche quando l’applicazione spinge fino al proprio limite le specifiche I2C originarie, oppure quando le stesse si dimostrano insufficienti a soddisfare i requisiti delle applicazioni più recenti. Con il crescere della complessità dei sistemi digitali, un numero sempre maggiore di dispositivi I2C viene collegato al bus, rischiando di compromettere alcuni parametri di funzionamento del sistema stesso.

Introduzione

Le problematiche più comuni derivanti dall’utilizzo dell’interfaccia I2C sono in genere legate alle caratteristiche elettriche, alla temporizzazione, e all’andamento dei segnali. Se si aumentano le dimensioni del sistema senza superare il limite di capacità del bus (pari a 400pF, richiesto per esigenze di compatibilità con i dispositivi I2C in obsolescenza oppure non noti), si può ad esempio causare il blocco del bus nello stato logico basso. Un altro tipo di problema può essere legato al numero insufficiente di indirizzi disponibili sul bus. Queste (ed altre ancora) sono problematiche tipiche che possono presentarsi ai progettisti I2C ed alle quali non è sempre facile trovare una soluzione. In questo articolo vedremo come i controllori I2C di Linear Technology siano in grado di risolvere uno o addirittura tutti questi problemi contemporaneamente, in modo tale che il progettista possa concentrarsi sull’attività di sviluppo del sistema, liberandosi dalle limitazioni e dalle insidie dallo standard.

Problemi di natura elettrica

Lo standard I2C prevede che la capacità massima del bus non ecceda il valore di 400pF. Tuttavia, la presenza delle piste conduttive, dei cavi di collegamento, e dei dispositivi stessi provoca un aumento di capacità del bus, che rende particolarmente difficile, soprattutto per i sistemi di grandi dimensioni, rimanere al di sotto del limite consentito.

Un altro problema tipico deriva dall’impossibilità di mescolare e abbinare allo stesso bus dispositivi con tensioni di alimentazione differenti. Non solo, alcuni sistemi richiedono anche l’inserimento e la rimozione dal backplane, “a caldo”, delle schede di I/O; senza le opportune precauzioni, queste azioni potrebbero corrompere l’integrità del backplane stesso. L’impossibilità di risolvere ognuno di questi problemi di natura elettrica potrebbe compromettere la conformità allo standard I2C, l’integrità dei dati, o persino l’affidabilità dell’intero sistema. Fortunatamente, l’introduzione dei buffer per bus I2C ha permesso di risolvere questi problemi basilari, fornendo al bus stesso funzionalità di bufferizzazione capacitiva, traslazione dei livelli e hot swap.

Con la continua crescita di complessità dei sistemi, sono sorte delle nuove problematiche di natura elettrica, ed è apparso evidente come i benefici apportati dall’introduzione dei buffer siano stati ottenuti compromettendo alcune specifiche del bus I2C.

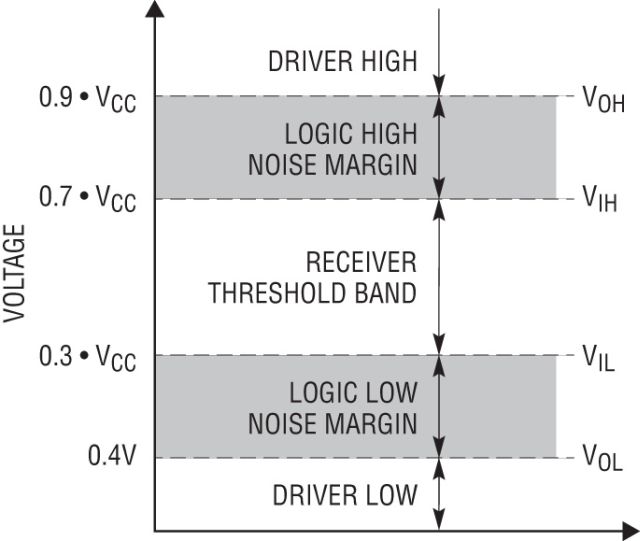

I buffer richiedono infatti un circuito che sia in grado di distinguere quando il bus viene portato allo stato logico basso da un driver esterno oppure dal driver del buffer stesso. Il risultato è che si sono realizzati dei buffer che o pilotano la tensione VOL al di sopra dei 0,4V previsti dalla specifica I2C, oppure pilotano la VOL utilizzando un offset. Aggiungendo sempre più buffer di questo tipo al bus, si comprime ulteriormente il margine di rumore nello stato logico basso, aumentando la suscettibilità al rumore.

I sistemi di dimensioni maggiori possono trarre enormi benefici impiegando un buffer quasi ideale, che sia in grado di ripristinare il margine di rumore nello stato logico basso al valore previsto dalle specifiche I2C, cioè un buffer veloce che rimanga attivo finchè le tensioni del bus non superino il valore 0,3VCC (VIL) e che non carichi il bus. Un requisito addizionale per i sistemi di grandi dimensioni è che essi siano retro-compatibili con i buffer i cui acceleratori del tempo di salita (RTA) si attivano al di sotto di 0,3VCC e con i dispositivi che pilotano una tensione VOL (non conforme allo standard) di 0,6V.

Nell'immagine seguente sono evidenziati i valori di tensione specificati per il bus I2C, nonchè le relative soglie di rumore.

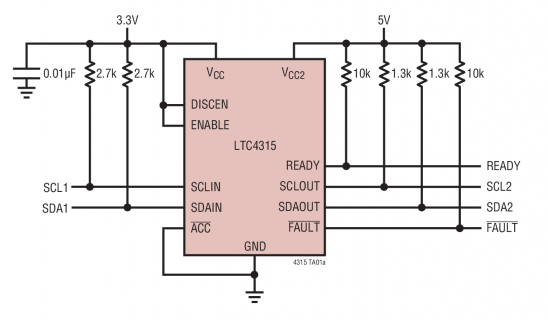

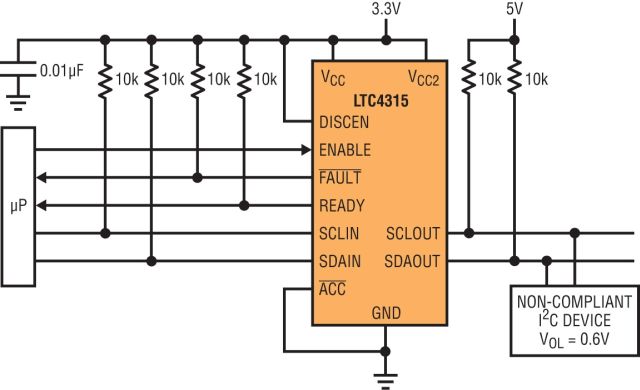

Nell'immagine seguente è mostrato il dispositivo LTC4315 di Linear Technology, un recentissimo buffer in grado di risolvere tutte le problematiche menzionate in precedenza. L’LTC4315 suddivide la capacità complessiva del bus in segmenti di dimensione inferiore, ciascuno con capacità <400pF, esegue la traslazione dei livelli del bus nel range di tensioni compreso tra 1,4V e 5,5V, e garantisce la funzionalità di hot swap, in modo tale che le schede di I/O possano essere inserite e rimosse dal backplane in sicurezza. Forse ancor più importante, l’LTC4315 garantisce una tensione VIL pari a 0,3Vcc, assicurando in tutte le condizioni un adeguato margine di errore nella soglia superiore dello stato logico basso. Di conseguenza, più dispositivi LTC4315 possono essere collegati in cascata, senza preoccuparsi della compressione dei margini di rumore, la soluzione ideale per sistemi di grandi dimensioni.

L’LTC4315 può anche interfacciarsi con dispositivi che pilotano una tensione VOL > 0,4V e con prodotti i cui RTA si attivino al di sotto di 0,3VCC; è così possibile realizzare un sistema senza conoscere o senza preoccuparsi di quali tipi di dispositivi I2C si collegheranno al bus.

Problemi legati alla tempistica

I sistemi basati sul bus I2C possono essere afflitti da due problematiche principali legate alla tempistica.

Anzitutto, i tempi di salita dei segnali I2C sono in genere determinati dalle resistenze di pull-up del bus, che talvolta si dimostrano inadeguate qualora venga richiesta una risposta rapida. Ciò avviene ad esempio per le specifiche PICMG, le quali richiedono che i entrambi i segnali SCL e SDA passino da 1V a 2,3V in 900ns con un pull-up di 2,7kΩ a 3,3V e una capacità di 690pF. Diversamente, l’elevata capacità del bus e la limitata corrente di pull-up possono allungare pericolosamente i tempi di salita dei segnali, sino al punto da violare il massimo tempo di salita previsto dallo standard I2C, cioè 1µs @ 100kHz oppure 300ns @ 400kHz.

Linear Technology offre un’ampia selezione di buffer con accelerazione del tempo di salita selezionabile, come l’LTC4315, ma anche acceleratori del tempo di salita stand-alone, come l’LTC4311, che consentono di soddisfare le tempistiche del bus più restrittive. Questi acceleratori dedicati del tempo di salita forniscono una corrente di pull-up stabilizzata e di notevole intensità, in grado quindi di soddisfare i requisiti relativi al tempo di salita. Gli acceleratori sono attivati automaticamente soltanto durante le transizioni positive del bus, facendo salire le tensioni del bus con una velocità particolare. In questo modo viene migliorata l’affidabilità della scheda e del sistema, con transizioni morbide e controllate durante i fronti di salita. I sistemi diventano anche meno suscettibili al rumore durante i fronti di salita, poichè i pull-up degli acceleratori presentano un’impedenza significativamente inferiore alle resistenze di pull-up del bus. Inoltre, gli acceleratori consentono di utilizzare dei pull-up di valore superiore, in grado di ridurre l’assorbimento di corrente e migliorare il margine di rumore nello stato logico basso.

Un altro problema comune legato alla tempistica avviene quando il bus I2C si blocca nello stato logico basso: errori di comunicazione, presenza costante di zeri nei dati, e strani comportamenti della GUI sono tutti sintomi di un bus bloccato nello stato logico basso, mentre i segnali SCL o SDA si trovano normalmente bloccati verso massa, come conseguenza di un comportamento erroneo o confuso dei dispositivi I2C. Se non si agisce opportunamente, un dispositivo bloccato impedisce agli altri dispositivi presenti sul bus di comunicare. Quando il bus si blocca nello stato basso, il dispositivo host deve risolvere il problema manualmente, solitamente attraverso un system reset; questa operazione è però distruttiva, costosa, e provoca una perdita di tempo.

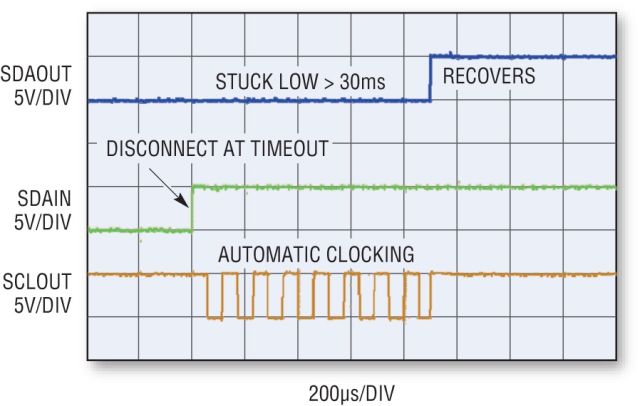

I blocchi del bus sono facilmente risolvibili utilizzando i buffer di Linear Technology con protezione dal blocco del bus selezionabile, come l’LTC4315, in cui le uscite SDA e SCL sono continuamente monitorate per determinare se lo stato basso venga mantenuto per oltre 30ms. Si osservi l'immagine seguente. Quando il fenomeno si verifica, i collegamenti ingresso-uscita di entrambi i segnali I2C vengono interrotti, impedendo l’ulteriore comunicazione con il dispositivo bloccato, mentre il buffer genera fino a 16 impulsi di clock sul pin SCLOUT nel tentativo di liberare il bus lato scheda. Se il bus si sblocca, oppure i 16 impulsi di clock sono completati, viene generato un bit di stop per resettare il bus, mentre i collegamenti I2C ingresso-uscita vengono ripristinati soltanto quando il bus si trova nello stato idle, e non nel mezzo di una transazione I2C.

Problemi legati ai segnali

I 111 indirizzi fisici disponibili nella modalità standard I2C possono rivelarsi sufficienti nella maggior parte dei casi, ma sistemi più complessi potrebbero richiedere la comunicazione con un numero maggiore di dispositivi. Un problema molto comune riscontrato dai progettisti è che essi sono obbligati a utilizzare dei dispositivi slave in grado di offrire soltanto un numero limitato di indirizzi univoci, e devono pertanto riutilizzarne alcuni (indirizzamento annidato).

Per risolvere questo inconveniente possono essere utilizzati i multiplexer I2C di Linear Technology, che permettono il riutilizzo di uno stesso indirizzo fisico I2C. Grazie alla loro natura bidirezionale, questi multiplexer possono anche essere utilizzati per pilotare i dati I2C dai bus di uscita al bus di ingresso.

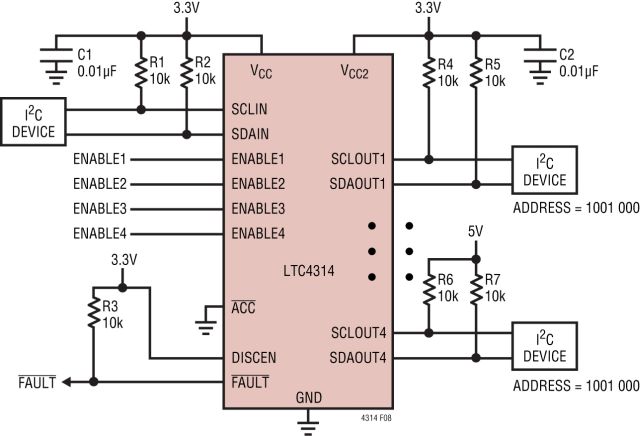

L'immagine seguente mostra il multiplexer 1:4 LTC4314 selezionabile tramite appositi pin, in cui a quattro dispositivi I2C è assegnato lo stesso indirizzo, mentre i pin di selezione individuali permettono all’utente di scegliere a quale bus a valle verrà collegato il bus a monte. È anche disponibile il multiplexer 1:4 LTC4306 selezionabile via software, il quale funziona in modo analogo al precedente, ma utilizza degli appositi comandi I2C (al posto dei pin hardware) per selezionare a quale bus a valle deve essere collegato il bus a monte. Questi multiplexer I2C integrano anche dei buffer, e pertanto offrono tutte le funzionalità dei buffer bus di Linear Technology, incluso il margine di protezione nei confronti del rumore elevato, l’acceleratore del tempo di salita, e la protezione contro il blocco del bus.

Conclusioni

Con oltre 30 anni di età, il bus I2C è tuttora ampiamente utilizzato, con sistemi sempre più grandi e complessi che sfidano continuamente i suoi requisiti e le sue specifiche. I progettisti possono oggi affrontare un’ampia selezione di problemi comuni di natura elettrica, temporale, o di forma dei segnali, ma la prassi migliore sarebbe quella di intraprendere delle misure correttive nei confronti di questi inconvenienti. Non è infatti sempre possibile prevedere quali tipi di dispositivi I2C si collegheranno al bus del sistema – un dispositivo I2C non conforme potrebbe infatti comportare il blocco del bus.

Utilizzando sin dai primi stadi della progettazione una giusta combinazione di soluzioni offerte da Linear Technology quali buffer I2C, acceleratori del tempo di salita, e multiplexer, è possibile soddisfare agevolmente i requisiti del bus I2C, ed è possibile espandere in futuro il sistema senza incontrare restrizioni o rallentamenti dovuti all’insorgenza di problemi sul bus.

A me questo bus piace molto e appena posso lo uso.

Alcuni dei problemi visti li ho incontrati, altri molto meno.

Ricordo qualche articolo recente sull’i2c in cui si parlava della resistenza di pull up e della necessità di farci attenzione, un errore comune.

Già perchè se non la metti, il segnale non va mai su e tu praticamente è come se non avessi collegato nulla.. 🙂

Ho scoperto da poco questo bus I2c, ma da subito mi è piaciuto moltissimo.

Ed ho fatto un paio di prove utilizzando due Arduino Uno come Master e Slave.

Leggendo questo articolo ho capito che ho visto solo la punta dell’iceberg.

Grazie davvero mi sarà utile.

Sergio

PS: le prove sono pubblicate sul mio blog.

Buon giorno,

Sono un abbonato PLATINUM. Questo articolo sulle problematiche I2C é molto interessante. Non é però riportato il numero della rivista firmware su cui é stato inserito. E’ possiibile saperlo o è possibile scaricare il pdf di questo solo articolo ? Con la vecchia gestione della rivista firmware era lecito farlo. Grazie.

Salve Michele, non si tratta di un articolo Firmware ma di un articolo free. Per scaricare l’articolo in PDF puoi utilizzare la funzione “estrapola in PDF” disponibile sul tuo browser.

Grazie mille.

Per chi come me, della vecchia guardia, ha problemi con i componenti a montaggio superficiale e preferisce utilizzare componenti a foro passante segnalo il P82B96 ed il P82B715 di Texas Instruments che sono disponibili in pdip.