Renesas ha messo a punto una nuova metodologia per riprogrammare i processori della serie R8C/38C proponendo un sistema assolutamente trasparente per l’utilizzatore, in grado di adattarsi ad ogni specifica richiesta e con prerogative tali da permettere al progettista di controllare direttamente tutta la fase di lavoro. Affrontiamo con questo articolo la terza e ultima puntata della serie, inclusa nella Rubrica Firmware Reload di Elettronica Open Source.

È possibile utilizzare i valori predefiniti previsti dal costruttore - 9600, 19200, 38400, 57600 e 115200 - inviando i necessari comandi; infatti, per impostare un valore pari a 9600 è indispensabile inviare, come primo e secondo byte, il valore B0; al contrario, possiamo ottenere un data rate di 19200 con due successivi comandi, byte, pari a B1. Così, per ottenere 38400 occorre inviare due B2, un data rate di 57600, i byte diventano B4, mentre con B4 si ottiene un data rate di 115200. Per riprogrammare la memoria flash, l’area ROM utente del processore, occorre rispettare un’apposita procedura; infatti, una volta selezionato il formato della comunicazione e regolato il bit rate, sarà possibile, attraverso alcuni comandi seriali, accedere alle risorse del processore e inserire il programma nella memoria non volatile. Schematizzando, possiamo riassumere questa operazione attraverso alcuni semplici passi:

- Selezionare un formato idoneo per la comunicazione

- Regolare lo stato della comunicazione

- Impostare il bit rate

- Eseguire il controllo dei dati

- Eseguire il controllo sullo stato della memoria

- Eseguire l’eventuale cancellazione del suo contenuto (è applicabile solo quando la memoria non risulti già cancellata)

- Eseguire la programmazione della memoria utente

- Eseguire la verifica dell’operazione precedente

- Terminare il processo di scrittura

Dopo aver impostato il formato della comunicazione e la regolazione del bit rate, si deve eseguire il controllo dei dati utilizzando la procedura ID data check. In questa operazione, il Serial Programmer dovrà inviare il clear status register command (valore 50h) e il read status register con il valore 70, sempre in notazione esadecimale. Al termine della negoziazione iniziale, il dispositivo di destinazione dovrà restituire, entro un termine di venti secondi, il valore dei due bit SR11 e SR10 contenuti nel registro SRD1: questi devono essere entrambi pari a 1 pena la nullità dell’intera operazione di verifica iniziale. In seguito, qualora i due bit fossero settati a 1, il Serial Programmer dovrà trasmettere il valore F5, ID data check function, insieme all’indirizzo al quale il parametro ID1 è contenuto. Non solo, il Serial Programmer ha anche il compito di trasmettere il parametro ID Size, ID1 (07h), ID1 a ID7 e, infine, di trasmettere il read status register command, ovvero 70h. Al termine, il destinatario dovrà trasmettere sempre il valore dei bit SR11 e SR10 in SRD1 chiudendo definitivamente l’operazione corrente. La successiva operazione è verificare che l’area dell’utente ROM (flash dei dati, il programma ROM) del target non contenga nulla, o sia stata già cancellata. Questa operazione si esegue inviando dal Serial Programmer al target due valori che abilitano il componente a lavorare in questa modalità; in effetti, dal Serial Programmer si spedisce, come primo valore, il Clear Status Register Command (50h) e poi all block blank check command (pari a 26h). Per eseguire il comando è però anche necessario inviare un comando di conferma con il valore D0. Il Serial Programmer, al fine di verificare il successo dell’operazione, ha la necessità di leggere il registro Read Status con 70h: il target entro 20 secondi deve spedire al Serial Programmer il contenuto del registro per la necessaria verifica.

In effetti, il Serial Programmer di Renesas deve leggere il bit SR5 e verificare lo stato del bit: alla presenza di un valore pari a 0 l’operazione si ritiene conclusa senza errori, altrimenti si dovrà ripetere il tentativo. Se vogliamo, o abbiamo la necessità di procedere alla cancellazione della memoria, dobbiamo iniziare un’altra procedura: in questo caso dobbiamo predisporci per cancellare l’area utente della ROM (flash dati, il programma ROM). Dobbiamo attivare la procedura di cancellazione della memoria su ogni indirizzo ripetendo in maniera sequenziale tutta l’operazione per quante sono le locazioni da cancellare. Infatti, dopo la negoziazione iniziale, trasmissione del Clear Status Register command (50) e del Block Erase Command (20), dobbiamo inviare l’indirizzo della locazione con il comando di conferma (D0) e la richiesta del comando di status register (70h) e aspettare la ricezione del registro per verificare il contenuto del bit SR5: con un valore pari a 1 si rileva la presenza di errori nella fase di scrittura in memoria; altrimenti possiamo pensare di chiudere l’operazione corrente e passare alla locazione successiva.

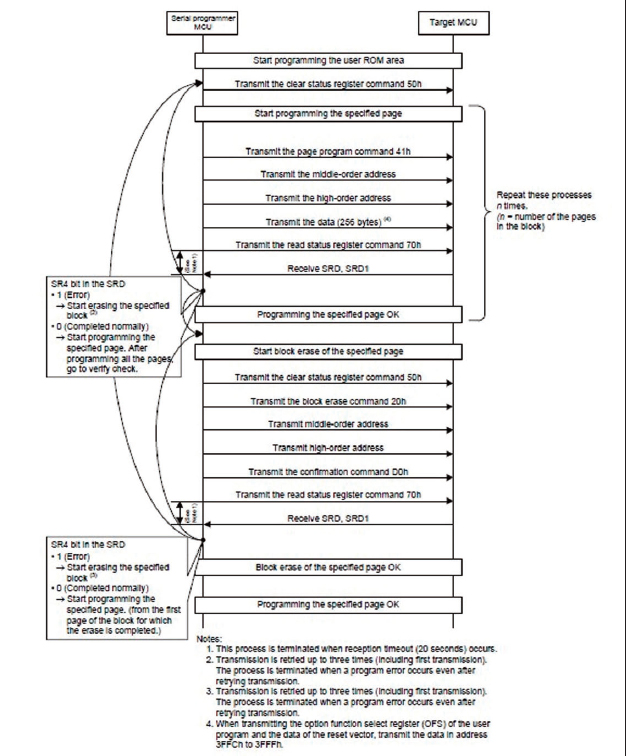

Di certo, la parte saliente dell’intera operazione si trova nella programmazione del componente stesso, perché possiamo sostituire il programma presente in memoria flash con un nostro programma che rispetti le nostre specifiche di progetto. A questo proposito, in Figura 1 si pone in evidenza l’intera operazione. Infatti, dall’illustrazione possiamo vedere che l’operazione di scrittura è fatta utilizzando il concetto delle pagine: in altre parole, la scrittura in flash è svolta a gruppi di 256 byte (una pagina) garantendo così una maggiore prestazione finale.

Figura 1: Sequenza di programmazione

Non solo, dalla figura notiamo che, insieme al comando 50h, clear status register command, si utilizza anche il comando 41h, per l’appunto il codice che si riferisce al comando Page Program. Si evince che il Page Program è un opcode complesso perché richiede diversi opcode successivi. Infatti, dopo aver inviato, in prima battuta, l’indirizzo della locazione del target, è necessario anche inviare i dati in modo paginato e in seguito si dovrà controllare l’esito dell’operazione: anche in questo caso si controlla il registro di stato per verificare lo stato del bit SR4. Il protocollo così definito da Renesas permette anche di verificare l’integrità dei dati scritti: questa operazione si svolge attraverso il comando verify. In questo caso, si legge il programma utente dal target, verificando che i dati letti siano uguali a quelli presenti sul computer.

La verifica è condotta a gruppi di 256 byte utilizzando l’opcode FFh: una volta che il target invia i dati verso il Serial Programmer, si compie una verifica di ogni byte delle due memorie e solo in caso di una perfetta coerenza l’operazione si considera conclusa con successo. Al termine della programmazione si deve tornare in modalità operativa con l’opcode Boot End Program, una volta invocato si chiude la sessione di download/upload. Il meccanismo, anche in questo caso, è abbastanza semplice: il Serial Programmer invia l’opcode Boot End Program, ovvero 01h, al target seguito dal comando di conferma con D0. Il target, una volta ricevuta la conferma, deve rispedire al Serial Programmer lo stesso comando come acknowledge dell’operazione.

CONCLUSIONI

Renesas, per approfondire tutti i diversi aspetti di questa nuova tecnologia, ha messo a disposizione una notevole mole di informazioni e codice sorgente auto-esplicativo [2], da utilizzare per approfondirne tutti i diversi aspetti. Grazie a questo nuovo protocollo, la casa costruttrice intende così offrire a tutti i progettisti delle nuove possibilità perché, con l’uso di una semplice linea seriale, permette di condurre sessioni di upgrade in modo perfettamente trasparente e senza richiedere un impegno particolare.

Leggi anche le puntate precedenti della serie:

Il Serial Programmer di Renesas - Puntata 1

Il Serial Programmer di Renesas - Puntata 2