I microcontrollori Fujitsu della serie F2MC-8FX mettono a disposizione dello sviluppatore un’interessante ed utilissima funzione di watchdog. Vediamo in questo articolo in cosa consiste e come utilizzarla a livello pratico.

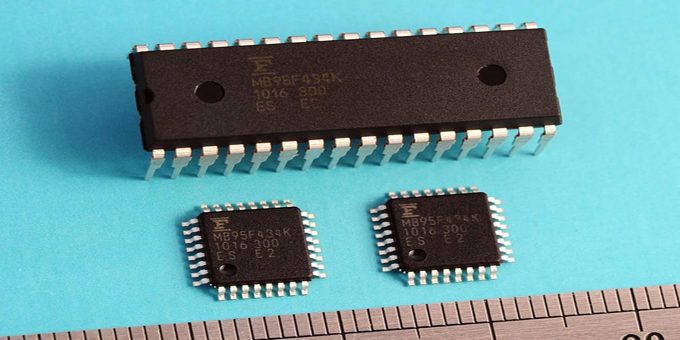

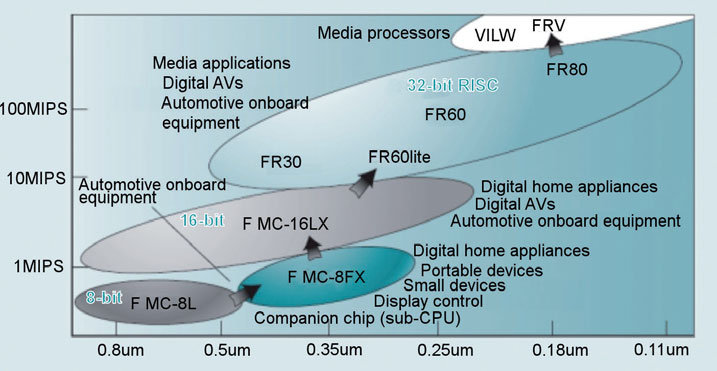

La famiglia di microcontrollori F2MC-8FX fu introdotta sul mercato da Fujitsu nel 2004 per rispondere alla crescente domanda, presente soprattutto sul mercato asiatico, di cpu ad 8 bit in grado di fornire un’elevata velocità e bassi assorbimenti. La famiglia 8FX si è poi diffusa rapidamente, trovando largo impiego principalmente nei settori audio/video digitale (lettori di CD/DVD) e delle apparecchiature domestiche (forni a microonde, frigoriferi, ecc.). Questa importante affermazione si è resa possibile grazie anche ad alcune caratteristiche peculiari dei micro 8FX, tra le quali la possibilità di controllare display LCD fino a 160 pixel con funzionalità di blinking integrata a livello hardware. Per quanto riguarda il futuro, Fujitsu continuerà ad aggiungere nuovi modelli alla già numerosa famiglia 8FX, aumentandone la densità di memoria ROM/RAM, il numero di pin, le funzionalità, e riducendone i consumi e la tensione di alimentazione. In figura 1 viene mostrato il posiziona mento della serie F2MC-8FX all’interno della famiglia di microcontrollori Fujitsu: la velocità di elaborazione è dell’ordine di un MIPS, mentre la tecnologia di processo impiegata per la sua fabbricazione è dell’ordine dei 0,35 µm.

Figura 1: il posizionamento della famiglia F2MC-8FX.

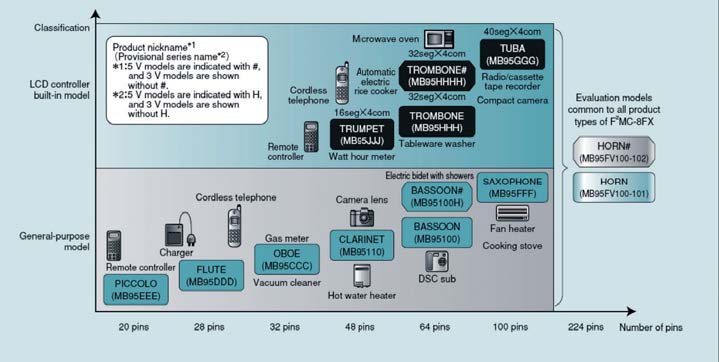

La figura 2, invece, mostra l’intera famiglia di microcontrollori F2MC-8FX, suddivisi in base al tipo di package (numero di pin disponibili) ed alle caratteristiche della cpu (presenza o meno del controller LCD).

Figura 2: le MCU della serie F2MC-8FX.

Ad esempio, la MCU del tipo MB95FFF (soprannominata all’interno di Fujitsu “Saxophone”) è disponibile in un package di 100 pin, ha un’alimentazione pari a 3V, è un modello per usi generici (forni a microonde, termoventilatori, ecc.) e non dispone di controller LCD.

Utilità del watchdog

Il watchdog (dall’inglese “cane da guardia”) ha lo scopo di fornire un meccanismo di ripristino della normale esecuzione di un’applicazione software nel caso in cui questa sia entrata in un loop di istruzioni non voluto, causato in genere o da un errore di progettazione del software o da un malfunzionamento dell’hardware controllato dall’applicazione stessa. Il concetto calla base di watchdog è il seguente: periodicamente l’applicazione deve resettare un apposito circuito di watchdog; se ciò non avviene, ad esempio perchè il software si “perde” in un loop infinito, il circuito di watchdog genera un reset (detto appunto “watchdog reset” ed assai noto agli sviluppatori firmware) che permette al software di ripartire ed eseguire quindi il “recovery” da una situazione critica. L’attività periodica di rinfresco del watchdog viene denominata in gergo “kicking the dog” (scalciare il cane). Al fine di impedire disabilitazioni accidentali del watchdog dovute a malfunzionamenti del software, il watchdog stesso, una volta attivato, non può più essere disabilitato; ciò, come vedremo, avviene anche nel caso dei micro della serie F2MC8FX.

Il watchdog timer del micro F2MC-8FX

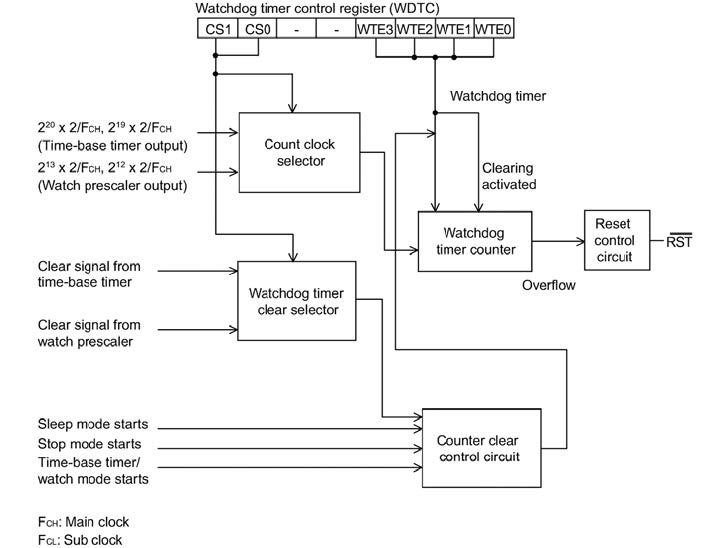

La figura 4 mostra lo schema a blocchi del watchdog timer. Il significato di ciascun blocco è il seguente:

➤ Count clock selector - seleziona la sorgente di clock del watchdog tra le due disponibili: time-base timer e watch prescaler. FCH è la frequenza del main clock, mentre FCL è quella del sub clock. Gli input di questo blocco sono il segnale di clock selezionato come sorgente ed i bit CS1-0 che permettono di effettuare tale selezione, mentre l’uscita è il segnale di clock.

➤ Watchdog timer counter - come ingresso riceve il segnale di clock selezionato ed i comandi di clear e start del watchdog. Nel caso in cui il watchdog timer non sia rinfrescato nei tempi stabiliti, si genera una condizione di overflow che causa un watchdog reset (segnale di uscita /RST del blocco reset control circuit).

➤ Watchdog timer clear selector - seleziona il segnale di clear proveniente dal time-base timer o dal watch prescaler.

➤ Counter clear control circuit - genera i comandi di clear e start del watchdog.

➤ Watchdog timer control register (WDTC) - attraverso questo registro è possibile eseguire la selezione della sorgente di clock, del periodo del watchdog timer, eseguir ne l’attivazione ed il rinfresco.

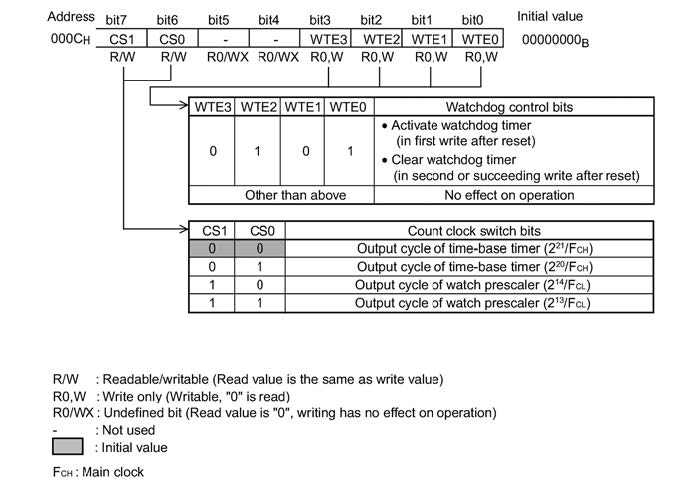

Attraverso il registro WDTC (figura 5) è possibile eseguire interamente la programmazione del watchdog timer.

Figura 5: il Watchdog Timer Control Register (WDTC).

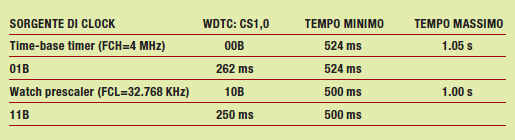

Il registro è mappato all’indirizzo di memoria 000CHEX, ed il suo valore iniziale è pari a 0. I bit CS1-0 sono di tipo read/write e permettono di selezionare la sorgente di clock del watchdog ed il periodo del watchdog timer in base alla tabella 1.

Tabella 1: Selezione della sorgente di clock e del periodi del watchdog timer nel registro WDTC.

Il significato dei tempi minimo e massimo è il seguente: se il watchdog non viene rinfrescato, un watchdog reset viene generato nell’intervallo di tempo compreso tra il tempo minimo ed il tempo massimo. Ne consegue che, al fine di evitare un watchdog reset, è sufficiente eseguire periodicamente il clear del watchdog con un periodo inferiore al tempo minimo. I bit WTE3-WTE0 consentono invece di eseguire sia l’attivazione che il clear del watchdog timer secondo la seguente regola: la prima scrittura eseguita dopo ogni reset attiva il watchdog, mentre le scritture successive eseguono il clear. Occorre osservare che delle sedici combinazioni ottenibili con questi bit solo una è ammessa, cioè 0101B. La lettura dei bit WTE3-0 restituisce sempre il valore 0. In fine, i bit 5-4 sono “don’t care” in scrittura, mentre in lettura restituiscono sempre il valore 0. Riassumendo, per attivare il watchdog timer occorre scrivere nei bit WTE3-0 il patter n “0101B” e, contemporaneamente, selezionare la sorgente di clock e la “finestra” di watchdog impostando il valore dei bit CS1-0. Una volta attivato, il watchdog timer non può più essere fermato; l’unico modo per disabilitarlo è quello di provocare un reset. Inoltre, anche il valore assegnato ai bit CS1-0 non può più essere modificato dopo aver eseguito l’attivazione del watchdog. Come visibile in figura 4, il clear del watchdog viene eseguito anche quando si esegue il clear del clock selezionato come sorgente del watchdog (time-base timer o watch prescaler).

Figura 4: schema a blocchi del watchdog timer

Questo fatto comporta una limitazione nell’utilizzo del watchdog: se l’applicazione esegue ripetitivamente il clear del clock selezionato come sorgente, anche il watchdog viene rinfrescato, e pertanto la sua utilità ne risulta notevolmente compromessa. Infine, come indicato nello schema a blocchi di figura 4, se il micro entra in standby mode (ciò può avvenire se viene attivata una delle seguenti modalità: stop mode, sleep mode, watchmode, time-base timer mode), il watchdog viene rinfrescato ed il suo funzionamento viene sospeso; uscendo dallo standby mode, il watchdog riprende a funzionare correttamente. Il listato 1 mostra un semplice esempio di programmazione del watchdog, supponendo che la frequenza del main clock sia pari a 4 MHz.

...

void main(void)

{

/* attivazione del watchdog timer

Tmin=262.144 ms

Tmax=524.288 ms */

WDTC = 0x45;

/* main loop */

for (;;)

{

/* “kicking” del watch-

dog */

WDTC = 0x45;

...

}

}

...

| Listato 1 |