Jitter clock: Le applicazioni che ricevono segnali deboli in prossimità di toni elevati, come ad esempio i riflessi statici del Doppler, radar e RFID sono sensibili nei confronti dei rumori di fase.

Non è l’ADC ma l’uso delle apparecchiature a determinare le necessità

Al contrario, quando viene digitalizzata una uscita CCD, in genere lo jitter non è un problema grazie all’intervallo di tempo molto ridotto necessario per il campionamento. Anche le applicazioni video non sono molto sensibili. Ad esempio, in HDTV la schermata standard è di circa 6.400psec (tempo per pixel).

Applicazioni per le comunicazioni con un elevato symbol rate generalmente non sono sensibili ai rumori di fase ravvicinati, e potrebbero non essere eccessivamente sensibili agli effetti del rumore di fase a banda larga. Forme d'onda con elevata ampiezza (WCDMA OFDM) con relativa distribuzione uniforme di potenza hanno un basso livello di potenza RMS, e richiedono anche altezza libera, in modo da non elevare il rumore di fondo quanto un singolo tono di ampiezza massima. Tuttavia tipi di modulazione di classe superiore, QAM e la fase di modulazione M-nary sono più sensibili al rumore ed hanno il ciclo di recupero della portante delle bande d’ampiezza più stretto allo stesso symbol rate, come per esempio QPSK utilizzato nei sistemi CDMA.

Quando forti interferenze (toni singoli) possono apparire molto vicini ad una radio digitale, oppure possono risultare molto più forti di un segnale di interesse, è generalmente esigente in termini rumore di fase, e possono essere sensibili al rumore di fase a banda larga. Come ogni sorgente di segnale a banda larga tende ad avere un alto fattore di cresta, e necessita di spazio per interferenti, la potenza nominale al ADC può essere bassa. Le caratteristiche della banda di interesse deve essere presa in considerazione nel decidere su una sorgente di clock.

Selezione di un oscillatore per pilotare un ADC ad alta velocità:

La maggior parte degli oscillatori avranno un rumore di fase ravvicinato che limiterà la chiusura della banda dinamica ad una primaria efficace. Se il rumore di fase ravvicinato è importante, in base all’esigenza della vostra banda dinamica in prossimità di toni forti, potrebbe essere necessario un PLL (Phase Locked Loop) per ridurre il rumore ravvicinato della sorgente del vostro oscillatore o per bloccare il vostro oscillatore ad una precisa frequenza di riferimento.

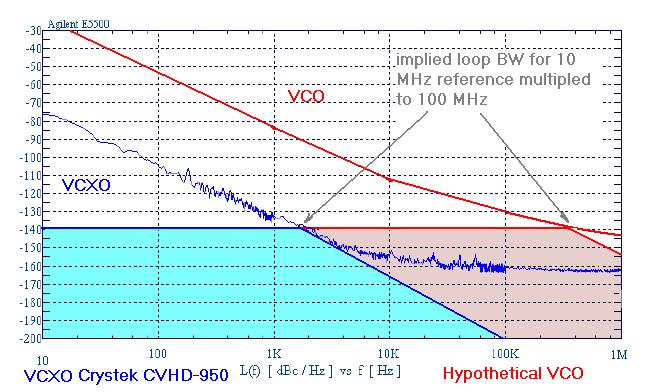

L'uso di un PLL come riduttore di jitter fornisce essenzialmente un filtro di allineamento per bande ridotte. La vostra scelta dell’oscillatore detterà il ciclo della larghezza di banda, in questo modo: il vostro loop BW desiderato determinerà l'oscillatore. A VCXO (oscillatore a cristallo con controllo via tensione) richiede solo un ciclo di larghezza di banda stretta per allinearsi ad un riferimento stabile. I VCO possono fornire un'ampia gamma di sintonia, ma hanno bisogno di un ciclo BW più ampio, al fine di ridurre il loro rumore di fase ravvicinato a livelli accettabili.

Figura 4. Confronto di VCXO contro ipotetiche prestazioni di rumore di fase del VCO

Se si richiede una gamma di sintonizzazione molto stretta, magari legato ad un oscillatore di riferimento, l'uso di un VCXO è l'opzione migliore. Se vi occorre un intervallo di sintonizzazione ottava di un VCO, e si ha bisogno di un basso rumore di fase ravvicinato, si potrebbe avere un problema, specialmente se avete bisogno di rapporti di divisione elevate e basse frequenze di riferimento a confronto in un PLL.

Figura 4 mostra una VCXO reale, confrontata al grafico di un tipico rumore di fase del VCO. La larghezza di banda ottimale per il circuito PLL è suggerita dalla intersezione tra la densità di rumore dell'oscillatore di riferimento moltiplicato per la frequenza centrale, e la trama rumore di fase del VCXO o VCO. L'esempio suggerisce 2 kHz per il VCXO, e 300kHz per il VCO. Un angolo 300kHz richiede una frequenza di comparazione di almeno 3MHz che suggerisce 5MHz.

Il VCXO potrebbe essere utilizzata con una frequenza di confronto a partire da 20 kHz. Se venisse utilizzata una frequenza di riferimento inferiore (con alti rapporti di suddivisione) con il VCO, l’intersezione tra il rumore di fase moltiplicato con quello del VCO sarebbe ad una frequenza più bassa, e sostanzialmente aumenterebbe lo jitter. L'uso di un ciclo BW eccessivamente basso, con un rapporto di moltiplicazione inferiore farà sì che il rumore di fase di un VCO rimanga entro il ciclo BW.

Se l'applicazione è insensibile al rumore di fase ravvicinato, e non ha bisogno di essere bloccato ad un riferimento, può essere utilizzato un XO.

Sorgenti di Clock e Architetture di Clock

Un buon clock può essere compromesso dall’instradamento attraverso un FPGA dove prevale il crosstalk interno. L’FPGA spesso massimizza gli I/O sacrificando pin del ground, con conseguente rimbalzo sul ground. Se l'FPGA pilotasse le uscite a differenti rate, queste si manifesteranno in qualsiasi clock instradato attraverso il chip FPGA e in ultima analisi l'uscita di qualsiasi ADC utilizzando tale clock. Un flip-flop a basso rumore con clock dal segnale pulito VCO può essere usato come una fase di ri-temporizzazione per eliminare lo jitter quando un FPGA è usato per dividere la frequenza del VCO.

L’FPGA può essere usato per implementare un PLL a banda stretta per un VCXO esterno, con un filtro di ciclo esterno, e un driver per filtro di ciclo protetto dal rimbalzo verso il ground riflesso dall’FPGA. Non usare una DLL per la produzione di un clock per un ADC a meno che non stiate aumentando il sampling della banda audio.

Un buon clock può anche essere compromesso dall’instradamento tra segnali digitali. Ogni clock generato da qualsiasi distanza dal ADC deve passare attraverso un conduttore di rame e di vias.

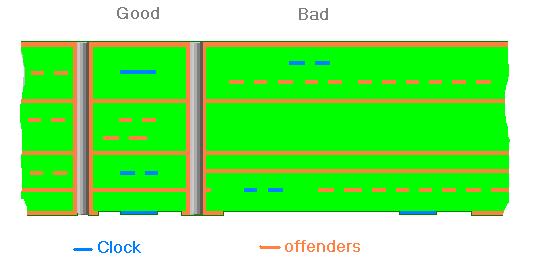

La Figura 5 mostra esempi di buoni e cattivi instradamenti di clock. I casi gravi sono dove i clock sono all'interno delle cavità condivise con i segnali digitali.

Figura 5. Esempio di aspetto di buoni e cattivi instradamenti di clock

Jitter Clock: capire l'effetto sugli ADC ad alta velocità: Conclusione

L'impatto dello jitter sulle prestazioni degli ADC è funzione della frequenza in ingresso (slew rate) e non della frequenza di campionamento. La scelta della sorgente di clock sarà determinata dall'applicazione. Non credere sempre ai distributori di sorgenti di clock. Prova le tue sorgenti di clock con la tua scheda di valutazione ADC prima che sia troppo tardi.