Sul blog di Elettronica Open Source puoi leggere non solo tutti gli articoli Premium riservati agli abbonati e inseriti nella rivista Firmware 2.0 (insieme ad articoli tecnici, progetti, approfondimenti, news, tutorial a puntate e molto altro) ma anche gli articoli della Rubrica Firmware Reload. In questa Rubrica del blog abbiamo raccolto gli articoli tecnici della vecchia rivista cartacea Firmware, che contengono argomenti e temi evergreen per Professionisti, Makers, Hobbisti e Appassionati di elettronica. Oggigiorno la continua integrazione di moduli aggiuntivi nei microcontrollori permette di avere in un singolo integrato varie funzionalità interessanti come, tra le altre, quelle fornite dai convertitori analogico digitali. L’Atmel propone dei moduli ADC nella famiglia di microcontrollori XMEGA con caratteristiche performanti e configurabili per svariate applicazioni. In questo articolo ne analizziamo le caratteristiche più rilevanti.

I MODULI ADC DEI MICROCONTROLLORI XMEGA

Quando viene misurata una grandezza di qualsiasi tipo, l’insieme di valori che essa può assumere in natura è un insieme continuo e composto da infiniti punti. Nelle comunicazioni di tipo digitale il valore della grandezza in questione, per essere meglio gestito, deve essere convertito in formato discreto e ciò avviene preventivamente grazie a un processo di campionamento nel tempo. Affinché una grandezza sia trasmissibile e codificabile con un numero finito di bit e quindi in forma numerica, è necessario che questa possa assumere solo un numero finito di valori discreti, il che si ottiene tramite un successivo processo di quantizzazione del valore della grandezza in questione. Tutto questo è possibile ottenerlo mediante un convertitore analogico-digitale (Analog to Digital Converter - ADC) che è un circuito elettronico in grado di convertire un segnale analogico con un andamento continuo (ad esempio una tensione) in ingresso in una serie di valori discreti, mentre un convertitore digitale- analogico (DAC) effettua l’operazione inversa. In una prima categorizzazione si possono distinguere due grandi famiglie di ADC, i lineari ed i logaritmici; nel primo caso significa che sono progettati per produrre in uscita un valore che è funzione lineare del segnale in ingresso, mentre per la seconda tipologia l’uscita è una funzione logaritmica dell’ingresso. In un ambito più generale, in elettronica possiamo distinguere cinque modi di implementare un ADC:

- ADC a conversione diretta (Flash ADC): hanno un comparatore per ognuno dei livelli di voltaggio riconosciuti dal quantizzatore e il segnale di ingresso arriva a tutti i comparatori. Questi convertitori sono i più veloci in assoluto e sono usati per campionare segnali ad alta frequenza, fino a diversi GHz. Poiché il numero di comparatori necessari cresce esponenzialmente con il numero di bit richiesti, i convertitori flash raramente hanno più di 8 bit di risoluzione.

- ADC ad approssimazioni successive (SAR - Successive Approximation Register): usano un comparatore e un convertitore digitale-analogico; a ogni passaggio l’ADC prova a impostare un bit, partendo dall'MSB (Most Significant Bit, bit con peso maggiore) e usando il DAC confronta il segnale campionato con il segnale di ingresso in feedback. Questo convertitore individua un bit a ogni iterazione in una sorta di ricerca binaria e la risoluzione è limitata solo dalle esigenze di frequenza di campionamento e dal rumore in ingresso.

- ADC a inseguimento (a codifica-delta): hanno un contatore up-down collegato a un DAC, che confronta il segnale di uscita del DAC con il segnale di ingresso e interrompe il conteggio quando i valori sono abbastanza vicini tra loro. Quando questo accade, il contatore contiene il livello quantizzato del segnale. Questi convertitori sono usati spesso per leggere grandezze fisiche che non variano con elevata velocità ma che devono essere lette con molta precisione.

- ADC a doppia rampa (Dual Slope o a integrazione): producono un segnale a dente di sega che sale, per poi decrescere velocemente a zero. Il segnale di ingresso viene integrato facendo salire la rampa mentre un contatore segna il tempo. Quando la rampa raggiunge un livello noto, il conteggio termina e indica il valore quantizzato del segnale. Questo tipo di ADC è sensibile alla temperatura poiché può alterare il clock usato per segnare il tempo o alterare la tensione di riferimento per la rampa e deve essere ricalibrato spesso.

- ADC a pipeline (noto anche come subranging quantizer): sono simili agli ADC ad approssimazioni successive, ma invece di individuare un bit alla volta individuano un blocco di bit; in un primo passo avviene una conversione grezza del segnale che viene poi riconvertito da un DAC; quindi si quantizza la differenza tra il segnale originario e quello campionato, eventualmente si può procedere a quantizzazioni sempre più fini con passi successivi. In quest’ultima categoria ricade la famiglia degli ADC XMEGA dell’Atmel, di cui approfondiamo le maggiori caratteristiche per dare una panoramica generale sulle loro funzionalità più salienti.

L’ADC DEGLI XMEGA

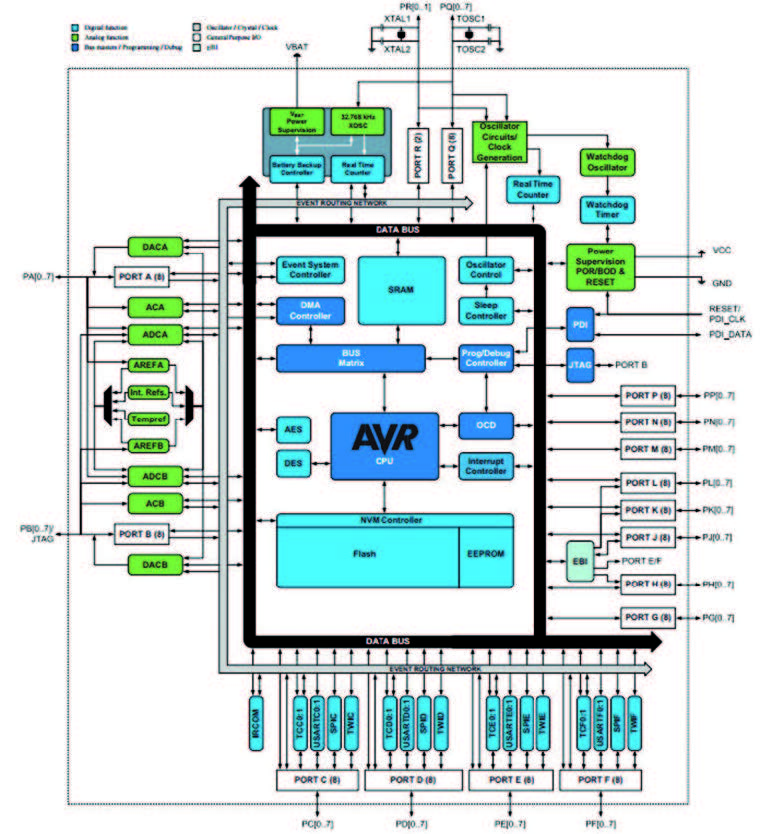

Gli XMEGA sono una famiglia di microcontrollori a bassa potenza, ricca di periferiche e ad alte prestazioni, basate sull’architettura AVR RISC migliorata, che permettono l’esecuzione di istruzioni in un unico ciclo di clock, raggiungendo throughput fino a un milione di istruzioni al secondo (MIPS) per MHz e dando la possibilità di ottimizzare il consumo di energia in funzione della velocità di elaborazione desiderata. La CPU AVR combina un ricco set di istruzioni con 32 registri ad impiego generico, tutti direttamente collegati all’unità logica aritmetica (ALU), con due registri indipendenti a cui accedere in una singola istruzione, eseguita in un ciclo di clock. L’architettura risultante permette di avere un codice più efficiente, ottenendo un throughput molte volte più alto rispetto ai tradizionali microcontrollori basati su tecnica CISC. Facendo riferimento alla Figura 1, possiamo vedere tra i vari moduli del micro XMEGA, quello degli ADC che permette conversioni con alte prestazioni fino a 2 milioni di campioni al secondo (MSP - Million Samples Per Second) con una risoluzione di 12bit; ha una vasta gamma di impostazioni per i multiplexer (MUX), integra uno stadio di guadagno e quattro canali di ingresso virtuali, che fanno di questo modulo un integrato molto flessibile e adatto per una vasta gamma di applicazioni, come l’acquisizione dati, il controllo embedded e il trattamento di segnali (general signal processing).

Figura 1: Diagramma a blocchi dei micro XMEGA

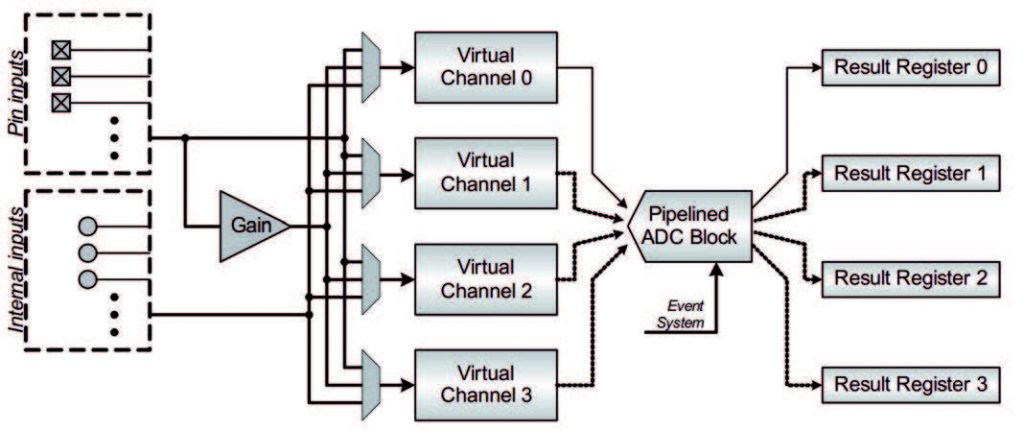

Il blocco di conversione ADC ha un’architettura pipeline a 12 stadi capace di campionare diversi segnali in parallelo, essendoci quattro multiplexer selezionabili in ingresso con configurazioni singole. Le impostazioni di configurazione per i quattro multiplexer possono essere viste come canali virtuali separati, ciascuno con una serie di registri di risultati, ma tutti fanno riferimento allo stesso blocco di conversione ADC. Per una maggiore comprensione si veda la Figura 2.

Figura 2: Diagramma a blocchi di un ADC XMEGA

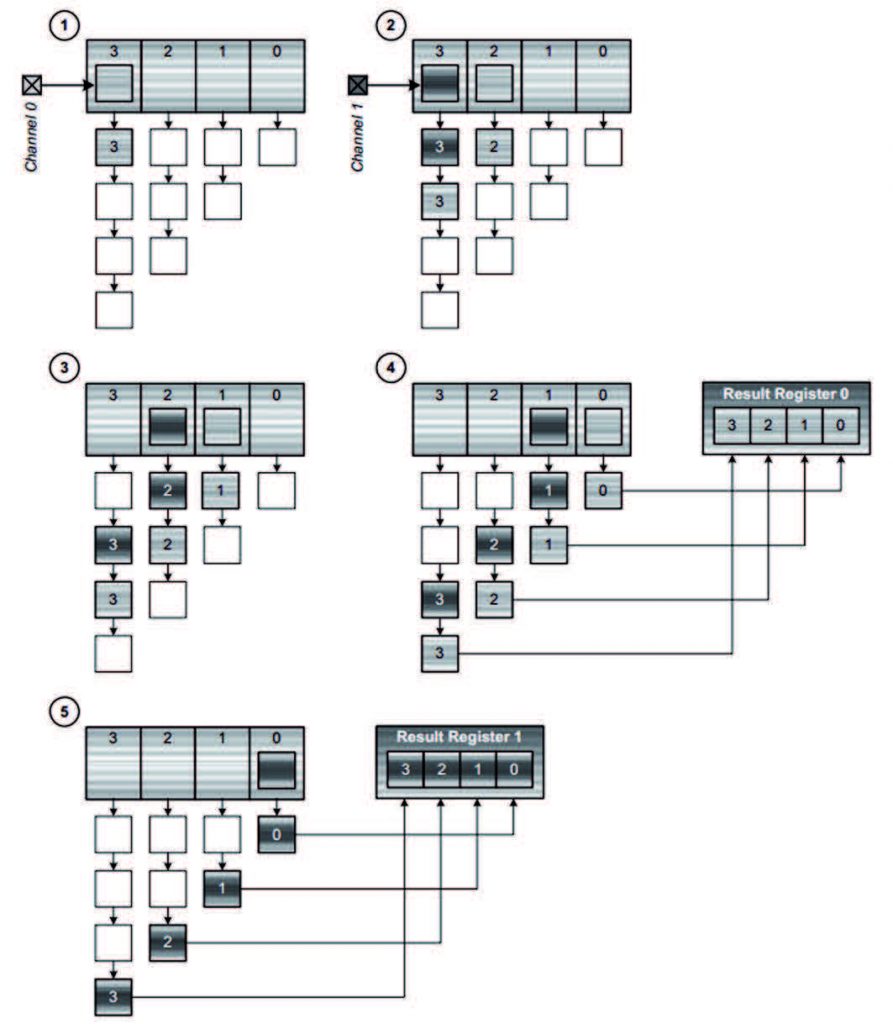

Sugli integrati Atmel AVR XMEGA A, si può campionare una serie di uscite del multiplexer a ogni ciclo di clock dell’ADC, mentre su altre famiglie come nella serie D XMEGA si può effettuare una nuova misura e prelevarla in uscita una volta che la conversione precedente sia stata completata. Negli XMEGA A ogni segnale si propaga attraverso la pipeline, in cui un bit viene convertito in ciascuna fase; in questo modo l’ADC nell’integrato nell'XMEGA A è in grado di campionare un segnale ogni ciclo di clock, anche se ciascun segnale deve propagarsi attraverso tutte le fasi della pipeline prima che il risultato sia pronto nel registro per essere letto. Il tempo di propagazione per una conversione singola di un segnale attraverso la pipeline è di sette cicli di clock per conversioni ADC a 12bit e cinque cicli di conversione nel caso di 8bit. Se viene utilizzata la funzionalità del guadagno, il tempo di propagazione aumenta di un ciclo. Al pieno utilizzo dell'XMEGA A, si ottiene un risultato a ogni ciclo di clock dell’ADC, mentre con l’integrato XMEGA D si riesce a ottenere un campione ogni 5 - 8 cicli di clock dell’ADC a seconda della modalità di funzionamento. In Figura 3 viene mostrata una pipeline semplificata a 4 stadi durante la conversione di due segnali di ingresso, da cui si può notare che una volta che il segnale è stato campionato nella pipeline, il primo stadio converte l'MSB (Most Significant Bit) del primo segnale. Mentre il secondo stadio è pronto per la conversione del bit successivo del segnale, il primo stadio ora converte l'MSB del secondo segnale e così via. Si tenga presente che altre famiglie Atmel, come ad esempio le XMEGA D3/D4, non hanno un ADC in pipeline e i quattro canali virtuali.

Figura 3: Pipeline di un ADC con la propagazione di due segnali

LO STADIO DEL GUADAGNO

L’ADC ha uno stadio di guadagno interno che può essere configurato per amplificare una tensione in modo da consentire la misurazione di tensioni più piccole di modo differenziale. Questo è uno stadio di guadagno condiviso che può essere utilizzato da tutti i canali. Quando il canale è configurato per utilizzare il guadagno, lo stadio di guadagno è inserito tra il canale di selezione in ingresso al MUX (multiplexer) e il blocco di conversione. Le impostazioni di guadagno disponibili sono: 1x, 2x, 4x, 8x, 16x, 32x e 64x. In un’architettura di questo tipo è possibile impostare il fattore di guadagno per il canale ed è possibile avere singole impostazioni di guadagno per tutti i canali virtuali. Il ritardo di propagazione di un campione attraverso il modulo ADC aumenta di un clock sull'XMEGA A quando viene utilizzato lo stadio di guadagno, mentre su altre famiglie il ritardo di propagazione dipende dalle impostazioni del guadagno:

- Ritardo di propagazione = 1 per un’impostazione del tipo 1/2x, 1x, 2x e 4x

- Ritardo di propagazione = 2 per un’impostazione del tipo 8x e 16x

- Ritardo di propagazione = 3 per un’impostazione del tipo 32x e 64x

Come è facile comprendere, per ridurre al minimo il percorso del segnale analogico per il miglior risultato possibile, è raccomandabile disattivare il guadagno quando non è necessario.

LE TIPOLOGIE DI CONVERSIONE

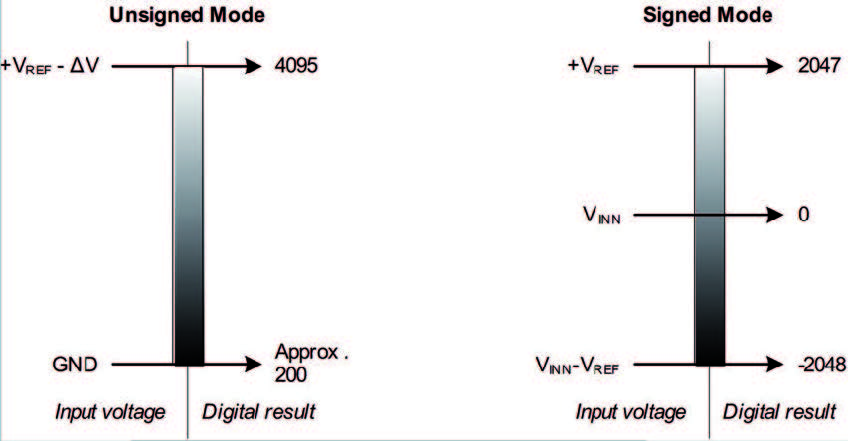

Il blocco di conversione può essere messo in due modalità di conversione: unsigned e signed. Per meglio chiarire si faccia riferimento alla Figura 4:

- In modalità unsigned (senza segno) l’intervallo di conversione va da massa alla tensione di riferimento (VREF). Per poter riuscire a rilevare il passaggio attraverso lo zero (zero-cross) viene sottratta una tensione definita (ΔV), che è di circa 0,05xVREF in modo che il livello della massa (GND - Ground) sarà di circa 0,05 del valore totale (ad esempio 0,05x4095 con risoluzione a 12-bit). Questo limita anche che la tensione d’ingresso massima è di VREF - ΔV.

- In modalità signed (con segno) l’intervallo va dal valore negativo al positivo della tensione di riferimento ma la tensione di ingresso deve essere comunque compresa tra GND e VREF.

Anche se il valore risultante può essere negativo o con tensioni inferiori alla massa (Ground - GND) oppure superiori all’alimentazione, in ogni caso tali valori non devono essere applicati a nessuna porta di ingresso del micro. In Figura 4 è mostrata la differenza delle due conversioni e, com’è facile comprendere, la prima modalità fornisce maggiore risoluzione su valori positivi rispetto alla seconda, ma non è in grado di convertire valori negativi. La modalità con segno può convertire valori negativi ma a costo di una risoluzione generale inferiore. La modalità signed può essere utilizzata come modalità di ingresso sia per tensioni differenziali che per ingressi single-ended, mentre la modalità unsigned è disponibile solo per l’ingresso single-ended o interno. Si tenga presente che la modalità di conversione una volta impostata è valida per tutte le conversioni dell'ADC e non singolarmente per ciascun canale, il che significa che l'ADC deve essere messo in modalità con segno anche se solo uno dei canali utilizza gli ingressi differenziali.

Figura 4: Tipologie di conversione unsigned e signed

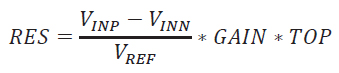

Per quanto riguarda il risultato della conversione nella modalità con segno, abbiamo:

dove VINP è la tensione all'ingresso positivo e VINN è la tensione all'ingresso negativo dell'ADC, mentre GAIN corrisponde all'impostazione di guadagno utilizzato e TOP è il valore superiore della particolare risoluzione configurata, pari a 2048 per la modalità a 12bit e 128 per la modalità a 8bit.

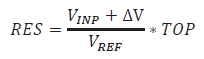

Per la modalità unsigned invece si ha:

dove VINP è l'ingresso single-ended e TOP è il valore superiore della particolare risoluzione configurata, per la modalità a 12bit è pari a 4096 e 256 per la modalità a 8bit. In entrambi i casi il risultato verrà memorizzato nei registri di risultato per ogni canale, che hanno dei flag separati per indicare quando una nuova conversione è pronta. Se il risultato non viene letto prima di una nuova conversione, andrà perso.

CONCLUSIONI

Come abbiamo potuto constatare, gli ADC XMEGA di Atmel sono molto performanti e permettono un’alta flessibilità di configurazione, rendendoli adatti a svariati campi d’impiego, dall’acquisizione dati al controllo embedded e al trattamento di segnali (general signal processing). La panoramica fatta vuole essere soltanto una trattazione generale delle caratteristiche più salienti di questi moduli, ma facendo riferimento al sito ufficiale si può reperire tutto il materiale utile per la loro configurazione e utilizzo, compresi esempi di codice per renderli rapidamente operativi.

Grazie per l articolo, basilare per chi programma mcu. Sono andato a dare un’occhiata al datasheet dell XMega, per info la modalità di default dello stesso ADC è come si poteva intuire la UNSIGNED MODE, ma per cambiarla basta scrivere un bit “1” nella posizione del quarto bit dell ADC CONTROL REGISTER (tale posizione è chiamata CONVMODE e come detto di default ha un bit “0”) . Per i più temerari direi di provare a lavorare proprio sui registri con datasheet alla mano e linguaggio C, anziché affidarsi al sito IDE e cercare le funzioni giuste tra le varie librerie preconfezionate, si aprirebbe un mondo nuovo, ve l’assicuro 🙂

#al solito IDE