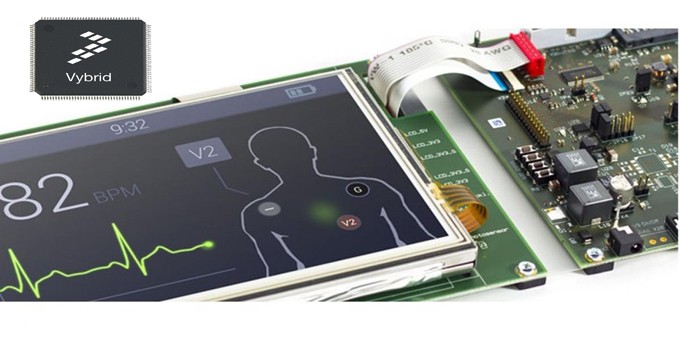

La serie Vybrid è un System on chip a bassa potenza che riesce a sfruttare un'architettura a multipocessore asimmetrico riuscendo a gestire in modo ottimale entrambi i processori di cui è dotata. L'architettura è stata realizzata dalla Freescale Semiconductor/NXP attraverso l'uso di ARM® Cortex™-A5 e, in modo opzionale, anche il Cortex™-M4; architettura attraverso la quale è possibile realizzare diverse applicazioni come application notes, un ambiente di sviluppo integrato, un ricco set di risorse per NXP e vari tools. È spesso usata, grazie alla bassa potenza richiesta, per applicazioni che richiedono connettività, grande sicurezza e controllo in tempo reale, e sta pian piano prendendo sempre più piede, diffondendosi rapidamente.

Introduzione

Se per tutte le comuni applicazioni multimediali che vengono usate è sempre più necessario un elevato throughput, vista l'elevata mole di dati che gli attuali processori devono elaborare, per applicazioni real-time questa regola non vale; in questo caso un fattore importante da tenere in considerazione è la latenza in memoria. La latenza in memoria è quel ritardo di tempo che intercorre tra due eventi (per esempio la richiesta dei dati e l'effettiva ricezione degli stessi). Questo parametro nelle applicazioni Vybrid è ridotto al minimo permettendo di creare soluzioni real time molto affidabili e complesse.

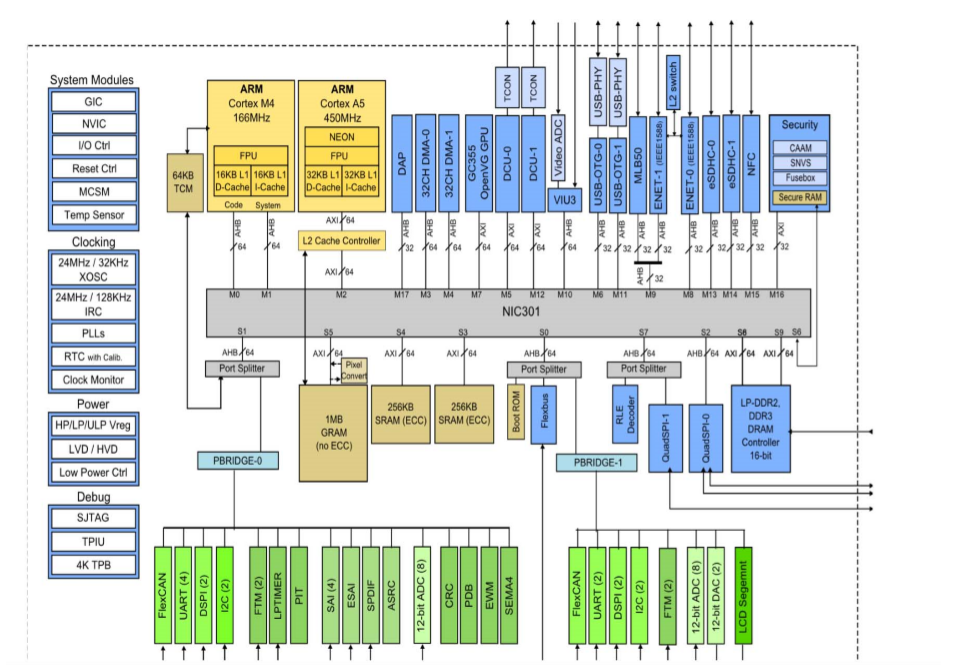

Osservando la figura 1 si può notare come la struttura dell'architettura Vybrid includa sia il Cortex-A5 sia il Cortex-M4. Se usati entrambi il primo svolge la maggior parte delle applicazioni mentre il secondo si concentra su tutte quelle applicazioni che devono essere eseguite in real time. Distinguendo questi due compiti si crea una divisione in base a ciò che deve essere gestito, separando a monte le applicazioni da eseguire.

L'architettura, inoltre, è predisposta per essere collegata con un gran numero di periferiche connesse al sistema tramite in Network Interconnect (NIC), il fulcro dell'intera struttura. Periferiche che possono essere connesse all'architettura tramite USB, CAN, SCI, SPI o in vari altri modi.

Network Interconnect (NIC-301)

Come già accennato il fulcro dell'architettura Vybrid è la sezione di Network Interconnect NIC-301 (la parte in grigio della figura 1) che crea, per l'appunto, interconnessioni tra master e slaves, determinandone il throughput massimo e, in qualche caso, aggiungendo latenza nel trasferimento dei dati.

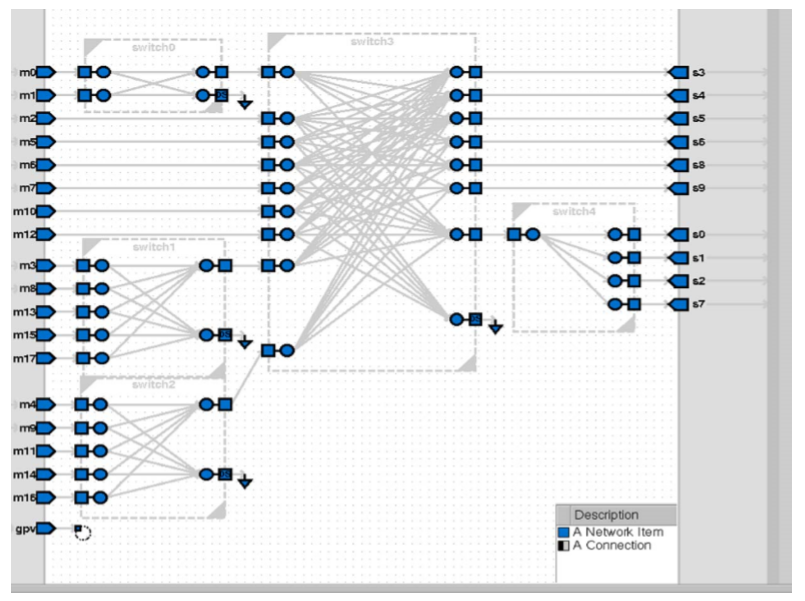

Nella figura 2 è illustrata la struttura interna di un NIC. Osservandola si può vedere come questo blocco operi fondamentalmente come un unico switch che mette in comunicazione 18 master (sulla sinistra della struttura, da m0 a m17) con 10 slave (sulla destra della struttura, da s0 a s7). Essendo impossibile avere un unico switch di tali dimensioni, il tutto è realizzato attraverso 5 switch connessi tra di loro.

Se, per esempio, il Codex-A5 (NIC m2) volesse comunicare con una delle due menorie RAM (NIC s2 o s3) si andrebbe ad attivare lo switch interno numero 3 connettendo il secondo ingresso con la prima/seconda uscita. Nello stesso istante in cui accade questo nessun altro master potrebbe comunicare con la memoria in considerazione. Se però, un master di maggiore importanza dovesse averne bisogno si interromperebbe la prima comunicazione per instaurarne una seconda. Risulta necessario programmare quindi la propria applicazione nel modo più opportuno per evitare continui switch. Questi switch avvengono perchè i nodi [...]

ATTENZIONE: quello che hai appena letto è solo un estratto, l'Articolo Tecnico completo è composto da ben 2111 parole ed è riservato agli ABBONATI. Con l'Abbonamento avrai anche accesso a tutti gli altri Articoli Tecnici che potrai leggere in formato PDF per un anno. ABBONATI ORA, è semplice e sicuro.

La latenza, ovvero il numero di cicli di clock che intercorrono tra l’inizio e la fine di un’istruzione, è sempre un problema da tener bene in mente quando si progettano soluzioni a microprocessori per applicazioni real time.