Una panoramica di alcune delle principali implementazioni del CAN sviluppate da Renesas, Fujitsu, NXP, tre tra i principali produttori al mondo nel settore.

CAN (Controller Area Network) è un protocollo di comunicazione per applicazioni real-time di controllo distribuito caratterizzato da elevata affidabilità. Gli ambiti principali d’impiego includono i settori automotive e building automation. A seguito dell’elevata diffusione dello standard e grazie ai continui progressi tecnologici dell’industria dei semiconduttori, sono sempre di più i microcontrollori che integrano a bordo controller di nodo CAN per applicazioni embedded. Di seguito è presentata una panoramica di alcune delle principali implementazioni sviluppate da Renesas, Fujitsu, Freescale ed NXP, quattro tra i principali produttori al mondo nel settore.

Renesas

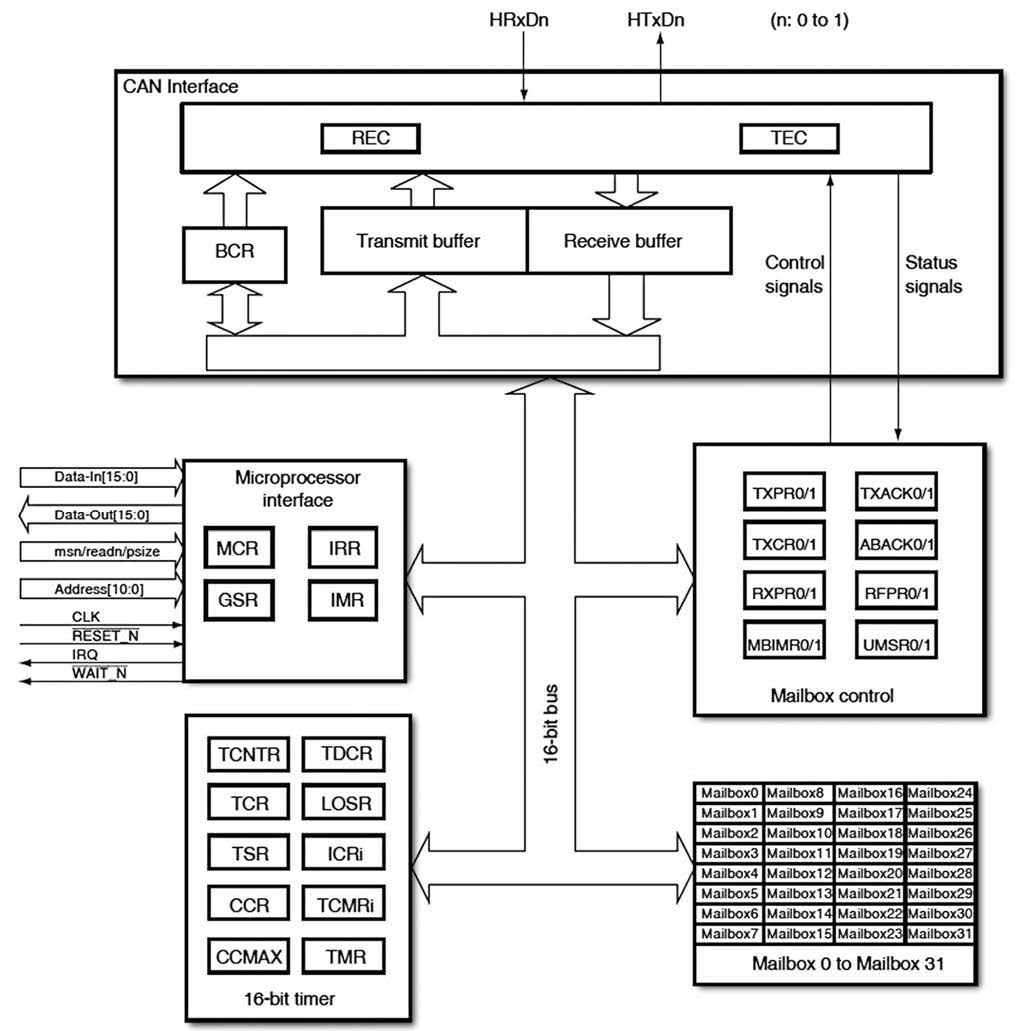

HCAN-II è, ad esempio, il controller di nodo CAN integrato nei microcontrollori della famiglia SH7000, dispositivi RISC con architettura SuperH a 32 bit di Renesas. La figura 1 mostra uno schema di principio dell’architettura interna.

Figura 1: architettura del controller HCAN-II dei micro Renesas SH7000.

Compatibile con specifiche CAN 2.0A/2.0B e ISO-11898-1, il controller supporta un data rate configurabile fino a 500 kbps (1 Mbps con certe limitazioni) ed un filtro programmabile per i messaggi in ingresso per ridurre la frequenza di interruzione del processore. Dispone di 32 mailbox per la gestione di messaggi, di cui 31 utilizzabili sia in trasmissione che in ricezione ed 1 dedicata, invece, ai soli dati in ingresso. E’ implementata una coda in hardware per la trasmissione con meccanismo di ordinamento in funzione della priorità. Il controller supporta fino a due connessioni CAN simultaneamente; ove non richiesto, tuttavia, è possibile disabilitare un canale ed espandere fino a 64 messaggi la capacità di buffering. Per migliorare le prestazioni, è inoltre prevista la possibilità di attivare automaticamente il controller per l’accesso diretto alla memoria del microcontrollore in corrispondenza della ricezione di un messaggio. Come mostrato in figura 1, il controller HCAN-II consiste di cinque diverse sezioni. L’MPI (Microprocessor Interface) consente la comunicazione con il processore host per l’accesso alle mailbox ed ai registri di controllo e configurazione. Include inoltre una logica di wake-up che consente di risvegliare il processore in risposta ad una attività sul bus CAN. Le mailbox sono aree di memoria in grado di contenere i controlli (StdID, RTR, DLC, IDE, etc.) ed i dati del messaggio, la maschera del filtro di accettazione per le transazioni in ingresso ed il timestamp del messaggio. Il controller delle mailbox gestisce la lettura e la scrittura dei messaggi. In ricezione, confronta l’ID del messaggio con i filtri previsti, genera l’indirizzo della mailbox di destinazione e vi memorizza i dati configurando opportunamente i registri di stato. In trasmissione, invece, seleziona il messaggio da inviare in base ad un algoritmo di arbitraggio che può essere configurato così da associare priorità più alta ai messaggi che abbiamo l’ID o l’indirizzo di mailbox più basso; quindi copia il messaggio dalla mailbox al buffer di trasmissione del controller di nodo. Tale controller implementa il data link layer del protocollo (DCL layer) come specificato dal livello 7 del modello OSI; implementa i contatori di errore in trasmissione e ricezione, i registri di configurazione dei parametri di tempo di bit oltre ai buffer locali per i dati in ingresso ed uscita. Il timer - un contatore free-running a 16 bit controllato direttamente dalla CPU - include tre registri di confronto utilizzabili, ad esempio, per generare ad istanti predefiniti interruzioni per applicazioni time-triggered. Sono inoltre previsti due registri a 16 bit che servono a memorizzare il tempo di ricezione di un messaggio; in questo modo, ad esempio, è possibile sincronizzare il tempo tra i diversi nodi all’interno di un sistema CAN. Il modulo HCAN-II implementa varie modalità di test che includono il solo ascolto sul bus per il rilevamento del baud rate del sistema o una capacità di autodiagnostica in cui le linee di trasmissione e ricezione sono internamente connesse. Due altre modalità di tipo Error Passive forzano il nodo a diventare passivo sotto controllo del processore host. Del tutto simile all’ HCAN-II, è l’implementazione dell’ RCAN-ET, presente a bordo dei microcontrollori della serie H8SX basati su architettura CISC. Più semplice è invece la struttura del controller implementato nei dispositivi delle famiglie R8C o M32R. Il modulo integra un controller di protocollo e la logica di filtro dei messaggi oltre ad un timer a 16-bit per segnare il tempo di ricezione. Prevede un interrupt di wake-up al processore automaticamente generato in corrispondenza della ricezione di un messaggio. Include un box con 16 slot (da 16 byte od 8 word per slot) che consente di memorizzare i messaggi; è definito un meccanismo di priorità dei messaggi dettato dal numero dello slot associato. Ogni slot può esser configurato indipendentemente come buffer di trasmissione o ricezione. Il controller supporta fino a 1 Mbps; prevede una modalità di sleep ed una di ascolto del bus.

NXP/Freescale

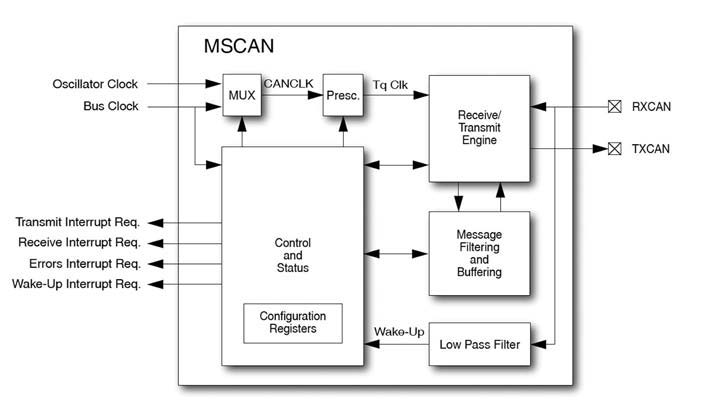

MSCAN (Motorola Scalable Controller Area Network) è invece l’implementazione del controller CAN integrata nei microcontrollori Freescale. Inizialmente progettato per dispositivi MC68HC12, MSCAN implementa il protocollo CAN 2.0 A/B utilizzando uno schema di gestione dei buffer di trasmissione e ricezione che determina un comportamento in tempo reale oltre a semplificare lo sviluppo del software applicativo. La figura 2 mostra uno schema di principio dell’architettura del modulo. Sono supportati frame dati standard ed estesi, con campi dati di lunghezza tra 0 e 8 bytes e frame remoti.

Figura 2: architettura del controller MSCAN dei micro MC68HC12 di Freescale.

Il data rate è programmabile fino a 1 Mbps. E’ implementato un buffer in ricezione di fino a 5 messaggi gestito con uno schema di tipo FIFO; quando il processore host legge un messaggio dalla coda, il controller fa scorrere automaticamente i messaggi restanti lungo la coda. E’ previsto un buffer in trasmissione di fino a 3 messaggi con gestione interna della priorità mediante concetto di ‘priorità locale’. Tra tutti i messaggi in attesa di essere spediti viene selezionato quello che è stato contrassegnato dalla priorità più alta. E’ adottato una schema flessibile di maschera dei messaggi che consente di selezionare fino a 2 identificativi estesi a 32 bit, quattro a 16 o 8 a 8 bit. Sono programmabili una funzionalità di wake-up del controller qualora si rilevi attività sul bus con un filtro passa-basso integrato per ridurre il rumore. Sono supportate una modalità di tipo loop-back per finalità di autodiagnostica ed una modalità di solo ascolto sul bus. Un timer consente il time-stamping dei messaggi in spedizione e ricezione. Per applicazioni power-saving sono previste le modalità sleep e power down. I buffer - sia di trasmissione che di ricezione - consistono di 16 byte che comprendono l’identificativo del messaggio (4 byte), il campo dati (8 byte), la lunghezza di questo (1 byte), la priorità locale del messaggio per l’arbitraggio in trasmissione ed il valore del timer interno in corrispondenza del riconoscimento del messaggio (che corrisponde, per un messaggio in uscita, al momento in cui questo è stato spedito o, per messaggi in ingresso, all’istante di ricezione). Sono inoltre previsti controlli accessori per evitare che l’utente possa violare alcune delle regole del protocollo CAN. I registri di errore in trasmissione e ricezione, ad esempio, non possono essere manipolati. Tutti i registri di controllo della configurazione non possono essere modificati se il controller è in linea; il controller deve essere forzato in una modalità di inizializzazione. I pin di uscita verso il bus vengono automaticamente configurati in uno stato recessivo quando il controller entra in modalità power down o di inizializzazione; il bit di abilitazione del controller può essere scritto una sola volta mentre il controller è in modalità operativa così da evitare che accidentalmente venga disabilitato da istruzioni errate.

Fujitsu

C_CAN è il controller di nodo CAN integrato nei microcontrollore Fujitsu della serie MB91245/S. Caratteristiche principali sono la compatibilità con la specifica CAN 2.0 A/B, il supporto di un data rate configurabile fino a 1 Mbps, la gestione di filtri per i messaggi in ingresso, la disponibilità di un buffer FIFO per i da ti in trasmissione e ricezione, la programmabilità della maschera della interruzioni generate verso il processore, il supporto di modalità di tipo loop-back e self-test. Il protocollo di gestione dei messaggi si basa su specifici oggetti, ovvero strutture dati che comprendono i dati del messaggio e tutti i controlli accessori per la comunicazione oltre alle informazioni di stato, come ad esempio l’avvenuta spedizione o ricezione. Il controller CAN comprende una memoria che consente di memorizzare fino a 32 (o 128, a seconda del modello di microcontrollore selezionato) oggetti. Una interfaccia registro dedicata consente di arbitrare gli accessi a tale memoria da parte del processore host e del controller di nodo. Nel caso siano presenti in memoria messaggi multipli in attesa di essere spediti, l’arbitraggio si basa su un meccanismo di priorità che assegna priorità più alta ai messaggi nelle locazioni più basse della memoria. In ricezione, il protocollo prevede che il controller di nodo, dopo aver decodificato i campi di controllo e di arbitraggio del messaggio, legga i dati di maschera dalla memoria per determinare la validità del messaggio corrente. L’intera memoria viene scorsa fina a riscontrare un identificativo valido. Le diverse locazioni sono scandite in sequenza a partire dall’indirizzo di base; se due oggetti, pertanto, condividono una stessa configurazione ed entrambi sono abilitati alla ricezione di un messaggio, questo verrà scritto nell’oggetto avente indirizzo più basso. In presenza di un identificativo valido, il messaggio viene copiato nell’oggetto corrispondente unitamente ad informazioni accessorie relative, ad esempio, all’arbitraggio. La CPU può quindi leggere i messaggi ricevuti presenti in memoria tramite l’interfaccia registro. In ricezione due o più oggetti possono essere configurati come una FIFO per semplificare le operazioni di lettura e gestione del buffer da parte dell’host. Piuttosto simile, sebbene in alcuni aspetti più semplice, è l’architettura dei controller integrati nei microcontrollori della serie F2CMC-16LX, i quali dispongono di un buffer di 16 messaggi in lettura e scrittura e supportano la possibilità di disabilitare la ritrasmissione automatica per le applicazioni TTCAN (ISO 11898-1) che implementano protocolli time-triggered.

STMicroelectronics

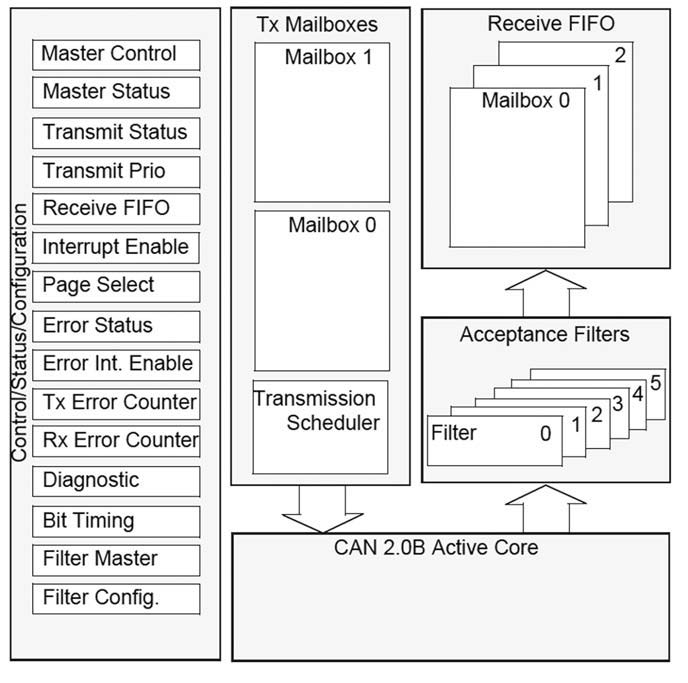

BeCAN (Basic Enhanced Controller Area Network) è il controller di nodo CAN integrato nei microcontrollori della serie ST72561 di ST-Microelectronics. Compatibile, come i moduli presentati in precedenza, con le specifiche CAN 2.0 A/B, il controller è progettato per gestire elevati flussi di messaggi tentando di ridurre il carico del processore host. La figura 3 mostra uno schema di principio dell’architettura.

Figura 3: architettura del controller BeCAN dei micro ST72561 di STMicroelectronics.

Sono previste, come si vede, due mailbox in trasmissione, con priorità programmabili, ed una in ricezione a tre stadi; sei filtri configurabili consentono di discriminare i messaggi in ingresso. Il controller supporta tre diverse modalità operative che includono una fase di inizializzazione, il normale funzionamento ed una modalità a bassa dissipazione di potenza. Due modalità di test consentono il debug dei malfunzionamenti. In modalità silente, il nodo è in grado di ricevere frame validi ma invia soltanto bit recessivi e non è in grado di iniziare una comunicazione. In modalità loop-back, invece, le linee di trasmissione e ricezione sono chiuse l’una sull’altra internamente. E’ possibile disabilitare la ritrasmissione automatica per le applicazioni time-triggered. Il protocollo per la trasmissione dei messaggi prevede che il processore host configuri le informazioni da inviare in una mailbox libera definendo identificativo, DCL e campo dati. La mailbox diventa, quindi, inaccessibile per evitare corruzione accidentale del messaggio. In presenza di più messaggi in attesa di essere inviati, viene eseguito un arbitraggio. La priorità viene selezionata in base all’identificativo del messaggio; quello più basso corrisponde alla priorità più alta. Nel caso in cui due messaggi abbiano lo stesso identificativo, viene inviato dapprima il messaggio presente nella mailbox identificata dal numero minore. In alternativa, le mailbox possono essere configurate così da creare una FIFO di trasmissione; in questo caso, la priorità più alta viene assegnata al messaggio scritto per primo nella coda. Allo stesso modo sono organizzate come una struttura FIFO le mailbox per la ricezione dei dati; tale soluzione consente di ridurre la complessità di gestione della coda di messaggi da parte del software applicativo. Come detto sono previsti fino a sei banchi di filtri per discriminare il messaggio in base all’identificativo. Ogni banco può essere configurato come: un unico filtro a 32-bit per i campi STDID[10:0], IDE, EXTID[17:0] e RTR del messaggio; due filtri a 16-bit per i campi STDID[10:0], RTR e IDE; 4 filtri ad 8-bit per STDID[10:3]; 1 filtro a 16-bit e 2 a 8-bit per queste stesse due ultime configurazioni. Per ogni filtro sono previsti un registro per la definizione dell’identificativo ed un registro di maschera (in modalità ‘identifier list mode’) o due registri per gli identificativi (in modalità ‘mask mode’). Caratteristiche simili al BeCan, presenta anche il core BxCAN (Basic Extended Controller Area Network) integrato nei microcontrollori della famiglia ST92F. Le mailboxes in trasmissione in questo caso sono 3 mentre in ricezione sono previste 2 FIFO a tre stadi; i banchi di filtri per i messaggi in ingresso sono 8. E’ inoltre prevista una modalità time-triggered per applicazioni deterministiche in tempo reale. In questa modalità il contatore interno del CAN viene attivato e usato per generare il tempo di riferimento del messaggio in trasmissione e ricezione.