In questo nuovo articolo della Rubrica Firmware Reload analizziamo alcuni accorgimenti per portare senza problemi la propria applicazione sui micro MSP430x5xxx di TI.

Introduzione

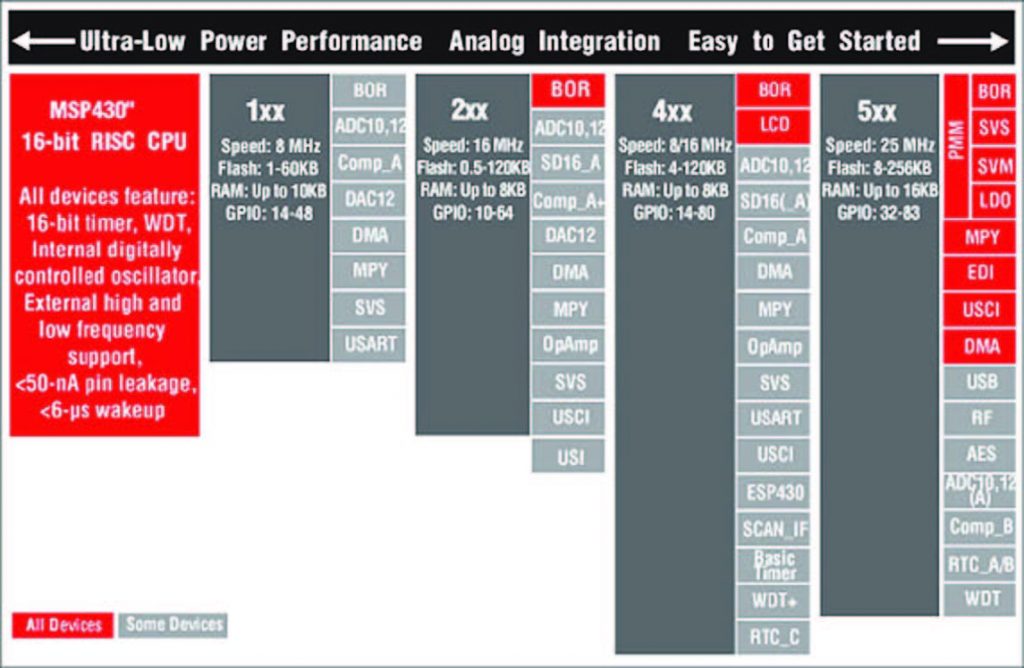

MSP430 è la serie di microcontrollori a 16 bit ultra-low-power di Texas Instruments, per applicazioni mixed-signals in ambito metering, sensori intelligenti, elettronica consumer. La famiglia comprende sei serie con oltre 200 dispositivi dalle diverse caratteristiche, come mostrato in Figura 1, per rispondere a un’ampia gamma di esigenze dell’utente.

Figura 1: la famiglia di micro-controllori MSP430: sei diverse serie per ogni esigenza

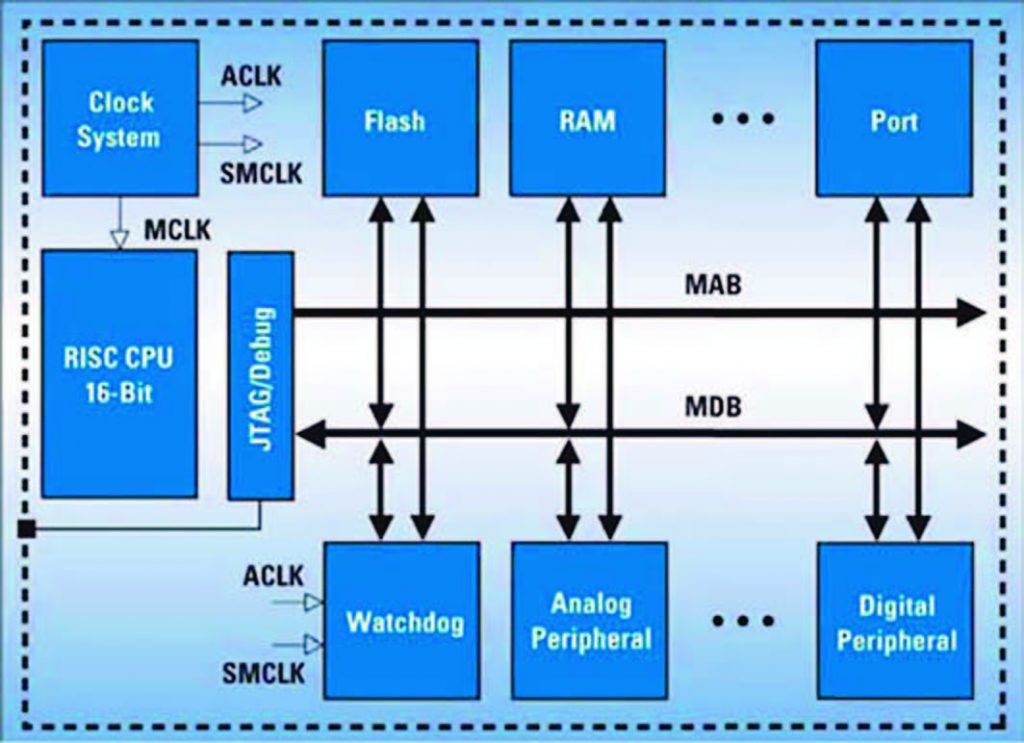

L’architettura (come mostrato in Figura 2) è di tipo von-Neuman, con bus di indirizzamento separati per la memoria programma e quella dati. La CPU è di tipo RISC a 16 bit, con insieme di istruzioni ortogonale, capacità di calcolo fino a 25 MIPS, supporto per trasferimento diretto memoria-memoria senza accesso temporaneo al register file.

Figura 2: architetture dei micro MSP430

Le periferiche sono accessibili in modalità memory-mapped. In modalità attiva ultra-low power, il consumo di potenza è di soli 120 μA con tensione di alimentazione di 2,2 V e si riduce a meno di 100 nA in shut-down. La linea di micro MSP450x5xxx introduce nell’architettura di base della famiglia MSP430 una serie di miglioramenti che consentono maggiore flessibilità, compilazione di codice più efficiente, più semplici espansioni. Anche se è mantenuta la compatibilità di massima con le versioni precedenti, il porting del codice di un’applicazione verso la suddetta famiglia richiede alcuni accorgimenti. Di seguito sono descritte in generale le linee guida a tale scopo.

PORTE DI I/O

Una delle prime differenze tra la famiglia MSP450x5xxx e le serie precedenti si trova, in particolare, nella gestione delle porte di I/O. Con la nuova famiglia sono da considerare i seguenti aspetti. I pin condivisi con la funzionalità di utilizzo di un cristallo esterno, ad esempio, sono configurati al power-up come porte. Pertanto, prima di commutare in tale modalità di clock, è necessario programmare la configurazione dei pin rilevanti. Inoltre, è necessario configurare come uscite tutti i pin del dispositivo non utilizzati, qualora non siano connessi al PCB, oppure come ingressi, abilitando, in questo secondo caso, i resistori di pull-up o pull-down. In caso contrario potrebbero generarsi correnti di perdita che influirebbero sul consumo ridotto nelle modalità low-power del micro.

L’abilitazione dei resistori di pull-up/pull-down, unitamente alla programmazione della capacità di driving del pin stesso, è gestita attraverso i registri PxDS. Vi è poi una funzionalità interessante accessoria che è stata introdotta nella serie MSP450x5xxx, ovvero un vettore di interrupt sulla porta P1. Le linee di interruzioni sono abilitabili e mascherabili singolarmente mentre il vettore è gestito a priorità; il valore della linea a più alta priorità asserita è riportato nel registro P1IV. Pertanto, una routine di gestione dell’interrupt può essere del tipo mostrato nel Listato 1. Come si vede, il valore del registro P1IV viene sommato al valore corrente del Program Counter per determinare quale istruzioni di salto eseguire; ogni salto punta, evidentemente, alla routine di gestione della singola interruzione (per brevità nel listato è riportato solo l’esempio della linea 7).

;Interrupt handler for P1 Cycles P1_HND ... ; Interrupt latency 6 ADD &P1IV,PC ; Add offset to Jump table 3 RETI ; Vector 0: No interrupt 5 JMP P1_0_HND ; Vector 2: Port 1 bit 0 2 JMP P1_1_HND ; Vector 4: Port 1 bit 1 2 JMP P1_2_HND ; Vector 6: Port 1 bit 2 2 JMP P1_3_HND ; Vector 8: Port 1 bit 3 2 JMP P1_4_HND ; Vector 10: Port 1 bit 4 2 JMP P1_5_HND ; Vector 12: Port 1 bit 5 2 JMP P1_6_HND ; Vector 14: Port 1 bit 6 2 JMP P1_7_HND ; Vector 16: Port 1 bit 7 2 P1_7_HND ; Vector 16: Port 1 bit 7 ... ; Task starts here RETI ; Back to main program 5

| Listato 1 |

POWER MANAGEMENT MODULE (PMM)

Il PMM è invece uno dei nuovi moduli presenti a bordo dei micro della serie MSP450x5xxx, introdotto nell’ottica di una migliore gestione dei consumi. Tra le varie funzionalità, il modulo ha il compito di generare, derivandola dalla tensione esterna DVCC , la linea di alimentazione VCORE usata dalla CPU, dalle memorie (flash/RAM) e dai moduli digitali. Include un regolatore LDO programmabile, in modo che la tensione di lavoro VCORE possa essere impostata in accordo alla frequenza di funzionamento del sistema. Ad esempio, a una frequenza di 12 MHz, la tensione interna della CPU può essere ridotta fino a 1,25 V.

Oltre all’LDO, il modulo PMM include circuiti SVS ed SVM per il monitoring delle tensioni interne, in grado di generare reset della CPU nel caso di failure sulla linea di alimentazione. Sebbene consente, dal punto di vista della riduzione dei consumi, interessanti applicazioni, la gestione del modulo PMM deve essere fatta con accortezza, per evitare, ad esempio, di generare reset non intenzionali da parte dei circuiti di supervisione, durante la commutazione della tensione di core o, diversamente, di impostare una frequenza di clock non compatibile con la tensione di core corrente. Le librerie di supporto per i micro della serie MSP450x5xxx includono, ovviamente, funzioni per la gestione ‘sicura’ a più alto livello del modulo. A titolo di esempio riportiamo nel Listato 2 uno schema di riferimento per una generica funzione per l’incremento della tensione di core.

void SetVCoreUp (unsigned int level)

{

// Open PMM registers for write access

PMMCTL0_H = 0xA5;

// Make sure no flags are set for iterative sequences

while ((PMMIFG & SVSMHDLYIFG) == 0);

while ((PMMIFG & SVSMLDLYIFG) == 0);

// Set SVS/SVM high side new level

SVSMHCTL = SVSHE + SVSHRVL0 * level + SVMHE + SVSMHRRL0 * level;

// Set SVM low side to new level

SVSMLCTL = SVSLE + SVMLE + SVSMLRRL0 * level;

// Wait till SVM is settled

while ((PMMIFG & SVSMLDLYIFG) == 0);

// Clear already set flags

PMMIFG &= ~(SVMLVLRIFG + SVMLIFG);

// Set VCore to new level

PMMCTL0_L = PMMCOREV0 * level;

// Wait till new level reached

if ((PMMIFG & SVMLIFG))

while ((PMMIFG & SVMLVLRIFG) == 0);

// Set SVS/SVM low side to new level

SVSMLCTL = SVSLE + SVSLRVL0 * level + SVMLE + SVSMLRRL0 * level;

// Lock PMM registers for write access

PMMCTL0_H = 0x00;

}

| Listato 2 |

La sequenza è la seguente:

1) programmare le soglie alte dei registri dei supervisori SVM ed SVS in accordo al livello di tensioni che si intende impostare, per evitare reset non intenzionali;

2) impostare mediante il registro PMMCOREV il prossimo valore di tensione di core desiderato;

3) attendere che la tensione di core impostata sia raggiunta;

4) programmare la soglia bassa per il monitor di tensione SVS, in accordo al nuovo livello di tensione impostato.

Come si vede, il PMM include un registro di controllo (PMMCTL_0) che deve essere opportunamente configurato per consentire la riprogrammazione delle caratteristiche del modulo. Ciò previene da modifiche accidentali della configurazione di sistema.

TIMER

I due timer A e B dei micro MSP450x5xxx hanno le stesse caratteristiche di quelli dei modelli delle serie precedenti e, in aggiunta, dispongono di un secondo divisore di clock che gli consente così di funzionare a frequenze di conteggio ancora più basse. Sono quindi stati introdotti i registri accessori TAxEX0 e TBxEX0 per l’impostazione del valore di divisione ulteriore desiderato. Nel portare il proprio codice sviluppato per modelli precedenti sui micro MSP450x5xxx, inoltre, è opportuno verificare la mappa dei registri dei timer suddetti in quanto, ad esempio, il vettore di overflow è stato spostato all’offset 0x0E invece che 0x0A come in passato.

ADC

Un discorso analogo vale all’incirca anche per i convertitori ADC, per i quali sono state introdotte alcune funzionalità accessorie, come ad esempio l’introduzione di un divisore addizionale per il clock di funzionamento (e quindi del relativo registro di configurazione ADC12PDIV) o la possibilità di configurare, mediante i campi ADC12RES ed ADC12DF, la risoluzione di campionamento (selezionandola tra 8, 10 o 12 bit) e il formato dei dati digitalizzati (scegliendo tra le convenzioni binario unsigned e complemento a 2). L’ADC può funzionare con frequenza di campionamento da 50 ksps (per applicazione low power) a 200 ksps, impostabile mediante i bit di controllo ADC12SR. Inoltre, rispetto ai dispositivi della precedente serie MSP430x2xxx, è importante sottolineare come il trasferimento dei dati dalla memoria del convertitore è ora facilitato dall’uso della periferica DMA che, tra l’altro, supporta fino a 8 canali indipendenti.

FLASH

Tra le caratteristiche più interessanti introdotte nella serie MSP430x5xxx per quanto concerne la flash, vi sono l’utilizzo di un oscillatore dedicato che non richiede configurazione, la possibilità di cancellare un banco mentre è in corso la programmazione di un altro, la scrittura in modalità long word singola o a blocchi e il supporto per l’accesso in lettura in modalità ‘marginal read’. Tale caratteristica, in particolare, può essere utile per verificare l’integrità dei dati memorizzati, consentendo infatti di rilevare celle di memoria programmate non sufficientemente e contenenti un ‘1’ (bit cancellato) o uno ‘0’ (bit programmato). Così, per identificare blocchi di memoria programmati in maniera non affidabile, è sufficiente rileggere i dati nella modalità normale e in quella ‘marginale’, calcolare il relativo CRC e confrontare i due valori. Se non tornano, la programmazione del banco è non ‘affidabile’. Le operazioni in modalità ‘marginal read’ sono controllate mediante i registri di controllo MRG0 e MRG1. Fare attenzione al fatto che, in modalità ‘marginal read’, la velocità di accesso alla flash deve essere limitata a 1 MHz.

RTC

Piuttosto diversa è invece l’architettura dell’RTC che comprende il Basic Timer della precedente serie, in aggiunta ad altre funzionalità, in grado di operare senza intervento della CPU. Tra queste vi sono, ad esempio, la capacità di correzione dell’offset e quella di allarme, con la possibilità così di generare interruzioni verso il processore a istanti programmati o periodicamente. A tali scopi sono stati quindi aggiunti i registri RTCCTL2 e RTCCTL3 per la calibrazione dell’offset e quello RTCCTL0 per la configurazione delle suddette interruzioni, oltre ai registri dedicati alla programmazione della modalità calendario della periferica. Il registro RTCIV sostituisce quello che in precedenza era implementato dai registri IE2 ed IFG2, e riporta l’offset da addizionare al Program Counter per gestire i salti all’interno dell’interrupt handler primario associato all’RTC.

USCI

Le differenze principali per quanto riguarda la periferica USCI riguardano invece la generazione delle interruzioni. In modalità I2C, ad esempio, queste sono state unificate in un unico vettore in modo da supportare una gestione più efficiente e lineare degli interrupt, sullo base di uno schema analogo a quanto appena descritto per l’RTC o in precedenza in dettaglio maggiore (si veda il Listato 1), per i pin di I/O della porta P1. In modalità SPI ed UART sono invece state separate le sorgenti di interruzioni per gli eventi di trasmissione e ricezione di dati. Per quanti intendano invece migrare verso l’impiego delle periferiche eUSCI incluse nei micro MPS430x5xxx, è bene verificare nel dettaglio le differenze con la versione USCI.

In modalità UART, ad esempio, sono state introdotte due nuove sorgenti di interruzione UCSTTIE ed UCTXCPIE. La prima è asserita al termine della trasmissione dei dati mentre la seconda al momento della ricezione del bit di start. Si noti che la flag TXIFG segnala invece lo svuotamento della FIFO di trasmissione e quindi è asserita al momento in cui l’ultimo dato da trasmettere è stato caricato nel registro di uscita per la serializzazione. Sempre in modalità UART è stata aggiunta nel modulo eUSCI la possibilità di programmare la durata dei glitch della linea in ricezione, che vengono filtrati, e sono stati forniti nuovi modi di generazione del baud rate di trasmissione. Si faccia inoltre attenzione al fatto che alcuni registri sono stati estesi a 16 bit e quindi è opportuno accedere a questi mediante indirizzamento a word. In modalità I2C, invece, la caratteristica più interessate introdotta con i modelli FR5xxx è la possibilità di implementare sulla stessa porta di comunicazione più dispositivi slave, ognuno con indirizzo dedicato e proprie flag di interruzione associate agli eventi di trasmissione e ricezione di un carattere.