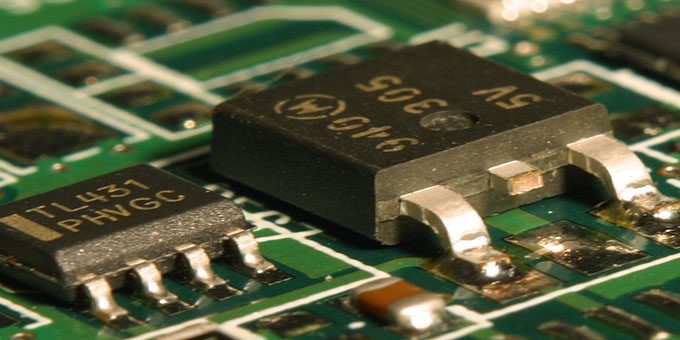

Sono di varie forme e dimensioni ma tutti hanno il medesimo scopo: proteggere il chip al suo interno, consentirne sia la dissipazione di calore verso l’esterno che la connessione al circuito elettronico di cui farà parte.

Adistanza di circa di cinquant’anni dalla realizzazione del primo circuito integrato, oggi il mercato della componentistica elettronica conta una numerosa moltitudine di circuiti integrati, i quali, esternamente, si distinguono per il loro package o contenitore. La pressante spinta evolutiva di questi componenti a semiconduttore, regolata dalle attuali tecnologie di produzione automatizzate, inevitabilmente trascina con sé il problema dell’inscatolamento, ovvero la realizzazione del package più idoneo al funzionamento ed al montaggio dello stesso IC su un circuito.

Nota storica

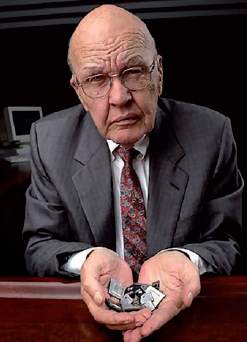

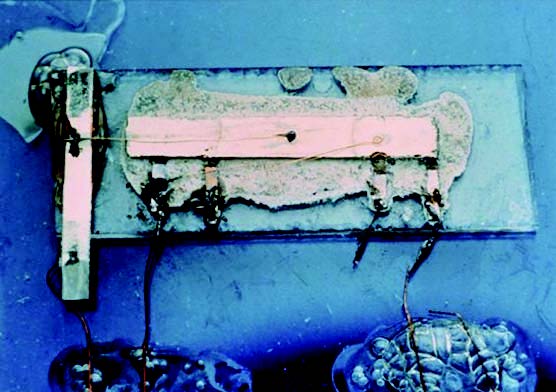

Storicamente l’invenzione del circuito integrato viene attribuita al premio Nobel Jack Kilby il quale, nell’ormai lontano 1958, realizzò un circuito oscillante integrato impiegando una barretta di germanio. Kilby, nato nel Missouri nel 1923, dopo i suoi studi liceali, presentando una tesi in ingegneria elettronica, consegue nel 1947 una laurea in scienze presso l’università dell’Illinois. Trascorsi i difficili anni contraddistinti dai tragici eventi della seconda guerra mondiale, credendo ancora nelle potenzialità offerte dalla scienza, Kilby nel 1950 ottiene un master presso l’università del Wisconsin. In seguito viene assunto dalla Texas Instruments, in qualità di neo ingegnere. Lo studio da lui condotto nell’estate del 1958, in merito al problema della progettazione dei circuiti noto come “la tirannia dei numeri”, ovvero l’impossibilità di aumentare la densità dei componenti di un elaboratore, lo portò alla conclusione che l’unica soluzione più logica fosse quella di integrare un gran numero di componenti su di un unico pezzo di semiconduttore (il germanio in questo caso). Il 12 settembre di quello stesso anno espose le sue conclusioni ai responsabili della Texas, con tanto di primo circuito integrato oscillante alla mano! Nacque così il brevetto che diede il via alla produzione dei primi IC (Integrated Circuit), rilasciati a partire dal febbraio del 1959. L’anno seguente, a soli sei mesi di distanza da quella famosa estate, Robert Noyce, uno dei fondatori della Intel e allora cofondatore della Fairchild Semiconductor, realizzò il primo IC al silicio, aprendo così nuove frontiere tecnologiche basate sull’uso di questo semiconduttore. Il brevetto venne riconosciuto alla Texas Instruments da tutti i paesi del mondo, fatta eccezione del Giappone che, nonostante ciò, in seguito divenne il maggiore produttore di circuiti integrati. Solo per la terza generazione di calcolatori il circuito integrato risulterà l’elemento fondamentale.

Figura 1: Jack Kilby, l’inventore del microchip, ricevette il premio Nobel per la fisica nel 2000 in coppia a Robert Noyce.

Il package

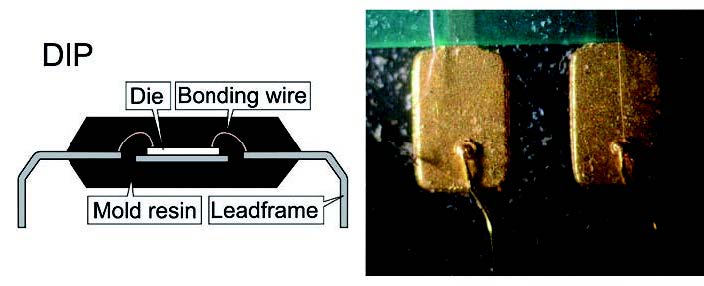

In generale col termine package si intende quel contenitore che racchiude una o più tipologie di componenti elettronici. Forma, dimensione e materiale dipendono dal tipo di dispositivo, dal calore che deve esser in grado di smaltire verso l’ester no, dal numero di connessioni col circuito esterno, nonché dal tipo di montaggio che si intende realizzare sulla scheda elettronica o circuito che ne fa uso. I packages generalmente sono standard, fanno eccezione alcune versioni custom usate talvolta dalle aziende di elettronica per particolari prodotti di nicchia, quali gli strumenti di misura di classe elevata. Nel caso dei microprocessori, dispositivi questi con un alto grado di integrazione, il package riveste il die ovvero il mattoncino di semiconduttore che integra tutti i componenti del processore stesso. Il contenitore di un IC riporta all’esterno la piedinatura del circuito che trova alloggiamento al suo interno, e ciò grazie a minuscoli collegamenti a filo congiungenti i diversi pad del mattoncino di semiconduttore col relativo pin o reoforo esterno. Le sue dimensioni sono generalmente piuttosto maggiorate rispetto a quelle del semiconduttore, e ciò per svariati motivi: uno di questi è la neccessità di spazio richiesta dalle numerose connessioni a filo, così come l’ovvia necessità di maneggevolezza dell’IC stesso durante le fasi di assemblaggio, di saldatura o di alloggiamento sugli appositi zoccoli delle schede elettroniche finali. Ad esempio, per un die da 2-3 cm² il package può tranquillamente avere una superficie di 20 cm². Inoltre, un altro fattore non meno importante è l’esigenza di dissipare all’esterno più o meno fortemente il calore prodotto dal funzionamento del chip. Il processo di packaging può inglobare più di un die di differente tipo, assieme a componenti passivi quali resistori e condensatori, come nel caso degli IC ibridi. Il materiale impiegato per la sua realizzazione può essere sostanzialmente di quattro tipi: resina plastica, metallo, ceramica o combinazioni di questi. La scelta tra uno di questi dipende fortemente da diversi fattori, come la capacità di dissipare il calore, il costo finale, la qualità richiesta per l’IC ed il tipo di assemblaggio al quale verrà sottoposto lo stesso integrato. Lo stato dell’arte dei circuiti integrati contempla numerosi tipi e sottotipi di package, in modo da rispondere adeguatamente alle necessità sopra elencate. L’avvento della tecnologia SMT (Surface-Mount Technology), che ha iniziato a diffondersi alla fine degli anni ‘80 grazie all’IBM ebbe, come conseguenza inevitabile, un aumento progressivo del numero di package per IC. Le sigle che li contraddistinguono sono ad oggi piuttosto numerose, tanto che sarebbe necessario un intero libro per poterli descrivere tutti con tanto di spiegazioni tecniche e fotografie. In questo articolo dunque viene presentata una panoramica dei vari tipi di package per IC, elencandone alcuni di quelli più conosciuti assieme ai diversi sottotipi:

» DIP (Dual Inline Package): PDIP (Plastic DIP), SDIP (Shrink DIP), CERDIP (Ceramic DIP), DIP-Tab (DIP with Metal heatsink);

» SIP (Single Inline Package);

» TO: TO-3, TO-5, TO-6, TO-8…TO-52, TO-55…TO-92, TO-93, TO-94…TO-100…TO-126, TO-127…TO-220…;

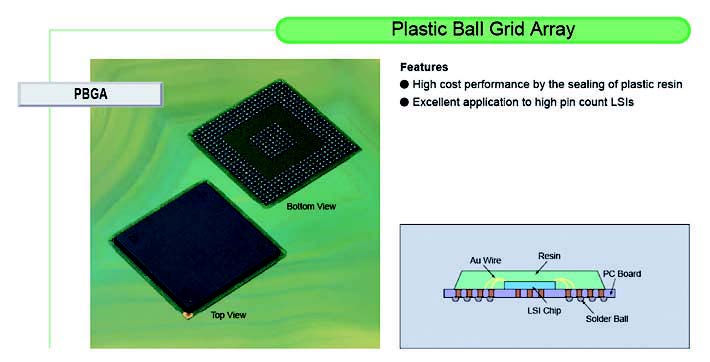

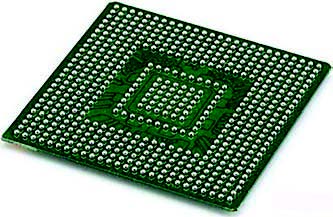

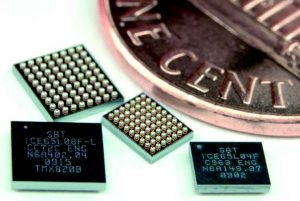

» BGA (Ball Grid Array): CABGA (Chip Array BGA), SSBGA (Small Scale BGA), CBGA (Ceramic BGA), EBGA (Enhanced BGA), FBGA (Fine pitch BGA), HSBGA (Heat Slug BGA), LBGA (Low-Profile BGA), FCBGA (Flip Chip BGA), LFBGA (Lowprofile Fine-pitch BGA), MCMCABGA (Multi Chip Module Chip Array BGA), MCMBGA (Multi Chip Module BGA), PBGA (Plastic BGA), SBGA (Super BGA), BGA (micro BGA);

» PGA (Pin Grid Array);

» QFP (Quad Flat Pack): CQFP (Ceramic QFP), LQFP (Low-Profile QFP), MQFP (Metric QFP), PQFP (Plastic QFP), TQFP (Thin QFP), ETQFP (Extra Thin QFP), VQFP (Very-thin QFP);

» SOP (Small Outline Package): MSOP (Micro SOP), PSOP (Plastic SOP), QSOP (Shrink Small Outline narrow body Package), SSOP (Shrink SOP), TSOP (Thin SOP), TSSOP (Thin Shrink SOP), VSOP (Very SOP), TVSOP (Thin Very SOP);

» LCC (Leaded Chip Carrier): DLCC (Dual Leaded-less Chip Carrier Ceramic), JLCC (J-Leaded Chip Carrier), LCCC (Leaded Ceramic Chip Carrier), MLCC (Micro Leadframe Chip Carrier), PLCC (Plastic LCC);

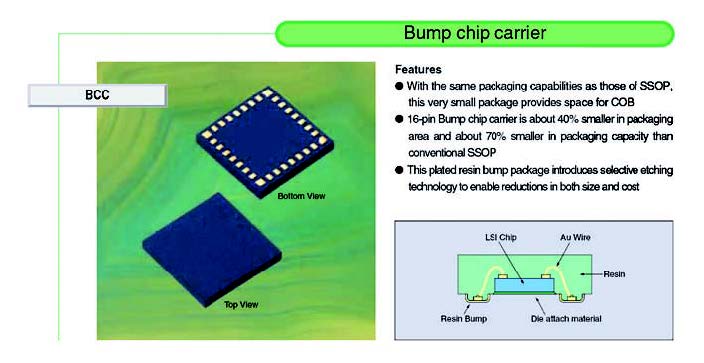

» BCC (Bump Chip Carrier);

» CFP (Ceramic Flat Pack);

» DFN (Dual Flat pack No-lead);

» QFN (Quad Flat No-lead);

» SOIC (Small Outline);

» SOT (Small Outline Transistor): TSOT (Thin SOT).

Dando un’occhiata alle fotografie di questi package, si comprende bene come siano in grado di rispondere in maniera molto diversificata alle diverse modalità di connessione col circuito che fa uso di quel particolare IC. E ciò in termini sia di numero di pin che di densità di pin. Questo è un aspetto di particolare importanza se si considera che gli IC diventano ogni gior no sempre più complessi e multifunzionali. Di questo lungo elenco solamente i primi tre tipi (SIP, DIP e TO) non sono a montaggio superficiale (SMD), aspetto questo che la dice lunga su come il mercato degli IC si sia orientato sempre più verso la SMT. Questa tecnologia ha infatti un impatto sui costi di produzione piuttosto significativi, offrendo la possibilità di risparmiare nei materiali, risparmiare sulla produzione dei PCB (Printed Circuit Board) sia perché non è più necessario andare a praticare tanti fori, sia perché il montaggio sulle linee robotizzate risulta essere notevolmente più semplificato. Oltretutto la SMT apporta ovvi vantaggi in termini di miniaturizzazione delle schede e, di conseguenza, permette di realizzare dispositivi portatili e di peso ridotto. I tipi DIP e TO sono adesso piuttosto obsoleti. Tuttavia in certi settori risultano ancora piuttosto utili, come nel campo della prototipazione elettronica, dell’hobbistica e del controllo di potenza. Questo perchè l’IC impacchettato secondo lo standar DIP, SIP o TO risulta sicuramente più facile da maneggiare al di fuori delle catene di montaggio e dei laboratori elettronici. Il formato DIP venne sviluppato nel 1965 dalla Fairchild al fine di ottimizzare lo spazio occupato dai circuiti integrati i quali, fino ad allora, avevano forma circolare. Questo fece sì che si potessero realizzare schede per computer più compatte e capaci di inglobare tutti i circuiti integrati necessari al funzionamento delle stesse. Ecco che il DIP diviene il package standard ed il più utilizzato dalle industrie di microelettronica negli anni ’70 ed ‘80.

Figura 2: il primo circuito integrato su piastrina di germanio.

Figura 3: bonding in un DIP.

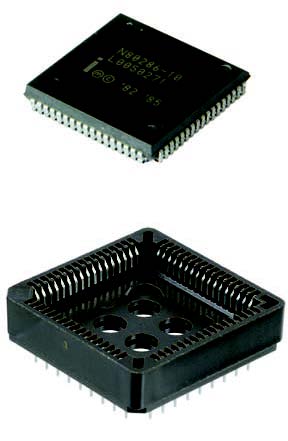

Figura 4: PLCC (Plastic Leaded Chip Carrier).

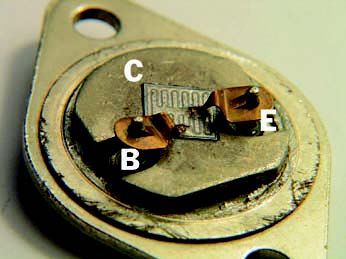

Figura 5: Interno di un powertransistor

in contenitore TO-3.

Evoluzione del packaging

Nei primi tre decenni seguenti la comparsa sul mercato del primo circuito integrato, il problema del packaging (impacchettamento) è stato sempre visto, in fase di produzione, come un problema secondario, considerato il fatto che il package doveva assicurare solamente la protezione del semiconduttore e la sua manipolazione. Con l’aumento del livello di integrazione, e quindi della possibilità di realizzare dispositivi elettronici con un numero a crescita esponenzialmente di componenti su di un unico supporto di semiconduttore (monolitico – tecnologia SoC System-On-Chip), si è posto nuovamente il problema del packaging. IC complessi comportano inevitabilmente lo studio e la scelta di soluzioni legati all’elevato numero di pin esterni (e quindi di collegamenti tra il DIE ed i pin stessi), velocità di funzionamento, dissipazione di calore crescente con la densità dei componenti integrati, interconnessione con le schede elettroniche eccetera. La nascita negli anni ’90 di package tipo BGA (Ball Grid Array), WLP (Wafer Level Packaging) e CSP (Chip Scale Packaging), rappresentano alcune delle prime risposte ai problemi menzionati. La necessità di una sempre più spinta integrazione accompagnata dalla necessità di affiancare tra loro tecnologie di produzione differenti, come nel caso dei microprocessori e dei sistemi a radiofrequenza, ha portato a soluzioni alternative più avanzate. Si pensi ad esempio al mercato consumer come quello degli smartphone di ultima generazione, in grado di coinvolgere sistemi di telefonia mobile, GPS, sistemi fisico/meccanici come gli accelerometri e tanto altro, oppure alle memorie che devono essere sempre più piccole e capienti. Nel caso, ad esempio, dei microprocessori, la necessità di una sempre maggiore potenza di calcolo ha portato alla nascita dei multicore, ovvero processori che inscatolano più core assieme e, in alcuni casi, più die. La possibilità di poter inglobare su di uno stesso package tecnologie differenti, apre dunque le porte ad IC sempre più complessi e con funzionalità sempre più differenziate e potenti. Se inizialmente si pensò di disporre più chip in orizzontale, lavorando quindi a livello bidimensionale (assi X e Y), adesso l’idea è quella di sfruttare anche la terza dimensione (asse Z), ovvero disporre i sotto-circuiti integrati anche in verticale. Parliamo dunque di package 3D. Questa frontiera, che oggi costituisce una realtà in via di consolidamento ed evoluzione, comporta inevitabilmente problematiche non di poco conto, alcune di queste sono:

» far coesistere sistemi diversi in spazi comuni pone problematiche inerenti le derive termiche dovute al calore prodotto dai chip posti sopra e sotto, oltre che in senso orizzontale;

» i collegamenti elettrici a filo tra il pinout dei chip e il pinout esterno è reso decisamente più difficoltoso;

» resistenza alle sollecitazioni meccaniche e quindi resistenza alle cadute e alle vibrazioni;

» scelta dei materiali più idonei per il package;

» difficoltà nell’esecuzione dei test elettrici, termici, meccani dei singoli sottostadi dell’IC finale.

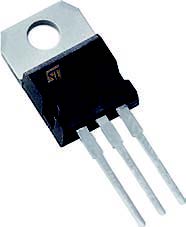

Figura 6:

contenitore TO-92.

Figura 7: contenitore TO-100

Figura 8: Contenitore

TO-220 – Fonte: ST

Microelectronics.

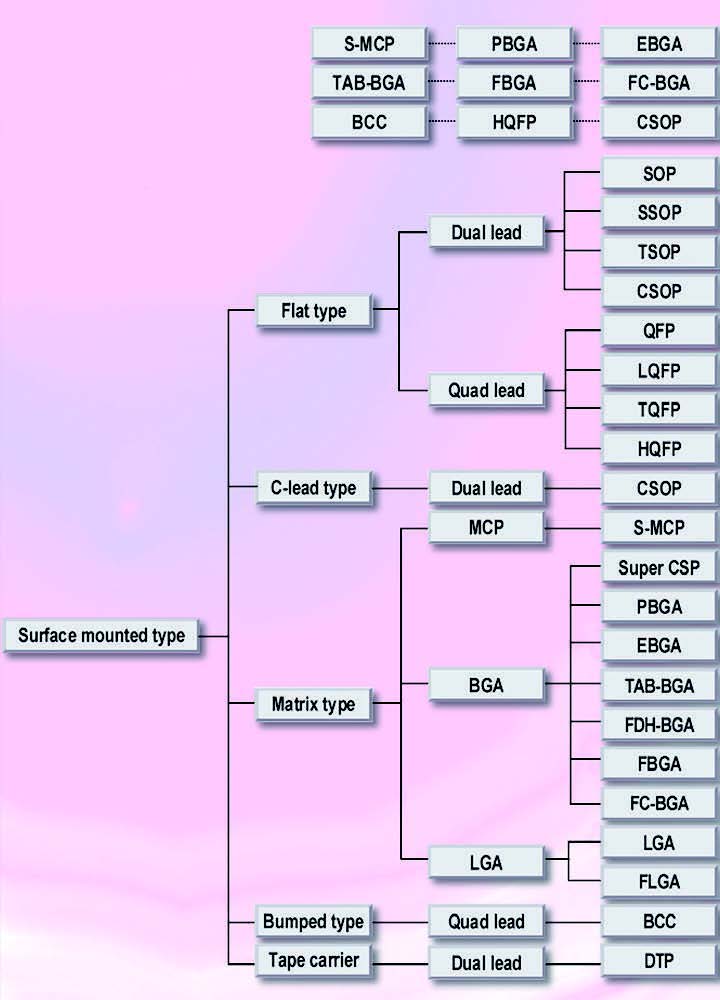

Figura 9: Classificazione package per IC in tecnologia SMT - Fonte: Fujitsu Microelectronics.

Ad oggi due sono le strade che si tentano di sviluppare, quella del System-In-A-Package (SiP) e del Wafer Level 3D Packaging (WL-3D). Primi esempi di SiP sono gli MCM (Multi Chip Module) ed gli MCP (Multi Chip Package), entrambi basati sull’uso di un substrato di ceramica o laminato o metallico sul quale andare ad integrare componenti passivi e a semiconduttore. Il WL-3D sfrutta invece le infrastrutture del WLCSP (Wafer Level Chip Scale Package), in cui il die fa anche da package. In questo caso si riducono drasticamente i collegamenti a filo tra i diversi sotto-circuiti, grazie alla produzione di vias attraverso i wafer. Ecco allora come lo stacked package, ovvero l’impacchettamento di die diversi realizzati con tecnologie diverse, si stia facendo sempre più pressante e presente. Da un punto di vista progettuale i vantaggi sono notevoli e nascono dal fatto che ciascun blocco funzionale, realizzato con la propria tecnologia e quindi con macchinari e processi già consolidati, rappresenta la soluzione ad un sottoproblema, ovvero un singolo aspetto funzionale dell’IC completo.

Figura 10: PBGA (Plastic Ball Grid Array) - Fonte: Fujitsu Microelectronics

Figura 11: BCC (Bump Chip Carrier) - Fonte: Fujitsu Microelectronics.

Figura 12: PGA (Pin Grid Array) - Fonte: IBM.

Figura 13: BGA (Ball Grid Array) - Fonte: techfuels.com.

Figura 14: TSOP (Thin SOP).

Figura 15: TQFP (Thin Quad Flat Package) - Fonte: Altera.

Figura 16: WLCSP (Wafer Level Chip Scale Package).

Figura 17: Differenza tra un SiP (System-in-A-Package) ed un SoC (System On Chip) – Fonte: necel.com.