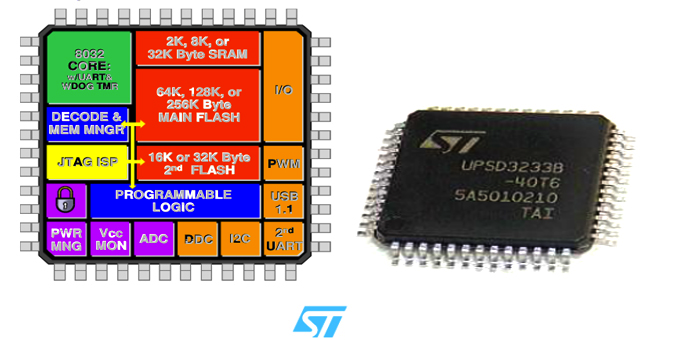

I microcontrollori uPSD della ST microelectronics sono una delle innumerevoli varianti realizzate su core 8051 ed immesse sul mercato molti anni fa. In questo caso ST ha integrato in un unico package il core 8051 e una periferica PSD. Unendo questi due componenti ha ottenuto dei dispositivi che integrano in un package QFP due memorie flash una memoria ram e due PLD. La doppia flash semplifica anche la realizzazione di un driver IAP (In Application Programming) per l’aggiornamento del firmware applicativo. Verranno inizialmente presentate le caratteristiche dei diversi moduli del uPSD, successivamente si esamineranno i software per la loro configurazione e programmazione, infine verrà descritto un esempio applicativo realizzato per uPSD33xx.

IL CORE 8051 DEL UPSD

La famiglia uPSD32xx si basa sul core classico 8051 con 12 cicli di clock per istruzione, poiché il clock può arrivare a 40MHz, un uPSD32xx può raggiungere i 3Mips di picco. All’interno del core sono presenti tutte le periferiche standard di un core 8051: tre timers a 16bit, due porte seriali e la periferica hardware per la gestione di un’interfaccia I2C sia in modalità master che in modalità slave. La SIE (Serial engine interface) del uPSD può gestire tre endpoint: l’endpoint0 bidirezionale e due endpoint di tipo IN (sola lettura) con modalità di trasferimento a interrupt. Completano la dotazione delle periferiche un convertitore ADC a 8bit su quattro canali multiplexati e una periferica PWM a 8bit. L’evoluzione della famiglia uPSD32xx è la famiglia uPSD33xx. In questo caso il core esegue le istruzioni in 4 cicli di clock e perciò può raggiungere i 10MIPS, per questo è stata anche denominata turbo uPSD. Inoltre è stato implementato un doppio registro DPTR per l’accesso alla memoria esterna del dispositivo che semplifica le procedure di trasferimento dati tra aree diverse di memoria. In questa famiglia le periferiche USB e PWM sono state sostituite da una periferica con doppio PCA (Program Counter Array) e da una porta di comunicazione SPI, configurabile solo in modalità master. Inoltre, alla porta seriale, è stata aggiunta la possibilità di comunicazione secondo lo standard IrDa. Il convertitore AD è stato aggiornato: si tratta di un SAR a 10bit con otto canali multiplexati e ingresso per la Vref dedicato. Come il suo predecessore anche per i uPSD33xx esistono versioni alimentate a 5V e 3.3V. In questo caso però il core è sempre alimentato a 3.3V mentre la periferica PSD può essere alimentata sia a 3.3V che a 5V. Utilizzando la versione con PLD alimentata a 5V si può facilmente interfacciare periferiche con tensioni di lavoro diverse. Gli I/O del micro infatti funzionano a 3.3V ma sono 5V tolerant in ingresso, mentre gli I/O del PSD funzionano a 5V. Un'altra famiglia è uPSD34xx denominata anche turbo plus rappresenta la sintesi delle due famiglie precedenti. Per aumentare la velocità di esecuzione del codice il core è stato ulteriormente migliorato con l’aggiunta di una coda di prefetch con accesso a 16bit alla memoria programma e di una branch cache. La coda di prefetch legge dalla memoria i quattro byte successivi all’istruzione in esecuzione durante la decodifica di quest’ultima. La tecnica di prefetch però fallisce se l’esecuzione sequenziale del codice è interrotta da un’istruzione di salto. In questa circostanza viene in aiuto la branch table che memorizza gli indirizzi delle ultime quattro istruzioni di salto eseguite. Se l’indirizzo di arrivo di un’istruzione di salto è presente nella branch table, la coda di prefetch viene aggiornata copiando i quattro byte di codice dalla branch table senza ulteriori ritardi nell’esecuzione del codice. Altrimenti il processore entra in stallo e attende finché la coda di prefetch non viene aggiornata con le letture dal nuovo indirizzo. L’utilizzo della coda di prefetch, che può essere disabilitata, può provocare comportamenti imprevedibili non facilmente individuabili quando si esegue codice memorizzato su più banchi di memoria. Il cambio banco infatti comporta la perdita di sincronizzazione della coda di prefetch che può portare all’esecuzione di istruzioni casuali. Prima di ogni bank switch si deve perciò disabilitare la coda per invalidare il suo contenuto ed eventualmente riabilitarla dopo lo switch del banco. Se l’applicazione è scritta in linguaggio C si deve verificare se questa operazione è gestita in modo trasparente dal compilatore.

IL MODULO PSD

Il modulo PSD è contenuto all’interno dello stesso chip ed è connesso al microcontrollore tramite il bus del micro. La periferica PSD descritta in figura 1 può contenere fino a 32KByte di ram una flash da 32KByte e una flash con dimensione fino a 256Kbyte, una PLD, denominata DPLD, per la decodifica dei chip select di selezione dei componenti interni al PSD e una seconda PLD, denominata GPLD (General PLD), di uso generale. Il PSD aggiunge nuove porte di I/O alle normali porte di I/O del microcontrollore portando il numero massimo di I/O utilizzabili a 38 per la versione a 80pin e 29 per la versione a 52pin. Dal conteggio è escluso il bus del micro disponibile all’esterno solo per la versione a 80pin. Tutti i registri di configurazione e di stato del modulo PSD sono accessibili nello spazio data XRAM del micro 8051 con l’istruzione movx. I singoli registri hanno un indirizzo relativo interno alla memoria del PSD e occupano un’area XDATA di 256byte. L’indirizzo assoluto dei registri del PSD è definito dal chip select csiop che abilita l’accesso al modulo PSD.

Le memorie flash

All’interno del modulo PSD sono contenute due memorie flash. Le dimensioni delle memorie dipendono dal modello utilizzato. La flash primaria ha le dimensioni maggiori e può variare da 64KB a128KB a 256KB ed è suddivisa in settori da 32KB indirizzabili separatamente con i segnali chip select fs0..fs7. La flash secondaria ha dimensioni di 16KB o 32Kb ed è suddivisa in settori di 8KB indirizzabili con i chip select CSBOOT0..CSBOOT3. La flash può essere scritta byte a byte mentre la cancellazione può avvenire solamente per settori. Per effettuare le operazioni di cancellazione o scrittura sulla flash si devono utilizzare le normali sequenze costituite da codici di controllo eventualmente seguiti dai dati da memorizzare. Per la verifica della programmazione o della cancellazione si possono applicare gli algoritmi del bit toggle o del data polling.

Le logiche PLD

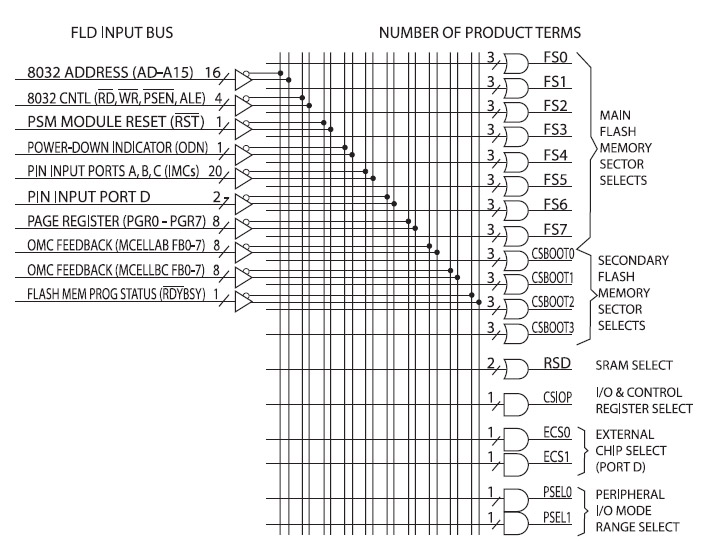

La DPLD gestisce tutti i chip select dei diversi componenti interni e esterni del PSD. La struttura della DPLD è riportata in figura 1.

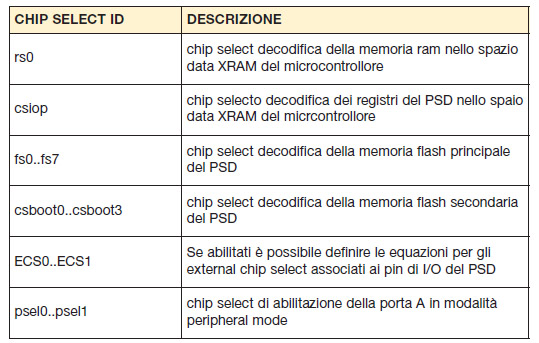

Mentre i chip select definiti dalla DPLD sono elencati nella tabella 1.

Tabella 1. Chip select definiti dalla DPLD del modulo PSD per la decodifica delle periferiche interne contenute nel modulo PSD e di eventuali periferiche esterne collegate al bus del microcontrollore.

La GPLD è formata da un array di 16 macrocelle di output e 20 macrocelle di input. L’uscita di ogni macrocella di output può essere collegata ad un pin delle porte del PLD oppure riportata come ingresso nella PLD per realizzare ad esempio contatori, registri a scorrimento oppure per setendere la logica di decodifica della DPLD. Ogni macrocella di output si può configurare come logica combinatoria oppure come logica sequenziale utilizzando il registro flipflop che può essere di tipo D, T, JK o SR. Le macrocelle di input possono gestire fino a 20 segnali e l’acquisizione può essere sincronizzata da un segnale di clock.

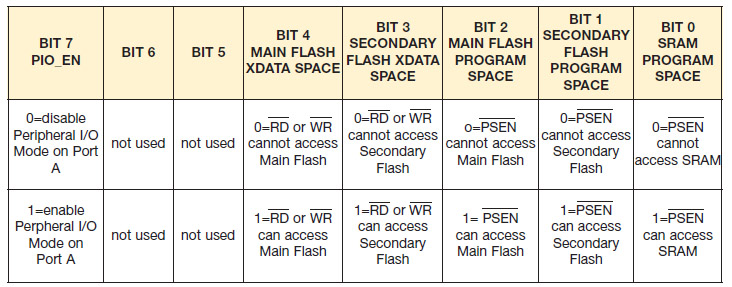

Il registro VM (Virtual Memory)

Tramite il registro VM, descritto in tabella 2, è possibile definire in quale spazio saranno visibili le memorie flash e ram.

Tabella 2. Il registro VM del uPSD. Con questo registro si può definire la visibilità delle memorie ram e flash negli spazi XRAM e CODE del microcontrollore 8051.

Se, ad esempio, si abilita la connessione tra il segnale psen e la memoria RAM sarà possibile eseguire codice dalla RAM stessa. Se si abilita la connessione dei segnali rd e wr del bus con una memoria flash sarà possibile accedere a quest’ultima in modalità dati e si potranno effettuare operazioni di lettura e scrittura con l’istruzione movx.

Il registro Page

Con il registro page è possibile abilitare la modalità di bank switching. Si può immaginare il registro page come un estensione del bus indirizzi a 16 bit del micro che consente di accedere anche a memorie di dimensioni superiori a 64KB, limite dell’indirizzamento a 16bit. Il registro sarà utilizzato come input della DPLD per la sintesi delle equazioni di decodifica dei chip select di abilitazione delle memorie.

LA PROGRAMMAZIONE DEL UPSD

Poiché all’interno del uPSD ci sono diversi componenti programmabili: le due memorie flash, la DPLD e la GPLD, per programmare un uPSD si devono realizzare tutti i files di configurazione dei diversi componenti. Il codice applicativo si può sviluppare con un qualsiasi tool di sviluppo per 8051 che può generare un file compilato in formato intel-hex o motorola-s. Per la configurazione dei registri del uPSD e la programmazione delle due PLD sono invece disponibili due programmi forniti dalla ST: il PSDsoft Express e il CAPS. La programmazione del componente avviene tramite la porta JTAG a quattro o sei fili. Per la programmazione è necessario disporre dell’adattatore FLASHLINK per la connessione al PC tramite porta parallela oppure dell’adattatore ULINK per la connessione della porta JTAG tramite USB. Questi adattatori e i tools di programmazione sono normalmente forniti con la scheda di valutazione del uPSD.

Programmare le PLD

I due programmi PSDsoft Express e CAPS utilizzabili per la programmazione delle PLD si equivalgono come funzionalità. Il PSDsoft Express è essenziale nella grafica ed era stato creato per la programmazione dei componenti PSD di Waferscale poi acquisita da ST. Il secondo programma è senza dubbio più semplice ed intuitivo e contiene alcune procedure automatiche di configurazione che semplificano la procedura di programmazione del PLD.

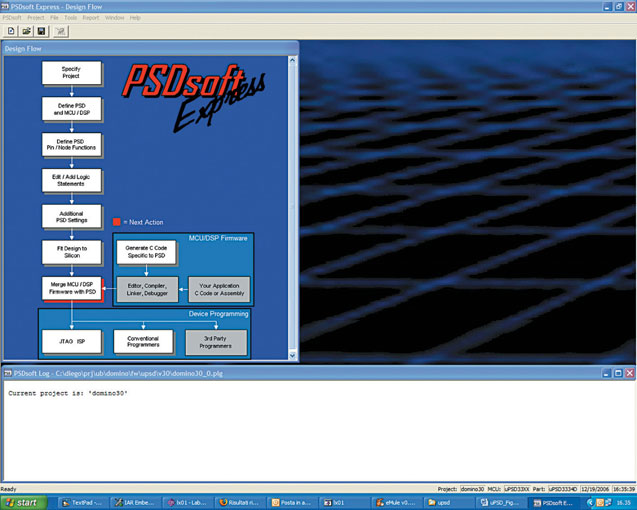

IL PROGRAMMA PSDSOFT EXPRESS

La finestra principale del PSDsoft Express è riportata in figura 5.

Il diagramma di flusso indica i singoli passi che si devono effettuare per la programmazione del uPSD. La prima operazione è ovviamente la scelta del componente da utilizzare. Per questa operazione si può richiedere l’aiuto del wizard che propone i modelli disponibili in base alle caratteristiche indicate. Nel passo successivo si devono configurare tutti pin del uPSD. Per ogni pin si può specificare un nome o meglio un’etichetta che ricorda la funzione svolta dal pin stesso. Ad esempio UART_TX oppure CS_EXT per un chip select esterno… Per ogni pin selezionato, sul lato destro della finestra compaiono le possibili opzioni di configurazione. Per i pin del micro è possibile scegliere tra GPIO (general pourpose I/O) oppure una funzione alternativa normalmente associata ad una periferica del micro, ad esempio la porta di comunicazione seriale o un timer o la periferica IIC. Ultimata la configurazione degli I/O si devono definire le equazioni per i chip select interni ed eventuali chip select esterni. La sintesi di queste equazioni verrà realizzata nella DPLD. Prima di procedere con la definizione dei chip select, se necessario, si deve definire la dimensione del registro di pagina da utilizzare per il bank switching. L’operazione è obbligatoria quando si utilizzano componenti con flash di grosse dimensioni, superiori a 64KByte. Per ogni chip select si deve definire il range di indirizzi in cui il chip select è attivo, si può specificare la pagina in cui il chip select è abilitato e si può condizionare questa abilitazione con una combinazione dei segnali di controllo elencati nella lista che compare a sinistra nella finestra di configurazione. Infine negli ultimi due passi del processo di configurazione è possibile definire le equazioni relative agli I/O assegnati alla GPLD durante la configurazione e le equazioni dei nodi (macrocelle non associate a pin di I/O) interni alla GPLD. Come risultato di questa configurazione viene prodotto il file di estensione .abl con il sorgente ABEL-HDL di tutte le equazioni descritte. Al passo successivo il programma PSDsoft Express permette di editare questo file per aggiungere nuove equazioni definite dal programmatore utilizzando la sintassi ABLE-HDL e mette a disposizione una libreria di funzioni predefinite per i moduli più comuni quali contatori, multiplexer… che possono essere facilmente aggiunte al codice sorgente. Le istruzioni aggiunte devono essere inserite entro i commenti begin user preserved …. e end user preserved… per evitare che il PSDsoft Express le cancelli quando aggiorna il file sorgente. Prima di procedere con la compilazione si devono fornire ancora alcune informazioni relative alla protezione del componente. È possibile abilitare la protezione in scrittura per ogni settore della flash del dispositivo e abilitare una protezione generale che impedisce la lettura del codice tramite porta JTAG. Questa protezione può essere rimossa solamente con la cancellazione delle memorie del uPSD tramite la porta JTAG. Il sorgente ABEL viene quindi compilato e il programma produce un report nel file con nome del progetto e estensione frp che riassume tutte le configurazioni dei pin e le equazioni descritte per le PLD. Dopo aver compilato il sorgente ABEL che descrive la programmazione delle PLD si deve unire al codice delle PLD il file di programmazione delle memorie flash. Nella finestra di selezione si deve specificare il nome del file per ogni chip select associato alle flash. Se l’applicativo può occupare un intera flash lo stesso nome del file dev’essere specificato per tutti i chip select relativi alla flash. A questo punto si può programmare il dispositivo tramite la porta JTAG Si può specificare il tipo di interfaccia (4fili o 6fili). L’interfaccia a 6fili include due segnali di controllo aggiuntivi ed è più veloce rispetto a quella a 4fili. Si possono indicare le operazioni da compiere: se programmare tutti i componenti del uPSD o solamente una flash o solo le PLD. È anche possibile leggere il contenuto del uPSD e salvare il contenuto in un file.

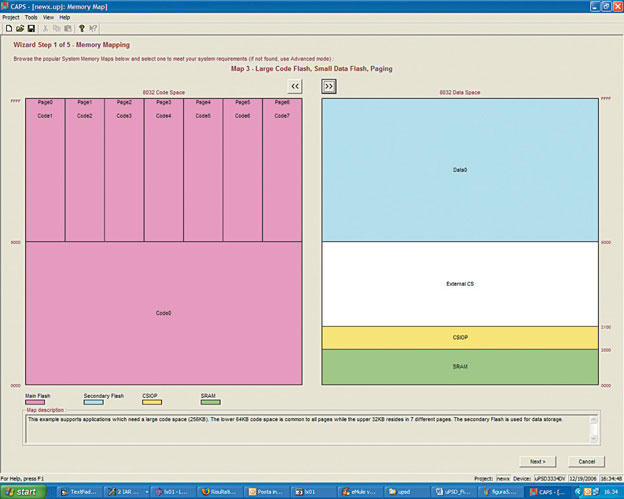

IL PROGRAMMA CAPS

Con il programma CAPS, scelto il componente da utilizzare, si può procedere con due modalità diverse: in wizard mode per la configurazione rapida e semplificata oppure in advanced mode per la configurazione dettagliata. La modalità wizard propone in veste grafica, la figura 4 è un esempio, delle possibili soluzioni per la mappa di memoria del uPSD.

Figura 4. La configurazione degli spazi CODE e XRAM del uPSD con il programma CAPS. In wizard mode il programma propone delle configurazioni predefinite e genera automaticamente le equazioni per i diversi chip select. In alternativa si pu ò utilizzare il programma in advanced mode per una configurazione personalizzata.

Scelta la mappa di memoria, le equazioni dei chip select sono definite in modo trasparente dal programma CAPS. Successivamente si possono specificare i file da associare alle flash del micro e quindi configurare i pin del uPSD. Come ultimo passo è possibile procedere alla programmazione tramite JTAG. La modalità advanced richiama la procedura di programmazione del PSDsoft Express. In questo caso però le finestre sono state aggiornate con una nuova veste grafica e rendono più semplice e intuitivo l’intero processo di configurazione.

ESEMPIO DI CONFIGURAZIONE DEL UPSD

L’esempio descrive una possibile configurazione della mappa di memoria del uPSD. La suddivisione è descritta nella tabella 3 Per la realizzazione e i test è stata utilizzata una scheda di valutazione DK3300 con un uPSD3334D-40U6.

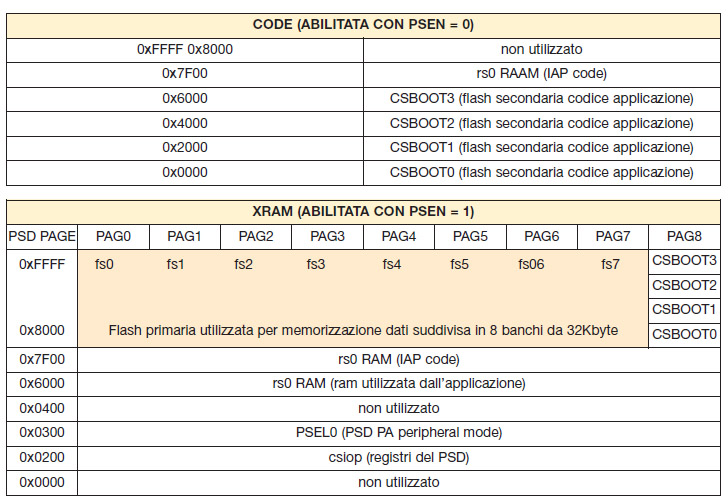

Tabella 3. Suddivisione degli spazi CODE e XRAM realizzata nell’esempio descritto nell’articolo. Si noti l’area a indirizzo 0x7F00 occupata in entrambi gli spazi dalla memoria ram e la pagina otto aggiunta allo spazio XRAM per consentire l’accesso alla flash secondaria durante la procedura di programmazione IAP. Per questa configurazione il registro VM = 0x9B

L’architettura 8051 prevede due spazi di memoria separati per il codice (spazio CODE) e per la memoria dati (spazio XRAM). È noto che l’accesso allo spazio CODE avviene in sola lettura con il segnale di controllo psen del bus., mentre l’accesso in lettura/scrittura allo spazio XRAM avviene con i segnali di controllo rd e wr. Nell’esempio descritto la flash primaria da 256KByte è destinata alla memorizzazione dati e pertanto sarà inserita nello spazio XDATA mentre il codice è memorizzato nella flash secondaria che dovrà essere inserita nello spazio CODE. Per realizzare la funzione IAP di aggiornamento del firmware però la flash dev’essere anche visibile nell’area XDATA per poter effettuare operazioni di scrittura. Durante la programmazione della flash, inoltre, non è possibile accedere alla memoria se non per controllare lo stato della procedura di programmazione. Pertanto durante l’aggiornamento della flash secondaria si dovrà eseguire codice dalla memoria RAM o, in altre parole, la RAM che normalmente occupa lo spazio XDATA dovrà essere visibile, tutta o in parte, anche nello spazio CODE. Nella definizione del progetto si deve specificare in quale spazio di memoria devono essere inizialmente inserite le due memorie flash se XDATA, CODE o entrambi. La scelta non è vincolante e può essere modificata durante l’esecuzione del codice cambiando il valore del registro VM del PSD.

Le equazioni dei chip select

Lo spazio XRAM è stato suddiviso in due parti, nei 32Kbyte inferiori sono stati inseriti la memoria RAM, i registri del PSD e le periferiche esterne. Come si può vedere dalla tabella 3 in quest’area, la flash secondaria e la ram condividono in parte lo stesso intervallo di indirizzi. Normalmente la flash occupa lo spazio CODE e la ram lo spazio XDATA e non ci sono conflitti perché i due spazi sono separati e non accessibili contemporaneamente. La funzione IAP però richiede che flash e ram occupino entrambi gli spazi, per questo si deve configurare il registro VM del PSD per consentire ai segnali rd/wr di raggiungere la flash secondaria (visibilità nell’area XRAM) e al segnale psen di raggiungere la ram (visibilità nell’area CODE). A questo punto poiché flash e ram condividono lo stesso intervallo di indirizzi, per evitare conflitti, si devono inserire anche i segnali di controllo nelle equazioni dei chip select dei due componenti per discriminare l’accesso al componente corretto. Per questo è sufficiente controllare lo stato del segnale psen che discrimina l’accesso all’area CODE (psen = 0) o XRAM (psen=1). Il csiop definisce la posizione assoluta dei registri del PSD all’interno dello spazio XDATA. Il range di indrizzi in questo caso dev’essere di 256 byte. Nell’esempio riportato in figura 5 i registri del PSD sono accessibili nell’area 200h..2FFh. Si tratta di una scelta arbitraria che dipende dal progettista. Anche la scelta di inserire la ram, che in questo caso ha dimensioni di 8Kbyte, negli indirizzi 6000H..7FFFH dello spazio XDATA è arbitraria e decisa dal progettista. L’accesso alla memoria ram è condizionato dal segnale psen come descritto in precedenza. Solamente gli ultimi 256 byte invece sono visibili in entrambi gli spazi CODE e XDATA, infatti nel secondo termine dell’equazione del chip select ram rs0 manca il controllo sul segnale psen. In questi 256 byte la memoria flash non è accessibile ma è possibile accedere solamente alla RAM in scrittura/lettura o per eseguire codice. In questa zona della ram viene copiato ed eseguito il codice di programmazione della flash durante la procedura di aggiornamento IAP. I 32Kbyte superiori della memoria RAM sono invece utilizzati per mappare i banchi della memoria flash primaria da 256Kbyte che si ricorda, è utilizzata come memoria dati. Sfruttando il registro di pagina del PSD è possibile selezionare uno degli otto banchi di memoria in cui è stata suddivisa la memoria flash primaria ed abilitare l’accesso nello spazio XDATA nel range indirizzi da 8000h a FFFFh. I chip select fs0…fs1 di selezione della flash primaria sono tutti attivi nel range di indirizzi 8000h…FFFFh ma l’abilitazione di ognuno di essi sarà condizionata da un preciso valore del registro di pagina come indicato nelle equazioni dei chip select fsx. La flash secondaria è posizionata nei primi 32Kbyte dello spazio CODE. Nella descrizione delle equazioni dei chip select CSBOOTx infatti compare il segnale !psen (il ! indica il segnale negato). La seconda parte dell’equazione dei chip select CSBOOTx abilita l’accesso alla flash secondaria nello spazio XRAM. Per avere l’accesso completo alla memoria in questo spazio si è scelto di mappare la flash secondaria nei 32KB superiori in una pagina aggiuntiva dell’area dedicata al bank switching. Il uPSD della scheda DK3300 ha il core alimentato a 3.3V e il PSD a 5V. Per interfacciare le periferiche a 5V, ad esempio un modulo display a caratteri, si devono necessariamente utilizzare le porte del PSD. In particolare per la connessione del display si può configurare la porta PA del PSD in modalità peripheral I/O. Per questo si deve definire anche il chip select psel0 che posiziona il buffer della porta PA ad un determinato indirizzo dello spazio XRAM. Ad esempio per la decodifica del CSBOOT3 è stato necessario utilizzare anche alcune macrocelle della GPLD. Compaiono anche altre semplici equazioni di logica combinatoria utilizzate per trasferire a 5V i segnali del bus dell’8051 per completare l’interfaccia del display.

PSDsoft Express è il software di progettazione per le famiglie PSD e UPSD di parti. Questo nuovo strumento di progettazione permette di integrare facilmente un PSD / uPSD mediante un semplice point-and-click environment. Qua il link della ST http://www.st.com/content/st_com/en/products/development-tools/software-development-tools/legacy-mcus-software-development-tools/legacy-mcus-ides/stsw-upsd001.html

Erano oggetti molto interessanti (li usavo fino a circa il 2008), ma oramai fuori produzione e da anni.

Ne ho ancora qualcuno nei cassetti e diversi funzionanti in applicazioni professionali a giro per il mondo.