Quartus II è un software per la progettazione di CPLD, FPGA e structured ASIC della famiglia Altera. Nell’articolo la descrizione dell’applicativo e alcuni consigli per conoscerlo meglio.

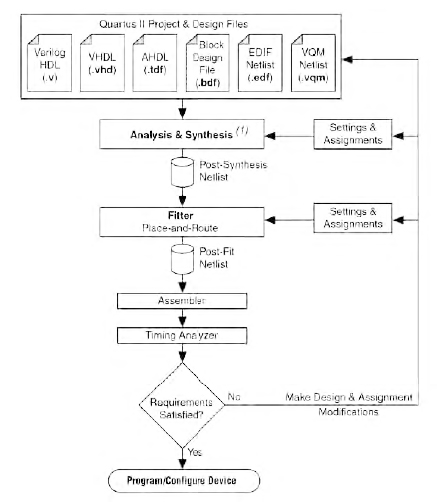

La versione 7.0 di Altera Quartus II ha integrato l’analizzatore TimeQuest, il primo tool di analisi delle temporizzazioni mai realizzato da un fornitore di FPGA a offrire un supporto nativo completo per il formato standard Synopsys Design Constraints. La versione integra anche una serie di prestazioni di progettazione team-based che permettono di gestire in modo efficiente le attività di sviluppo congiunto su progetti ad alta densità. Questi potenziamenti soddisfano le specifiche imposte dai moderni progetti ad alta densità da 90nm ed aprono la strada per indirizzare la richiesta - proveniente dai clienti di FPGA - di densità sempre più elevate che sta portando Altera verso le famiglie di nuova generazione da 65nm. Con quest’ultima versione del software Quartus II, Altera introduce una serie di innovazioni tecnologiche che permettono di soddisfare le esigenze dei clienti che lavorano sulle soluzioni a 90 nm, impostando un nuovo cammino verso il nuovo traguardo dei 65nm. Il software Quartus II di Altera fornisce una ambiente completo e cross-platform per la progettazione di logiche programmabili, che facilmente si adatta alle diverse necessità del progettista. Esso include soluzioni efficienti per tutte le fasi di progetto di FPGA e CPLD. Gli step seguenti descrivono il flusso del progetto base che generalmente si usa con Quartus II:

- Creazione di un nuovo progetto, eventualmente utilizzando il Wizard messo a disposizione del software.

- Utilizzo dell’editor di testi per creare la descrizione in linguaggio VHDL o Verilog. In aggiunta, è anche possibile utilizzare il linguaggio AHDL (Altera Hardware Description Language) appositamente studiato dalla casa produttrice ed ottimizzato per i suoi prodotti.

- Inserimento di vincoli di progetto tramite i tool Assignment Editor, Pin Planner, le finestre Settings, Floorplan Editor o Design Partitions.

- Sintesi del dispositivo mediante Analysis&Synthesis.

- Se il progetto contiene partizioni (nel seguito si spiegherà di cosa si tratta) e non si sta eseguendo una compilazione completa, bisogna effettuare il merge delle partizioni.

- Generare una netlist per effettuare una simulazione del progetto.

- Effettuare il Place&Route (denominato fitting in Quartus II) del progetto tramite il tool Fitter.

- Eseguire una analisi delle alimentazioni tramite l’analizzatore PowerPlay Power.

- Eseguire una simulazione temporale per verificare che rispetti i requisiti di progetto. Per questo si può usare l’analizzatore Classic Timing oppure TimeQuest Timing

- Creazione dei file di programmazione con il tool Assembler e trasferimento del codice mediante Programmer e l’hardware relativo fornito da Altera.

- Eseguire il debug del codice attraverso SignalTap II Logic Analyzer.

Il software supporta i principali dispositivi della famiglia Altera:

- Cyclone II e III

- MAX II

- Stratix II

- APEX II e 20KE

- ACEX

- Excalibur

- FLEX 10K, 10KE e 6000

- MAX 7000S, 7000B, 7000AE e 3000A

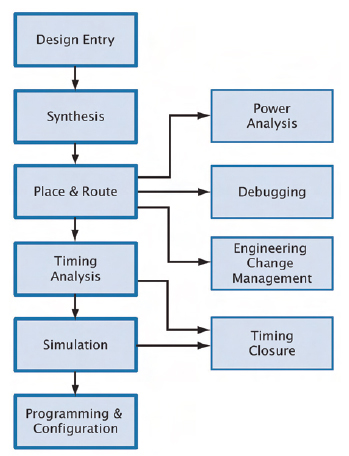

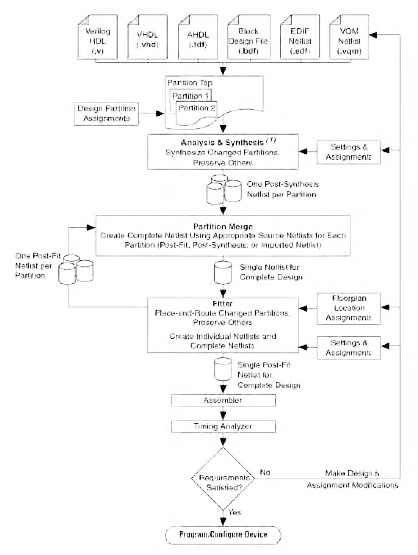

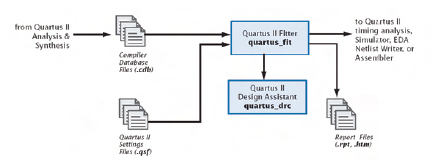

Per la sintesi del codice VHDL o Verilog è possible utilizzare software di terze parti come Mentor Graphics, Synopsys o Synplicity; in alternativa, è disponibile anche il software integrato in Quartus II (figura 1).

Figura 1. Quando il proprio progetto è basato su logiche programmabili è necessario seguire fasi di progetto ben precise. Il software Quartus II, messo a disposizione da Altera, offre soluzioni efficienti e semplici che assistono il progettista in ciascuna di tali fasi

COMPILAZIONE INCREMENTALE

Normalmente, quando si apportano delle modifiche ad un progetto è necessario ricompilare l’intero codice. Questo tipo di compilazione è chiamata standard o non partizionata. Lo schema logico delle varie fasi di progettazione sono riportate in Figura 2.

Figura 2. La compilazione non partizionata presenta lo svantaggio di dover, ad ogni modifica del progetto, ricompilare tutto il codice con conseguente perdita di tempo e di effecienza

Quartus II permette, invece, di effettuare anche una compilazione incrementale. Una ulteriore caratteristica di Quartus II è il LogicLock grazie al quale è possibile affrontare la progettazione incrementale, fondamentale quando si affrontano dispositivi di elevato taglio, quando si lavora in team o quando si integrano IP. Grazie a questa tecnica le prestazioni sono garantite al susseguirsi delle iterazioni in ogni regione su cui il software ha già compiuto un’ottimizzazione. Con la progettazione incrementale l’interazione tra tool di sintesi e tool di implementazione è divenuta sempre più fondamentale e coordinata. In questo modo si conservano i risultati delle precedente compilazioni e si effettua la ricompilazione solo sulla parte di codice che è cambiata. Si velocizzano notevolmente le fasi di modifica, compilazione e debug del codice. Per sfruttare i vantaggi della compilazione incrementale, bisogna organizzare il proprio progetto in partizioni logiche e regioni fisiche per la sintesi ed il fitting: una sorta di macro-aree di codice. Solo l’area modificata sarà interessata dalla ricompilazione. Le fasi di sviluppo si possono riassumere con lo schema logico riportato in Figura 3.

Figura 3. La compilazione incrementale (o partizionata) presenta l’indubbio vantaggio di semplificare l’intero processo di progettazione del codice, poiché solo le parti interessate dalle modifiche saranno ricompilate

L’AMBIENTE DI SVILUPPO

Si esamineranno ora i passi fondamentali richiesti per la creazione e gestione di un nuovo progetto. Essi si possono riassumere in:

- Creazione del progetto mediante il wizard.

- Inserimento delle specifiche sulla temporizzazione.

- Compilazione e download del codice nel dispositivo Altera.

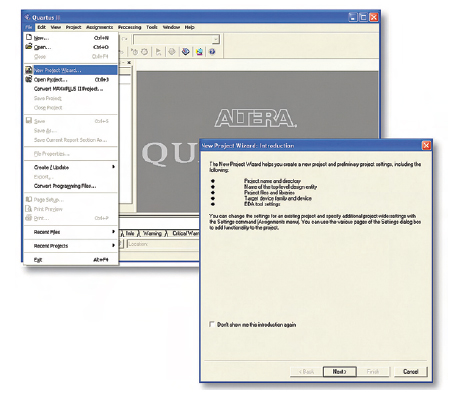

Per la creazione del progetto selezionare il menu File e quindi scegliere New Project Wizard, come mostra la Figura 4.

Figura 4. Per la creazione di un nuovo progetto con Quartus II è possibile usare il Wizard di configurazione. Esso semplifica notevolmente il processo di generazione del progetto

Saranno richieste le seguenti informazioni:

a) La directory di progetto, nome e top-level entity.

b) I file del pr

c) La famiglia dei dispositivi Altera con cui si intende lavorar

d) Il modello del dispositivo. È anche possibile, in alternativa, inserire le specifiche sul dispositivo ed avvalersi della selezione automatica.

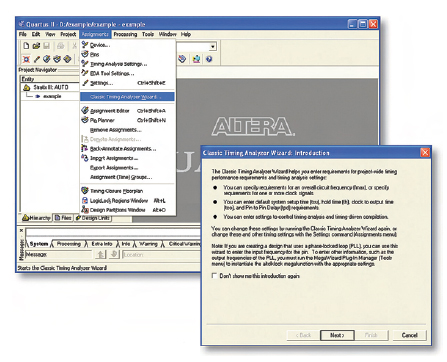

Dal menu Assignments il software permette di impostare le specifiche sulle temporizzazione del circuito (vedere Figura 5).

Figura 5. Per la selezione del specifiche di temporizzazione è possibile utlizzare il Timing Wizard del menu Assignments

Saranno richiesti i seguenti parametri di configurazione:

a) La frequenza massima di funzionamento (indicata con fmax) oppure le specifiche per uno o più segnali

b) Il tempo di setup (tSU), hold time (tH), clock-to-out (tCO) e pin-to-pin (tPD).

c) I ritardi stimati dei segnali esterni da e verso i pin del dispositivo.

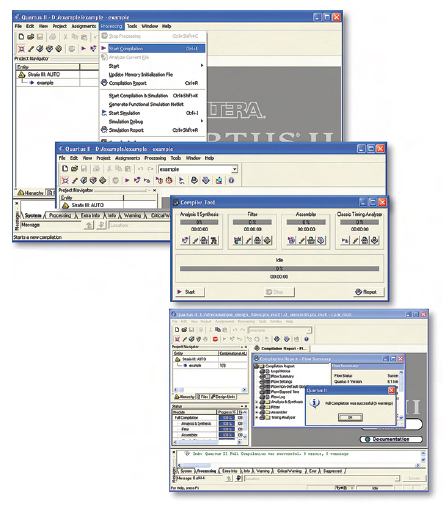

La fase successiva consiste nella compilazione del progetto. Per fare questo è possibile procedere in tre modi distinti:

a) Dal menu Processing selezionare Start Compilation.

b) Utilizzare l’apposito tasto della toolbar ( Figura 6).

c) Dal menu Compiler Tool selezionare Start

Figura 6. Per eseguire la compilazione del progetto è possibile usare tre differenti modi: menu Processing, il relativo tasto della toolbar oppure il menu Compiler Tool

Quando il processo di compilazione termina, fare riferimento alla finestra Compilation Report per avere informazioni circa le impostazioni del compilatore, le risorse utilizzate ed altro. Per avere informazioni su di una determinata funzione, è sufficiente premere F1 mentre si seleziona il menu interessato.

Strategie di routing

È il processo che traduce le specifiche ed il codice HDL nei blocchi logici programmabili che ne soddisfano le richieste (Figura 7); nell’ambiente di sviluppo Quartus II, questa fase è indicata con il termine fitting. Il software in questa fase assegna a ciascuna funzione logica il blocco digitale più appropriato, affinché siano ottimizzati i tempi ed i ritardi tramite la scelta del percorsi di routing migliori. Gli sforzi maggiori dei tecnici si sono indirizzati al miglioramento dell’algoritmo di Place&Route. Per questo scopo si è rivelata fondamentale l’acquisizione della startup Right Track CAD, nata dall’ambiente di ricerca dell’Università di Toronto e molto all’avanguardia negli studi sugli algoritmi di piazzamento. Grazie a quest’operazione il VPR (Versatile Place&Route), risultato di diversi anni di ricerca e messa a punto, è divenuto il punto cardine di Quartus II. Questo software consente di introdurre maggiori gradi di controllo nella procedura di Place&Route che a tutti gli effetti diviene di tipo timing driven e, gestendo in maniera prioritaria i percorsi critici, consente una riduzione del tempo totale di compilazione.

Figura 7. Il processo di Place&Routing trasforma le specifiche iniziali nella implementazione hardware della FPGA

Correggere il routing: il tool Chip Planner

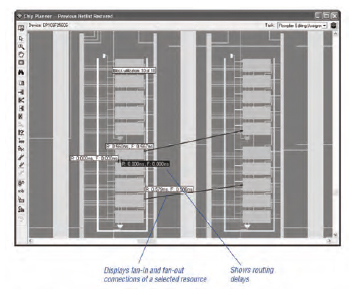

Uno strumento particolarmente utile per individuare possibili percorsi critici nel routing e ottimizzare al massimo i ritardi è Chip Planner. Questo strumento è in grado di rilevare tutte le risorse del dispositivo come interconnessioni e linee di routing, LAB (Logic Array Block), blocchi di RAM, pin di I/O e interfacce (vedere Figura 8).

Figura 8. Chip Planner è un utile strumento per individuare percorsi critici dovuti ad errori nella fase di placamento e routing

Tramite lo zoom in, Chip Planner offre un dettaglio maggiore della finestra visualizzata. Sulla base delle informazioni ottenute si possono modificare di conseguenza le interconnessioni dei blocchi digitali.

Ottimizzare i consumi: il tool PowerPlay

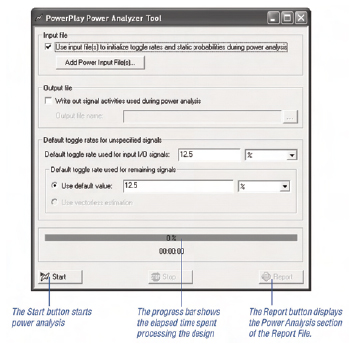

Quando si lavora con logiche programmabili quali FPGA, un apsetto da non sottovalutare è il consumo di potenza. Quartus II dispone di un comodo strumento che consente di stimare i consumi di potenza sia statici che dinamici: PowerPlay. Esso fornisce un report che evidenzia, per tipo di blocco ed entità, i consumi.

Figura 9. Il tool PowerPlay consenti di stimare i consumi di potenza statica e dinamica

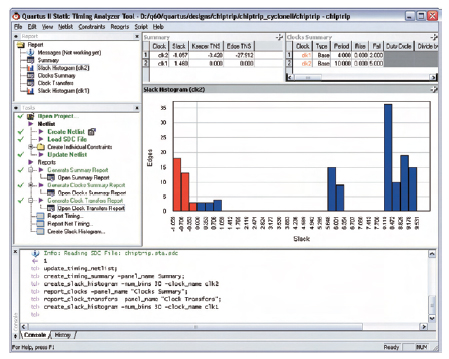

Analisi delle temporizzazioni: il tool TimeQuest

Altera ha sviluppato TimeQuest, un nuovo analizzatore di timing direttamente integrato nel software Quartus II versione 7.0. TimeQuest rappresenta il primo tool di analisi delle temporizzazioni “ASIC-strength” proposto da un fornitore di FPGA: esso complementa il tool di analisi dei consumi PowerPlay, introdotto con le versioni precedenti per supportare – secondo lo stile utilizzato negli ASIC - l’analisi e la previsione dei consumi. TimeQuest è particolarmente utile nell’analisi dei progetti basati su temporizzazioni complesse, tipiche nei circuiti con clock multiplexati o con I/O “source synchronous” veloci. TimeQuest supporta il formato standard SDC (Synopsys Design Constraints) relativo ai vincoli temporali, largamente diffuso tra i progettisti ASIC: esso offre un semplice ed efficiente mezzo per controllare i progetti e per accelerare la convergenza temporale (Figura 10).

Figura 10. Il tool TimeQuest consente di analizzare le temporizzazione dei segnali

Tutorial interattivo

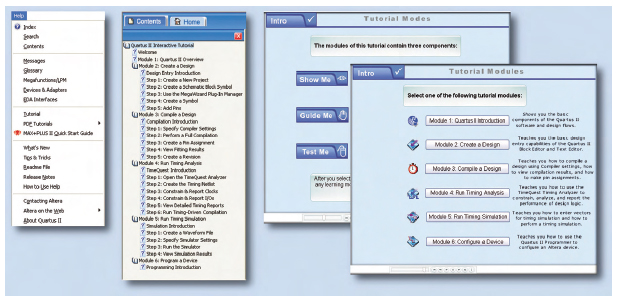

A partire dalla versione 6.1 del software Quartus II è stato incluso un nuovo tutorial interattivo. Tale strumento risulta particolarmente utile e fornisce a chi si avvicina per la prima vlota a questo ambiente di sviluppo le linee guida sul progetto, compilazione, analisi temporale e programmazione del target. Il tutorial comprende animazioni audio e Flash per spiegare step-by-step come realizzare le diverse funzioni. È possibile scegliere tra le modalità di visualizzazione Show Me, Guide Me o Test Me, come mostrato in Figura 11.

Figura 11. Quartus II dispone di un utile tutorial interattivo che guida l’utente nella descrizione (attraverso animazioni multimendiali) del vari passi da seguire per sviluppare un progetto

INSTALLAZIONE DEL SOFTWARE

Per installare il software far riferimento ai passi di seguito riportati:

- Creare una directory sull’hard disk per l’installazione. La posizione di default è c:\quartus2we

- Avviare l’eseguibile quartusii_< version information >_web_edition_single.exe (dove < version information > indica il numero di versione del software).

- L’installer guiderà attraverso i vari passi di installazione.