Nell’ultimo decennio, i progettisti di stazioni base wireless hanno fatto molti sforzi per ridurre costi, consumi e ingombri. Per questi progettisti, l’obiettivo preso in considerazione per lo sviluppo delle stazioni base 3G è stato semplice: raggiungere una banda dieci volte superiore a fronte di un costo dieci volte inferiore. L'approccio servirà come base futura per lo sviluppo di tecnologie mobile di prossima generazione, un esempio è rappresentato dal 5G.

Introduzione

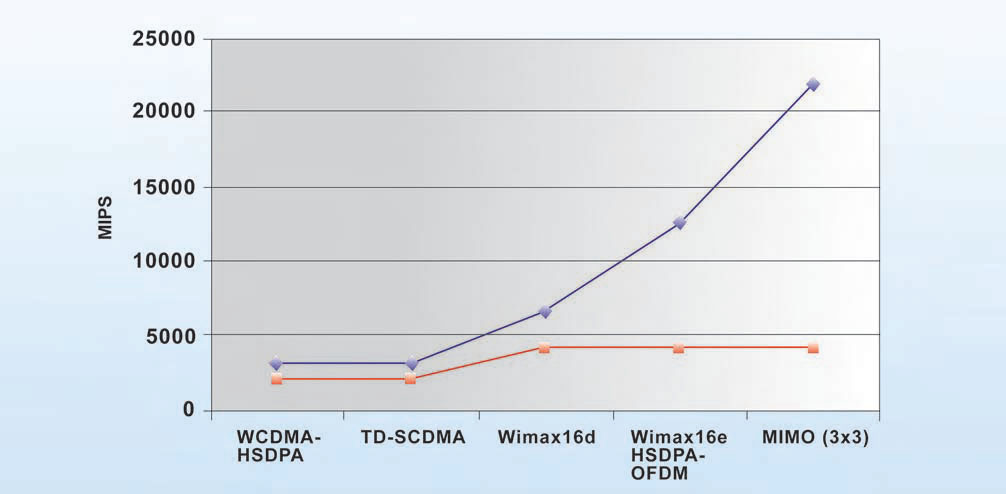

La specifiche di potenza di calcolo necessarie per gestire gli algoritmi in banda base continuano a crescere a causa dei nuovi protocolli wireless. Come riportato in figura 1, i DSP (Digital Signal Processor) convenzionali non dispongono di una quantità sufficiente di MIPS per eseguire tutte le funzioni di elaborazione della banda base.

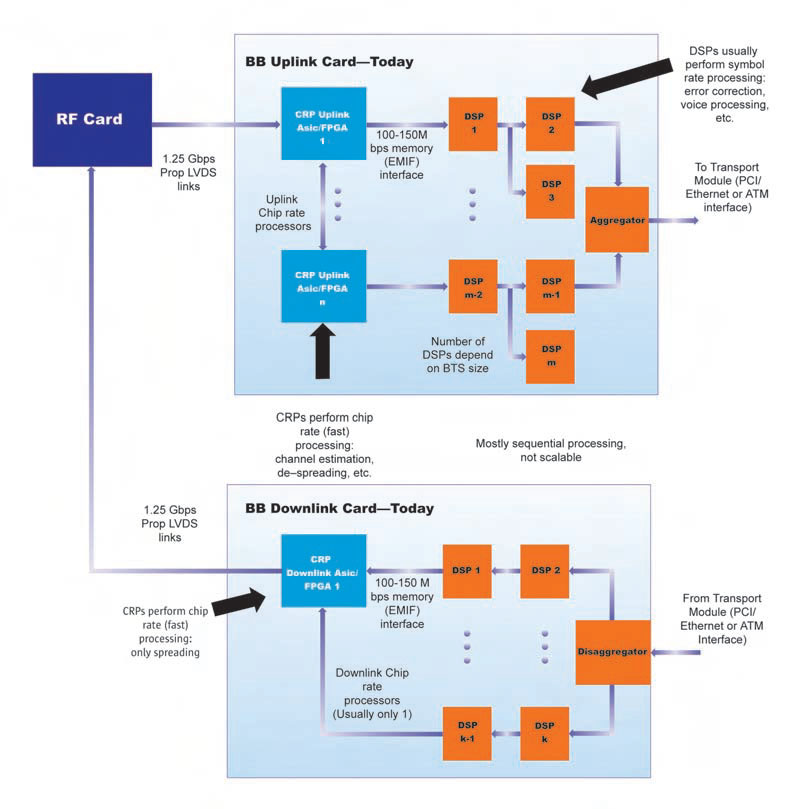

Questo comporta l’esigenza di ricorrere a degli acceleratori hardware capaci di sopperire alle carenze dei DSP. Un’architettura tipica prevede un cluster di DSP e di blocchi di accelerazione hardware integrati nella scheda bandabase dove vengono elaborati più canali. Le stazioni base fanno normalmente affidamento su uno schema di elaborazione sequenziale dove i vari blocchi e le varie funzioni di elaborazione sono allineati nel tempo. Tali architetture sono spesso riconducibili a quanto riportato in figura 2.

Qui, un processore “chip-rate” (CRP) si interfaccia a un backplane time-sliced e riceve dalla scheda RF dei “campioni”. Nei sistemi legati alle tecnologie CDMA (quali WCDMA o CDMA2000) i campioni sono convertiti in simboli prima di passare al DSP, spesso attraverso l’interfaccia di memoria parallela. A questo punto il DSP esegue le sue operazioni sui simboli, per esempio la correzione degli errori o l’elaborazione del canale voce/dati. Nei sistemi OFDM (Orthogonal Frequency Division Multiplexing) legati - per esempio - agli standard 802.16x o WiMAX, il CRP è sostituito da un PHY OFDM che esegue la sincronizzazione e l’FFT prima di inviare i simboli ai DSP. In tal caso i DSP eseguono operazioni simili a quelle svolte nelle architetture CDMA. Questo tipo di soluzione non è molto scalabile in quanto le allocazioni su ASIC e DSP sono predeterminate e sono strettamente collegate al tipo di hardware adottato. Come risultato, alcuni DSP e CRP possono risultare sottoutilizzati, anche se questa inefficienza è tollerata a causa della difficoltà di trasferire le risorse da un blocco di elaborazione all’altro durante la fase operativa. Ulteriori elementi di difficoltà derivano dall’impossibilità di avere architetture simili per stazioni base di taglio pico, micro e macro: ciò deriva dalle problematiche relative all’adattamento degli algoritmi sviluppati per i CRP e per i DSP per una determinata applicazione. In tal caso, per soddisfare un piccolo incremento di prestazioni, potrebbe essere necessario aggiungere un intero nuovo gruppo di CRP e DSP. In alcune architetture, uno dei CRP interfaccia il backplane (scheda RF) mentre il resto dei CRP dialoga con il primo CRP (scheda uplink). Ciò richiede un progetto differente per il CRP destinato all’interfacciamento del backplane in quanto non è possibile replicare lo stesso tipo di sviluppo anche per i CRP subordinati senza ridurre la loro efficienza e pertanto senza influenzare il ritorno di investimento. Un problema per il software di sistema può essere rappresentato dall’interfaccia di memoria tra CRP e DSP. La natura bidirezionale di una interfaccia di memoria standard può rendere difficile sfruttare a fondo questo tipo di interconnessione. Normalmente infatti gli algoritmi in banda base sono sensibili ai ritardi non deterministici che possono essere introdotti utilizzando un’interfaccia bidirezionale.

Standard

Negli anni più recenti l’industria ha supportato numerosi sforzi di standardizzazione volti a promuovere la modularità a livello di sistema e di rete, a favorire la riutilizzabilità dei risultati di ingegnerizzazione e ad aumentare la scalabilità delle architetture. Uno degli esempi più significativi di questo trend è stato la Open Base Station Architecture Initiative (OBSAI). OBSAI definisce un’architettura modulare per stazione base basata su interfacce standardizzate tra ciascun modulo. Sei mesi dopo il lancio di OBSAI, è stato lanciato uno standard concorrente – il Common Public Radio Interface (CPRI). Molto più semplice dell’OBSAI, lo standard CPRI è focalizzato sulle stazioni base UMTS. Esso prevede la suddivisione del sistema in un blocco RF e in un blocco di controllo: i due sono connessi attraverso un’interfaccia digitale standard. Per indirizzare le esigenze a livello di chassis dei produttori di apparati di rete e dei service provider, il PCI Industrial Computer Manufacturers Group (PCI-MG) ha definito un formato di standard di chassis denominato Advanced Telecom Computing Architecture (ATCA). Per il trasferimento dei dati e la gestione del protocollo, i DSP utilizzati nelle applicazioni relative alle stazioni base wireless hanno bisogno di interconnessini semplificate ma ad alta velocità. Queste applicazioni embedded – estremamente pesanti dal punto di vista dei calcoli – richiedono al sistema di spostare rapidamente i dati tra i vari processori di segnali presenti all’interno di una farm di DSP strettamente integrati tra loro. Le specifiche serial RapidIO sviluppate come standard aperto, sono state espressamente pensate per soddisfare le necessità dei sistemi embedded ad alte prestazioni. Lo standard seriale RapidIO combina i vantaggi di modularità a livello di chassis e di sistema tipici di standard quali OBSAI, CPRI e ATCA, estendendoli anche a livello di scheda. Sia OBSAI che CPRI non definiscono l’interfaccia verso la scheda di linea di una stazione base. Oltre a questo, il supporto ottimizzato offerto da serial RapidIO ai cluster DSP consente ai progettisti di sviluppare in modo economicamente conveniente architetture di apparato flessibili e scalabili che semplicemente non possono essere replicate in progetti basati su FPGA o ASIC. Utilizzando serial RapidIO un progettista di stazioni base può, per esempio, costruire un sistema DSPintensive per applicazioni di macrocella che può essere rapidamente diffuso per supportare la copertura di grandi aree. Gran parte del progetto originario può essere successivamente riutilizzato in soluzioni su scala ridotta per ambienti cellulari micro o pico, garantendo il raggiungimento dei livelli di densità e saturazione desiderati nel modo più economico possibile. Cosa più importante, serial RapidIO semplifica le comunicazioni inter-processore grazie all’integrazione del traffico di controllo e del traffico dati: tale approccio permette di scaricare il processore dalle task più semplici e più onerose sotto il profilo del tempo e di differenziare il traffico dati a bassa e alta priorità.

Mettere tutto insieme

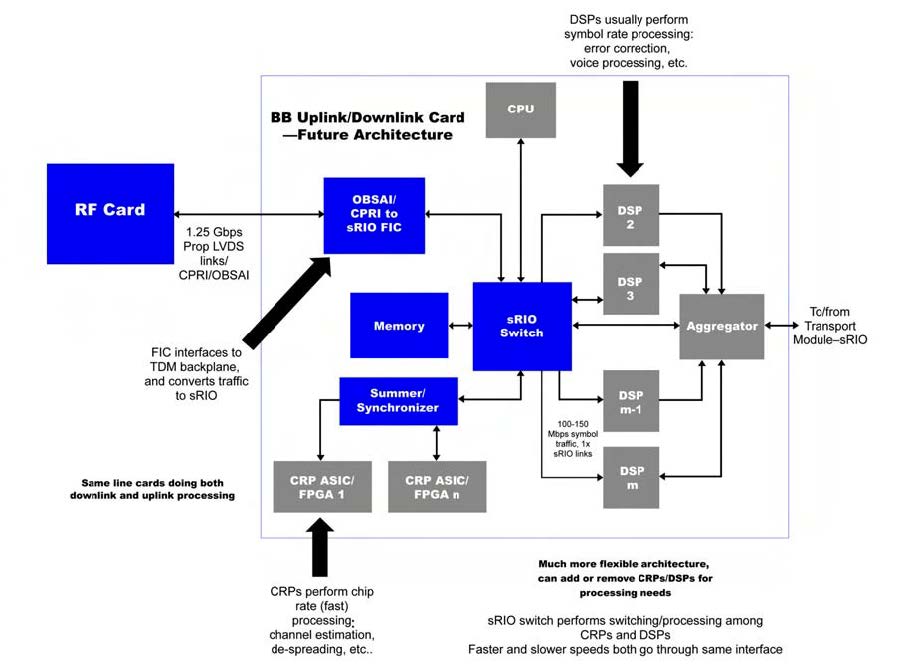

La domanda ora è: come mettere tutto questo insieme per sviluppare una stazione base? Cosa manca ancora per realizzare una scheda banda base completa? Esaminiamo il partizionamento degli algoritmi di protocollo per le stazioni base. I blocchi in azzurro sono le operazioni matematiche necessarie per i transceiver bandabase di tipo CDMA (UMTS, CDMA2000, ecc.). Una scheda bandabase ideale ha un cluster di DSP e di blocchi di accelerazione hardware (o CRP) realizzati sotto forma di FPGA o ASIC. La figura 3 illustra il partizionamento degli algoritmi sui DSP e sui CRP. Questo può richiedere più DSP e CRP in funzione delle specifiche di elaborazione della scheda bandabase: in ogni caso, questi blocchi devono essere connessi tra loro. Una ripartizione simile può essere fatta per gli algoritmi basati su OFDM. In figura 3 sono indicate con delle linee rosse anche le interfacce seriali RIO e CPRI/OBSAI. Le interfacce seriali RIO sono utilizzate per connettere più blocchi di elaborazione sulla scheda bandabase, come illustrato in figura 4. Queste interfacce sono riportate anche in figura 3 con il partizionamento degli algoritmi.

È da notare che i blocchi verdi in prossimità delle interfacce sono necessari per la formattazione dei dati tra l’interfaccia e gli algoritmi, quali l’estensione del segno, la pacchettizzazione dei campioni o dei simboli e l’allineamento multiple-packet (per CRP multipli) prima della somma. Queste funzioni devono essere eseguite da uno dei dispositivi prossimi a questa interfaccia. La domanda è: qual’è l’architettura più adatta a gestire questo partizionamento? La figura 4 illustra un’architettura pressoché ideale per le schede bandabase di nuova generazione.

Un FIC (Fabric Interface Component) traduce i segnali CPRI/OBSAI in serial RapidIO, mentre il resto dell’interfaccia della scheda bandabase è seriale RapidIO: in tale situazione, un normale switch di serial RapidIO non sarebbe sufficiente per gestire le operazioni necessarie. Nella scheda bandabase sono presenti due flussi di traffico distinti:

- Tra FIC e CRP: traffico ad alta velocità (campioni sparsi) con timing deterministico. La latenza su questo link deve essere deterministica per supportare le specifiche di timing della stazione base. I pacchetti vengono inviati a più CRP o in uplink, sommati al downlink.

- Tra CRP e DSP: molto più flessibile in termini di latenza, si tratta di traffico con banda inferiore (simboli) e pacchetti di manutenzione e controllo

Un normale switch di serial RapidIO deve essere supportato da un dispositivo sommatore e sincronizzatore il quale allinea i pacchetti dai vari CRP, li somma all’uplink e li invia in multicast ai CRP dell’uplink. Differenti dispositivi e algoritmi lavorano su differenti campioni e dimensioni simboliche. Per esempio, CPRI definisce dimensioni di campione da 8 bit a 40 bit. I processori preferiscono lavorare su dimensioni di campione da 8, 16 o 32. Anche i vari algoritmi vogliono campioni in ordine specifico (IQ insieme o separati, sovracampionamento insie- me a campioni regolari o separati eccetera) pertanto queste operazioni di formattazione dati devono essere eseguite nel CRP e nel DSP. In funzione del tipo di DSP e CRP, esistono numerose combinazioni di operazioni che il progettista deve prendere in considerazione e il processore deve spendere molti MIPS per eseguirle. Le dimensioni delle schede bandabase possono essere piccole o grandi, in funzione del sistema. Il fattore di forma Micro-TCA può essere considerato adatto a tutte le varie schede di una stazione base. Questo permette al progettista di dare vita a una vasta selezione di moduli intercambiabili che consentono di soddisfare le esigenze dei vari costruttori di apparati per telecomunicazioni. Questa architettura supporta anche progetti di stazioni base flessibili e scalabili:

- flessibili: cambiando i CRP con PHY OFDM lo stesso progetto può essere utilizzato per sistemi basati sia su CDMA sia su OFDM

- Scalabili: il numero di CRP e DSP può essere facilmente cambiato, adattando lo stesso progetto per stazioni base da pico a macro. Anche il traffico e la capacità di elaborazione possono essere spostati da un dispositivo all’altro durante il normale funzionamento in quanto l’architettura non è più strettamente accoppiata agli algoritmi.

Conclusioni

Gli utenti si aspettano servizi di qualità sempre più elevata a fronte di costi nettamente inferiori. Di conseguenza, le specifiche di banda e di prestazioni legate alla fornitura di servizi di prossima generazione implicheranno la disponibilità di stazioni base realizzate con progetti sempre più sofisticati e complessi. L’elemento chiave per soddisfare queste esigenze e la contemporanea richiesta di riduzione dei costi sta nell’adozione di architetture modulari e basate su soluzioni standard. Con il ricorso a standard quali ATCA, OBSAI e CPRI e con l’adozione di progetti ad elevato grado di flessibilità e di adattabilità per gli array DSP dotati di interfaccia serial RapidIO, gli sviluppatori di stazioni base possono garantire i servizi ad alte prestazioni a fronte di una struttura di costo gradita agli utilizzatori. Nella presente trattazione sono stati descritti i componenti chiave di una architettura ideale di un sistema bandabase evidenziando l’importanza del ruolo giocato da vari standard - tra i quali Common Public Radio Interface (CPRI), Open Base Station Architecture Initiative (OBSAI), Advanced Telecom Computing Architecture (ATCA) e Serial RapidIO.

La ricerca e sviluppo 5G mira soprattutto al supporto di comunicazione con costi contenuti nella gestione delle relatiive strutture. Il tutto in una visione di massima efficienza per far fronte all’IoT e simili.