In questo articolo della rubrica Firmware Reload affrontiamo una introduzione ai dispositivi mixed-processor OMAP-L132 di TI.

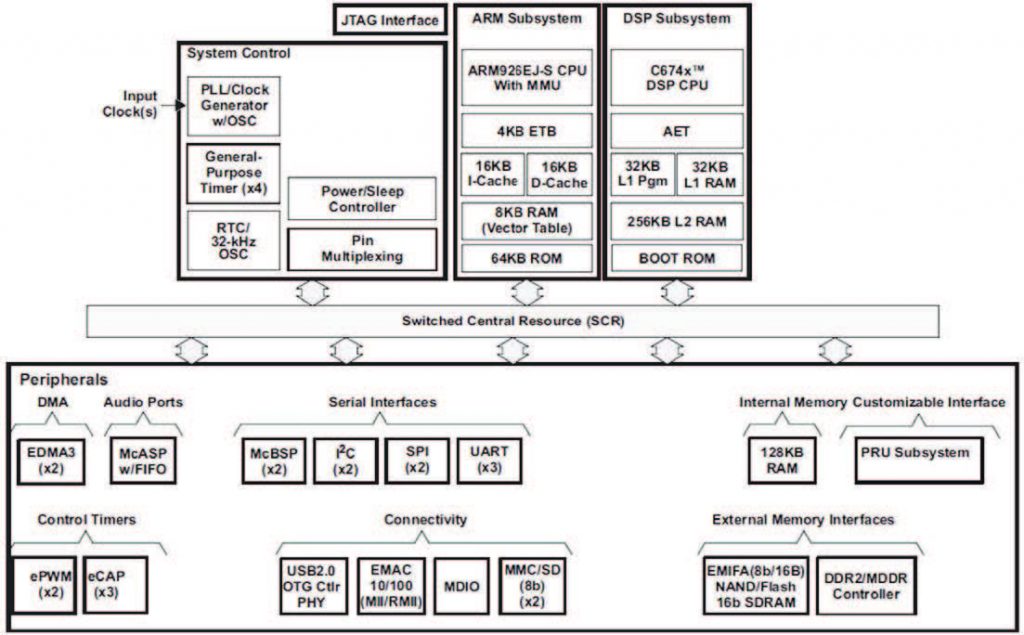

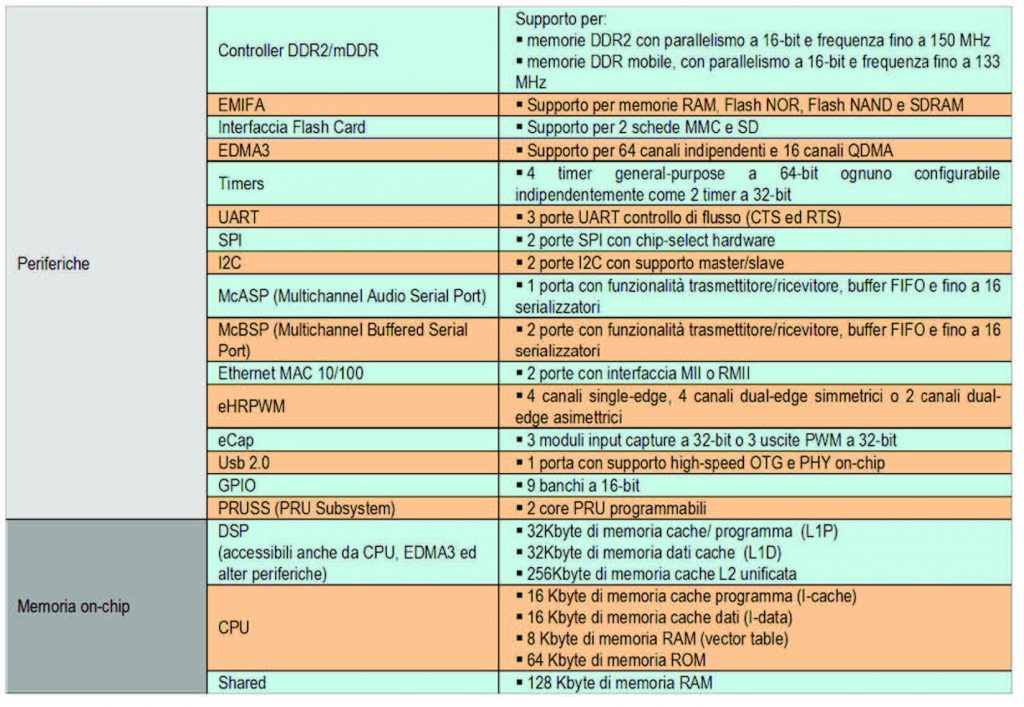

Se nel mondo delle logiche programmabili è sempre più forte la necessità di soluzioni mixed-signals, in quello dei microprocessori è forte la spinta verso sistemi mixed-processor che integrino un core CPU e un motore DSP per offrire prestazioni di punta, supporto per un sistema operativo robusto e un insieme esteso di periferiche di espansione e comunicazione. Uno dei dispositivi più interessanti in questo segmento di mercato è certamente l'OMAP-L132 C6-Integra di Texas Instruments che integra una CPU ARM926EJ-S ed un DSP TMS320C674x. La Figura 1 mostra uno schema a blocchi dell’architettura del componente mentre la tabella in Figura 3 ne riassume le principali risorse e periferiche disponibili.

Figura 1. Architettura dei mixed-processor OMAP-L132 di TI

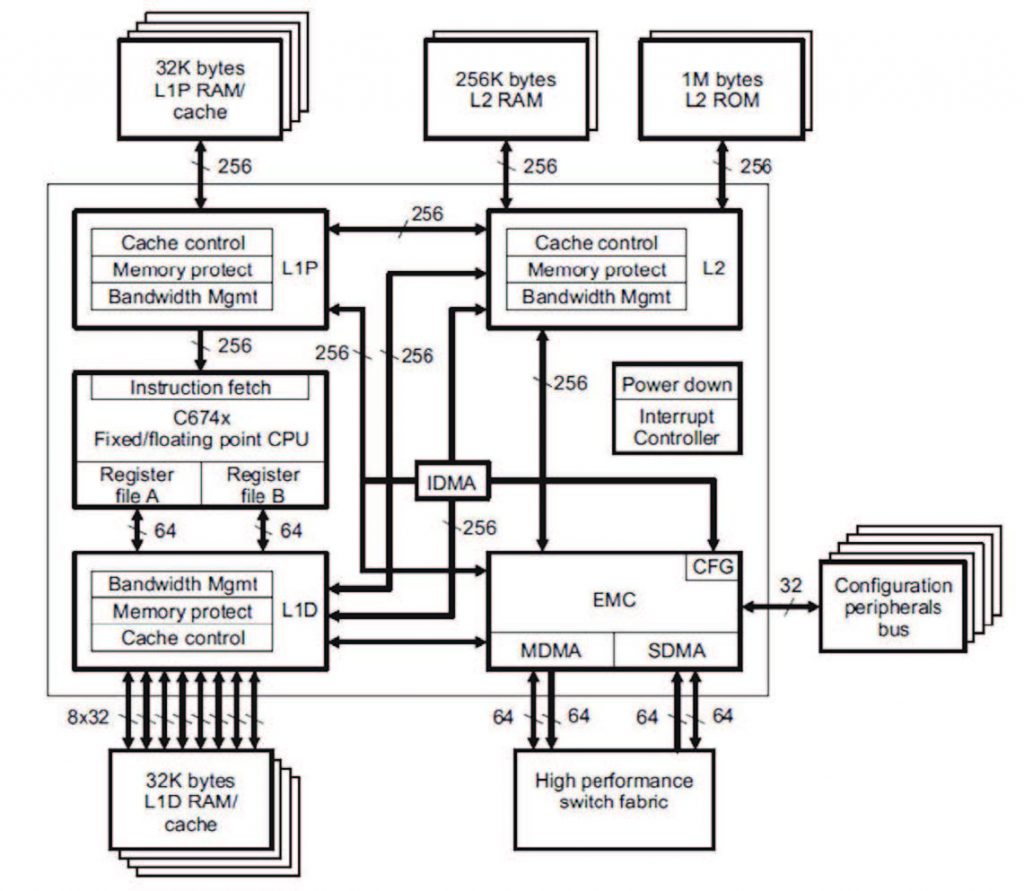

Figura 2. Architettura del core DSP degli OMAP-L132 di TI

Figura 3. Risorse di memoria e periferiche disponibili a bordo dell'OMAP-L132 di TI

UNA CPU…

La CPU ARM926EJ-S è un core RISC a 32 bit con architettura Harvard e supporto per l’insieme di istruzioni ARMv5TEJ (che permette di operare nelle modalità 32 bit ARM e 16 bit Thumb, così da consentire applicazioni ad elevate prestazioni o che richiedano elevata densità di codice). E' inoltre implementata l’estensione NEON per l’accelerazione hardware, mediante MAC 32x16 singolo-ciclo, di calcoli in matematica a 16 bit fixed-point. La CPU dispone di memorie cache interne (16 kbyte) per dati e programmi separati ed interfaccia AHB per l’accesso allo spazio di memoria esterno (che include tra l’altro 8 kbyte di memoria RAM e 64 kbyte di ROM built-in); dispone di MMU e write buffer (16 word data buffer e 4 word address buffer), quest’ultimo impiegato per scritture verso locazioni non cacheable o verso le cache (quando queste siano configurate in modalità write-through o in caso di write miss in modalità write-back).

La cache è di tipo 4-way set-associative con lunghezza di linea di 32 byte e supporto per virtual index, virtual tag e indirizzamento mediante Modified Virtual Address (MVA); la cache dati supporta le modalità writethrough e write-back. La MMU implementa una singola TLB unificata a 2 livelli con mapping per pagine di dimensione da 1 kbyte (tiny pages) a 1 Mbyte (sections); la tabella è invalidabile e supporta lockdown mediante programmazione di appositi registri. Per scopi di debug, la CPU dispone di Embedded Trace Buffer (4 kbyte) internamente connesso alla porta Embedded Trace Macrocell (ETM); software dedicati ETB-enabled sono richiesti per l’interpretazione del contenuto del trace buffer e il debug della CPU.

…E DSP

Oltre alla CPU ARM, i dispositivi OMAPL132 integrano un core DSP della serie TMS320C674x. Il core implementa un'architettura load-store con supporto per trasferimenti non-allineati a 32 bit e 64 bit e 2 data-path. L’insieme di istruzioni è di tipo VLIW. Sono disponibili 64 registri general-purpose organizzati in 2 register file, 6 ALU 32/40 bit e 2 Multiply Functional Units. Le ALU supportano operandi interi (32 bit) e floating point, con precisione singola (32 bit) o doppia (64 bit), implementando, ad esempio, fino a 4 addizioni per singolo ciclo di clock su operandi a singola precisione o fino a 2 addizioni su operandi a precisione doppia. La Multiply Functional Unit implementa, invece, moltiplicazioni multiple (in parallelo) a 32x32 bit, 16x16 bit o 8x8 bit e moltiplicazioni complesse. Il DSP dispone, inoltre, di controller dedicati per le memorie dati e programma di livello 1, indipendenti l’una dall’altra, e per una memoria condivisa di livello 2. Le memorie sono configurabili (anche parzialmente) come RAM o cache, di tipo one-way set-associative nel caso della memoria programma L1, di tipo two-way set-associative nel caso di quella dati L1 e di tipo four-way set-associative per quella L2.

La memoria programmi L1 è direct-mapped, read-allocate richiedendo il fetch di una linea intera di 32 byte in caso di miss in accesso in lettura. Analogo meccanismo è implementato anche dalla cache dati L1, con meccanismo di sostituzione di tipo LRU. Nel caso di miss in accesso in scrittura, invece, l’accesso è rimandato alla cache L2 mediante write buffer. La coerenza è assicurata mediante write-back. La cache di tipo L2, infine, è di tipo read-and-write allocate con algoritmo di sostituzione LRU; supporta, inoltre, le modalità writeback, writeback con invalidate e invalidate. E' previsto in generale un modulo di protezione della memoria che limiti l’accesso dei thread in esecuzione in funzione dei relativi permessi; il DSP supporta l’esecuzione in modalità utente e supervisor. Il trasferimento dati tra le memorie locali è accelerabile grazie all’impiego di un controller IDMA che assicura minore latenza operando in background rispetto alla CPU, mentre la gestione della banda disponibile verso ogni memoria è fornita dal modulo BWM che previene l’eventualità che un richiedente monopolizzi la risorsa.

UN INSIEME ESTESO DI PERIFERICHE…

CPU e DSP core sono corredati da un esteso insieme di periferiche per connettività, comunicazione e controllo. Tutti i core sono connessi da una fabric di interconnessione che include risorse centrali di switching multiple (SCR) e bridge multipli per assicurare trasferimenti a bassa latenza tra core master e slave. Oltre alle periferiche tradizionali come SPI, UART, I2C, USB, Ethernet, McASP, controller DDR2, SDRAM e Flash (sia NAND che NOR), etc., sono disponibili pure un controller EDMA3 e 2 sottosistemi PRU (Programmable Real-time Unit). Questi ultimi, in particolare, sono core micro-programmabili dotati di architettura Harvard, con 3 bus dati ed 1 bus istruzioni. Istruzioni e dati sono a 32 bit. L’architettura di I/O è di tipo load store con data flow di tipo registro-registro; sono accessibili 30 registri interni, 1 registro esterno e 1 registro general purpose. L’ALU è di tipo a interi insigne, con supporto per istruzioni aritmetiche di base (addizione, sottrazione), logiche (and, or, shift, set, min, max, etc.) e di controllo di flusso di programma (halt, branch, jump). La modalità di esecuzione è di tipo in-order non pipeplined. L'EDMA3 è, invece, un controller DMA multi-canale per trasferimenti dati programmati dall’utente tra due endpoint slave del dispositivo OMAP-L132 e di tipo memory-mapped. L’architettura del controller include logica dedicata per il riconoscimento di eventi atti ad iniziare il trasferimento configurato (supporta per questo le modalità manuale, evento esterno, chained e auto-triggered) e RAM per la memorizzazione dei parametri di questo.

…ED UN COMPLETO ECOSISTEMA SOFTWARE

L'OMAP-L132 C6-Integra è ovviamente supportato da un completo ecosistema software che consente di sfruttarne al meglio caratteristiche e prestazioni hardware. Oltre ai tradizionali tool di sviluppo e debug disponibili per i processori ARM e i DSP di TI (per questi ultimi in particolare, il classico IDE CodeComposer Studio basato su Eclipse), può essere interessante segnalare la libreria IMGLIB, una collezione di oltre 70 building block (forward ed inverse DCT, motion estimation, image istogram e thresholding, image correlation, error diffusion, pixel expansion) sotto Matlab Simulink per applicazioni di video ed image processing, con simulazione bit-level accurate del kernel DSP presente nell'OMAP-L132. IQMathLib, invece, è l’analogo adattamento, sempre sotto Simulink, della libreria IQMath per i DSP C64x per calcoli fixed-point in applicazioni real-time intensive (per le quali velocità di esecuzione e accuratezza elevata sono parametri cruciali), mentre il Basic Secure Boot Development Tools fornisce documentazione, utility ed esempi di riferimento per la generazione delle immagini di boot criptate per il boot in secure mode. Se poi si è alla ricerca di supporto di primo livello o interessati a condividere applicazioni e idee, si può sempre provare a dare uno sguardo alla TI’s Engineer-to- Engineer (E2E) Community e alla pagina TI Embedded Processors Wiki.