Costi contenuti, gamma estesa, buone prestazioni, ampia disponibilità di esempi di riferimento e tool di sviluppo gratuiti hanno reso i PIC uno dei dispositivi più diffusi tra sviluppatori ed hobbisti. Nati nella metà degli anni ’70 con il primo PIC1640 sviluppato dalla divisione microelettronica della General Instrument, nel lontano 2008 hanno superato quota 6 bilioni di dispositivi distribuiti nel mondo. Basati su architettura Harvard con spazio di indirizzamento separato per istruzioni e dati, sono microcontrollori RISC caratterizzati da un ridotto numero di istruzioni di lunghezza finita.

Le versioni più complesse integrano periferiche molteplici come RTCC (Real-Time Clock and Calendar), UART (Universal Asynchronous Receiver Transmitter), SPI (Serial Peripheral Interface) ed ADC (Analog to Digital Converter). Ma anche nei dispositivi più semplici, molte tra le applicazioni, anche se non supportate direttamente (come 1-Wire ed I2C, ad esempio), possono essere emulate mediante porte di I/O. Una conoscenza più approfondita di questa sezione è tuttavia fondamentale per utilizzarne al meglio le risorse. Per questo abbiamo deciso di occuparci di seguito in dettaglio dell’architettura degli stadi di ingresso/uscita dei PIC/dsPIC MicroChip.

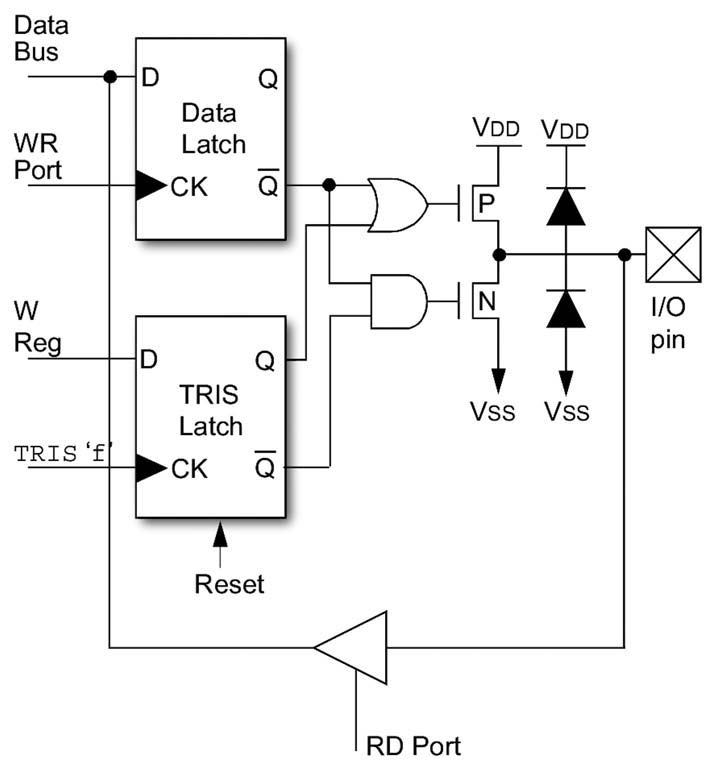

Moduli di I/O nei PIC10F

La figura 1 mostra lo schema di principio del circuito di I/O presente nei PIC10F, i dispositivi ad 8-bit più semplici della gamma realizzati in tecnologia flash a bassa dissipazione di potenza.

Figura 1: stadi di I/O nei PIC10F

Una sola porta a 4 bit è prevista; tre linee sono bidirezionali mentre la quarta è di solo ingresso. Le linee bidirezionali possono essere configurate separatamente come ingressi - nel qual caso lo stadio di driving viene forzato in alta impedenza - o come uscite. Come mostrato in figura 1, la sezione di I/O integra i due elementi di memoria latch che consentono di abilitare la porta e definiscono il livello pilotato sulla linea quando questa è attiva. Tali registri sono direttamente accessibili nello spazio di indirizzamento della CPU dalle istruzioni generiche. Quattro sono invece le funzioni specificatamente definite per la manipolazione dei pin di I/O: BCF (Bit Clear f), BSF (Bit Set f), BTFSC (Bit Test f, Skip if Clear) e BTFSS (Bit Test f, Skip if Set). Si noti che l’accesso in lettura alla porta consente di acquisire lo stato del pin e non dei latch. In ingresso è poi possibile abilitare resistori di pull-up o pull-down per evitare che la linea oscilli se non pilotata dall’esterno. Diodi di clamping verso massa e alimentazione sono previsti come protezione da sovratensioni. Ogni pin è in grado di erogare fino a 25 mA consentendo di pilotare direttamente, ad esempio, dei led. E’ prevista inoltre una interessante funzionalità di wake-up che consente di risvegliare automaticamente la CPU in corrispondenza di variazioni dello stato di una delle porte; in modalità sleep, i PIC10F riducono la dissipazione di potenza fino a 100 nA nel caso di alimentazione a 2 V. Due dei pin della porta (GP0 e GP1) oltre che come I/O servono anche come ingressi di clock e dato nella modalità di programmazione seriale del dispositivo. Il microcontrollore entra in tale modalità se i due pin sono forzati a ‘0’ mentre il segnale di Master Clear (~MCLR) viene rilasciato. Per migliorare l’immunità al rumore, i due ingressi sono dotati di un circuito con trigger di Schimdt. Alcune precauzioni devono essere tenute in considerazione utilizzando le porte di I/O. Da un punto di vista hardware, ad esempio, è importante evitare che, a seguito di erronea abilitazione, due pin pilotino contemporaneamente la stessa linea. Come mostrato infatti in figura 2, se i due livelli sono opposti si crea una connessione ‘diretta’ tra alimentazione e massa con il passaggio di corrente elevata che può danneggiare i dispositivi.

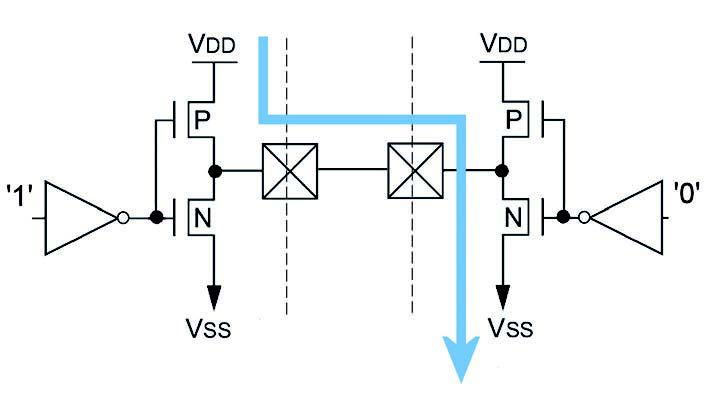

Figura 2: gli stadi di I/O dei PIC non supportano applicazioni wired-OR.

In altri termini, gli stadi di ingresso dei PIC non possono essere usati direttamente per applicazioni di tipo wired-OR. La seconda precauzione riguarda, invece, gli accessi in lettura alle porte. Alcune istruzioni come appunto BCF e BSF sono di tipo read-modify-write; la CPU legge dapprima lo stato della porta, aggiorna il valore del singolo bit oggetto dell’istruzione e quindi riscrive il risultato nei latch di uscita. Pertanto, se durante l’operazione una delle porte non direttamente interessate è configurata come ingresso, al termine dell’istruzione, il latch di uscita corrispondente sarà stato sovrascritto proprio con il valore letto in ingresso. Se in seguito il pin sarà abilitato, il livello pilotato in uscita potrebbe essere non noto. Piuttosto simile a quella descritta per i PIC10F, è l’architettura dei moduli di I/O dei dispositivi della seria PIC24H. In aggiunta alle caratteristiche presentate in precedenza, è prevista su alcuni I/O una modalità di Input Change Notification che consente di generare una interruzione al processore in corrispondenza di una variazione dello stato della linea in ingresso. Ogni I/O che supporta tale modalità dispone di stadi di pull-up che funzionano come sorgenti di corrente connessi al pin e quindi eliminano la necessità di resistori esterni quando utilizzati con circuiti come pulsanti o switch.

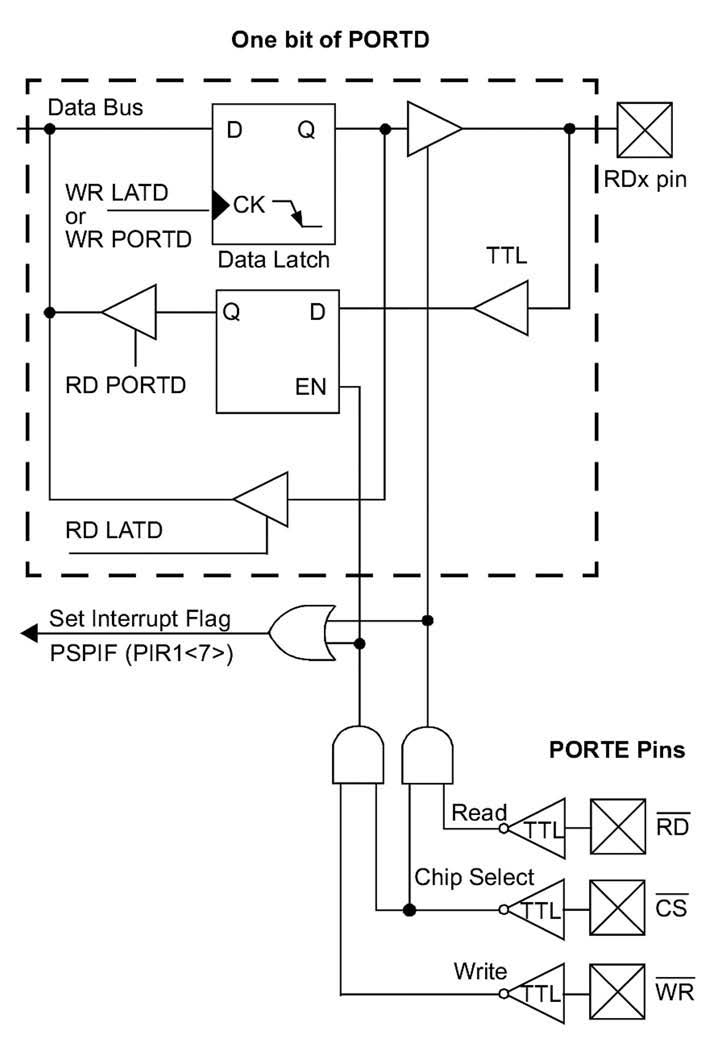

Porta parallela nei PIC18F4X20

Simile è pure la struttura degli stadi di I/O dei dispositivi della famiglia PIC18F. In funzione del modello selezionato sono disponibili, in questo caso, fino a 5 porte di ingresso/uscita ognuna ad 8-bit. Alcuni dei pin, tuttavia, sono condivisi con altre funzionalità e quindi non direttamente disponibili quando queste sono abilitate. Nei PIC18F4X20 interessante è soprattutto la possibilità di configurare la porta D come una porta parallela slave ad 8 bit con segnali accessori di controllo, come mostrato in figura 3.

Figura 3: una porta parallela nei PIC18F4X20

Alla porta è possibile accedere dal lato della CPU e dall’esterno in maniera asincrona in lettura e sincrona in scrittura. La porta può così essere connessa, ad esempio, direttamente al bus dati di un microcontrollore ad 8 bit realizzando una interfaccia per scambiare dati tra questo ed il PIC. Come per la maggior parte dei dispositivi di memoria, la scrittura dall’esterno avviene in corrispondenza di una transizione basso-alto su una delle linee CS o WR quando l’altra è attiva a ‘0’; la porta è invece abilitata in lettura quando i segnali CS e RD sono attivi bassi. Un semplice meccanismo di handshake è utilizzato per gestire gli accessi alla porta da entrambi i lati. Quando il PIC scrive nella porta un nuovo valore, viene attivata la flag OBF (Output Buffer Full Status); la flag viene invece rilasciata quando si accede in lettura alla porta dall’esterno. In questo modo il PIC può essere informato del fatto che i dati scritti verso l’uscita sono stati letti dal destinatario. Allo stesso modo una flag segnala al PIC la presenza di nuovi dati validi nei latch di ingresso della porta in seguito ad un accesso in scrittura a questa dall’esterno.

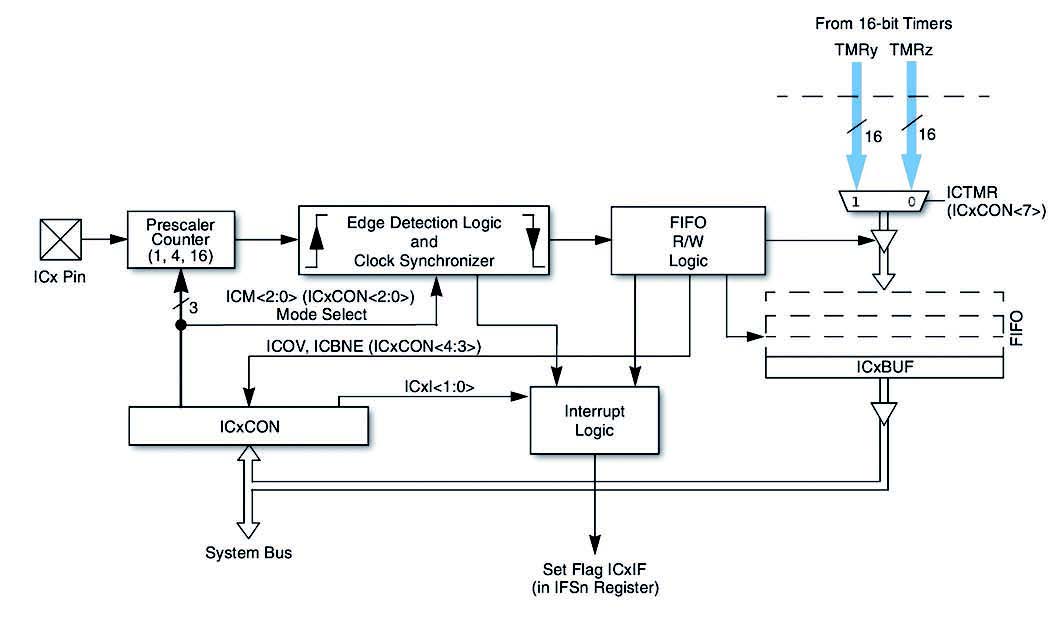

Periferiche di Input Capture ed Output Compare

Oltre a blocchi di I/O descritti in precedenza, alcuni PIC come, ad esempio i microcontrollori delle serie PIC24H o i dsPIC33FJ, dispongono di periferiche di Input Capture e Output Compare. Queste risultano spesse utili, ad esempio, in applicazioni che richiedono controlli di tipo PWM. La figura 4, in particolare, mostra il blocco di Input Capture dei dsPIC33FJ.

Figura 4: la periferica di Input Capture dei dsPIC33FJ

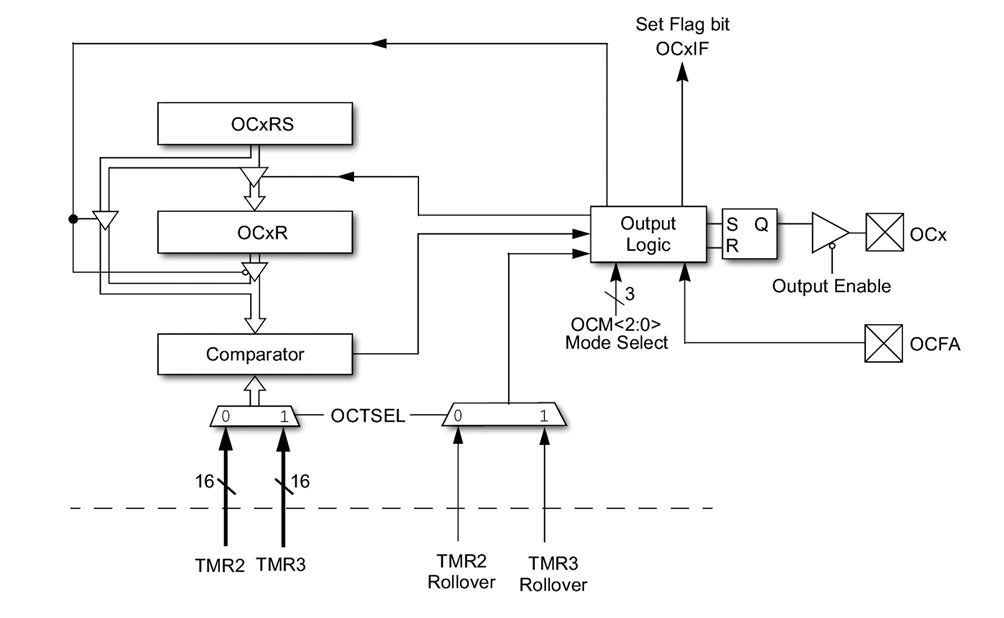

Il circuito permette di memorizzare il valore di un contatore interno free-running in corrispondenza di una qualsiasi transizione del segnale di ingresso (o, in maniera programmabile, di una delle due); è possibile abilitare un prescaler per ridurre la frequenza di acquisizione mentre la stessa base dei tempi può essere selezionata tra due dei timer disponibili a bordo del microcontrollore. Sono previste la possibilità di generare un’interruzione alla CPU ed una modalità automatica di wake-up di questa dagli stati di Sleep ed Idle in corrispondenza di un evento di capture. E’ presente un buffer di tipo FIFO in grado di memorizzare fino a quattro campioni del timer in corrispondenza di quattro successivi eventi; il livello di riempimento del buffer in corrispondenza del quale viene inviata l’interruzione alla CPU è configurabile. La figura 5 mostra, invece, il blocco di Output Compare dei PIC24H.

Figura 5: la periferica di Output Compare dei PIC24H

Il modulo confronta il valore configurato in un registro con quello di uno dei timer del microcontrollore; quando i due corrispondono viene aggiornato il valore della linea di uscita. E’ anche possibile generare contemporaneamente una interruzione alla CPU in corrispondenza dell’evento. Diverse sono le modalità operative tra cui:

» active-low/active high one-shot mode: viene inviato sulla linea un singolo impulso attivo basso/alto;

» toggle-mode: viene commutato il valore della linea;

» delayed one-shot mode: genera un impulso attivo alto con un ritardo programmabile;

» continous pulse mode: genera un impulse per ogni ciclo del timer;

» PWM mode con/senza protezione da fault: genera un’onda quadra con duty cycle e periodo variabili.

Alcuni dispositivi della famiglia PIC24H includono inoltre un controller DMA che consente di trasferire i data dalla memoria centrale al modulo Output Compare; è possibile definire così complesse sequenze di impulsi di controllo generati automaticamente in uscita senza necessità di intervento della CPU.