I chip F2MC-8FX della Fujitsu sono dotati di un’interessante periferica, il timer PPG, che consente di generare segnali analogici, oltre che funzionare come timer ad 8 e 16-bit. Nell’articolo saranno descritti i registri di configurazione ed un esempio pratico di utilizzo.

Negli ultimi anni si è assistito ad impressionante sviluppo dei dispositivi elettronici. In ogni caso, i microcontrollori ad 8-bit hanno continuato ad essere impiegati in diversi campi applicativi, grazie soprattutto alla loro flessibilità e disponibilità di periferiche integrate. Fujitsu, uno dei principali produttori di micro, ha riconosciuto questa esigenza aggiungendo tempo fa nuovi prodotti ad 8-bit alla sua gamma: serie MB95120 (prodotto in package 100-pin) e serie MB95160M (prodotto in package 64-pin). Tali prodotti rientrano nella famiglia di chip ad 8bit indicata col nome di F2MC-8FX. Oggetto di questo articolo è presentare una panoramica sul funzionamento del timer integrato PPG 8/16-bit. Sarà, inoltre, presentato un esempio pratico per generare in uscita al micro un’onda triangolare.

Figura 1: schema a blocchi della serie F2MC-8FX MB95160M

8/16-bit PPG: overview

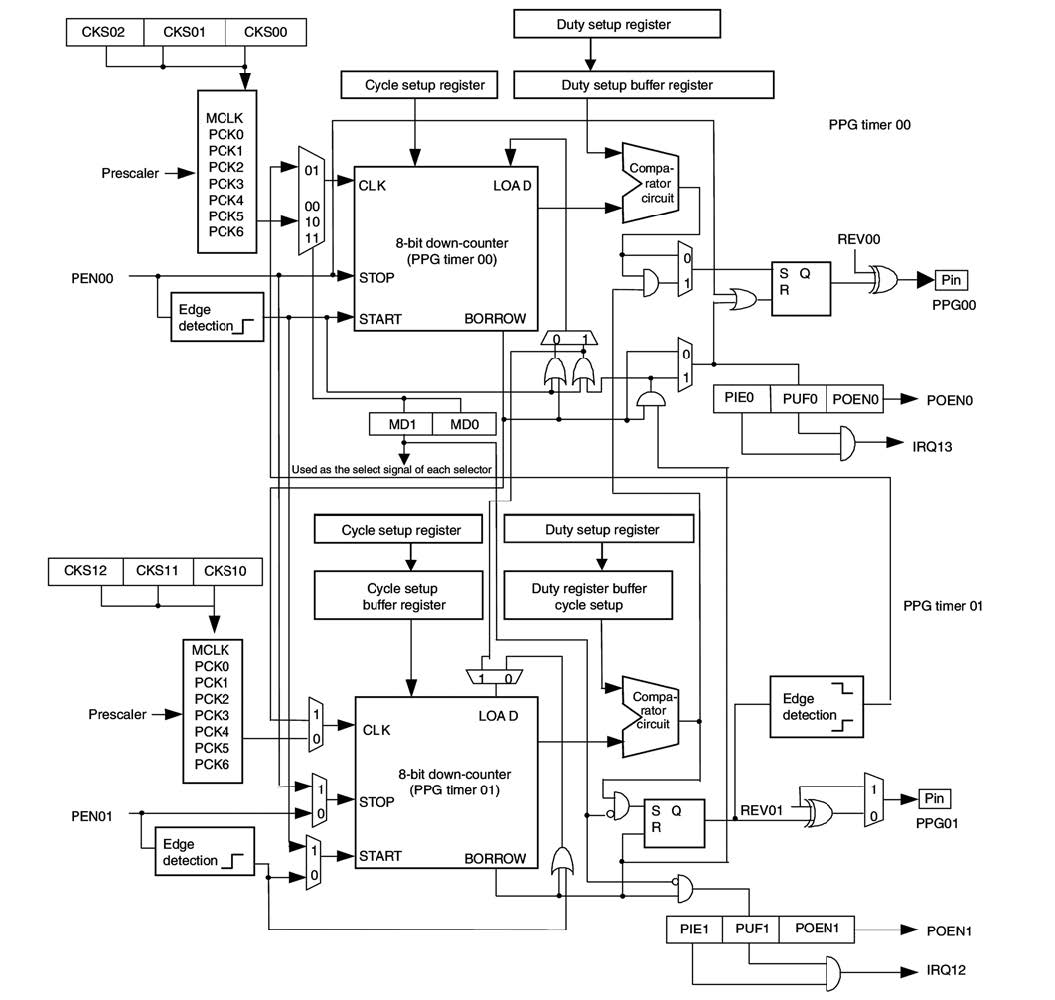

Lo schema a blocchi del timer 8/16-bit PPG è riportato in figura 2.

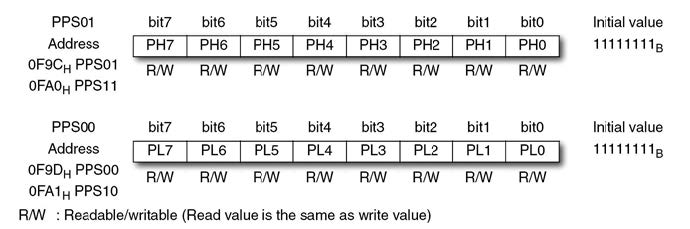

Figura 2: dettaglio dei singoli bit dei registro per l’impostazione del periodo (PPS0x).

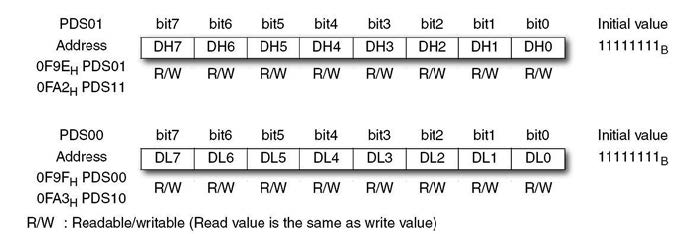

Figura 3: dettaglio dei singoli bit dei registro per l’impostazione del duty-cycle (PDS0x).

Esso è costituito da due blocchi fondamentali, che sono i contatori ad 8-bit, a ciascuno dei quali corrisponde un pin di uscita del micro (PPG00 e PPG 01). Nello schema a blocchi sono rappresentati anche tutti i registri impiegati per la sua configurazione. Tali registri consentono di utilizzare cinque differenti modalità operative:

■ 1-Due uscite indipendenti ad 8-bit PPG;

■ 2-Un’uscita ad 8-bit PPG ed un prescaler ad 8-bit.

La rilevazione dei fronti di salita e discesa del timer 01 diventano ingressi per il timer 00. Questo consente di variare la frequenza di conteggio;

■ 3-Un’uscita a 16-bit PPG. I due blocchi fondamentali sono collegati in cascata (Timer PPG 01 per gli 8 bit MSB e Timer PPG 00 per gli 8 bit LSB);

■ 4-Modalità PPG. In questo modo può essere generata un’uscita con duty-cycle variabile. In tale modalità è possibile utilizzare l’uscita come un D/A (ovviamente, con un’opportuna elettronica esterna);

■ 5-Modalità uscita invertita. Questa modalità può invertire il segnale di uscita.

Nel seguito sarà illustrato il funzionamento di ciascuno di essi.

Il registro di controllo (PC0x)

Il registro di controllo, la cui struttura base è rappresentata graficamente in figura 4, contiene i bit di configurazione dei timer.

Figura 4: schema a blocchi del timer 8/16 PPG.

Tabella 1: registri di controllo e configurazione dei timer 00 e 01.

I tre bit LSB (CKS12, CKS11, CKS10) servono per impostare la frequenza del clock che deve scandire il conteggio. Essa può essere scelta come una frazione di MCLK o FCH . Con la sigla MCLK si è indicato il master clock del processore, mentre FCH si è indicata la frequenza di clock dell’oscillatore. Il bit POEN1 è necessario per abilitare l’uscita del timer. Invece, il bit PUF1 serve per abilitare il rilevamento del borrow (prestito), qualora il timer sia configurato con conteggio all’indietro. Infine, il registro PC0x contiene anche il bit PIE1 con cui si abilita l’interrupt.

Il registro per l’impostazione del periodo (PPS0x)

La figura 2 riassume i bit utilizzati nel registro PPS0x. Tale registro serve per impostare la durata del periodo. La funzione di tale registro è differente a seconda della configurazione dei timer:

➤ In modalità 16-bit, il PPS01 è utilizzato per conservare gli 8 bit MSB del timer, mentre PPS00 quelli LSB. In tale modalità è necessario scrivere prima PPS01 e poi PPS00.

➤ In modalità 16-bit il massimo periodo è dato da: 65536 (0xFFFF) × Sorgente di clock.

➤ In modalità 8-bit il massimo periodo è dato da: 255 (0xFF) × Sorgente di clock.

Il registro per l’impostazione del periodo (PDS0x)

Per impostare il duty-cycle dell’onda quadra generata dall’uscita del PPG è necessario utilizzare i registri PDS0x. La figura 3 riporta un dettaglio dei registri PDS00 e PDS01. Per tali registri è importante tenere a mente alcune considerazioni:

➤ In modalità 16-bit, PDS01 rappresenta la parte alta mentre PDS00 quella bassa. In tal caso è necessario scrivere sempre prima la parte alta.

➤ Per impostare duty-cycle pari a 0% si deve scrivere 0x00, mentre per impostare un duty-cycle pari al 100% è necessario scrivere in PDS00/01 lo stesso valore dei registri PPS00/01.

➤ Se il valore scritto in PDS00/01 è superiore a quello in PPS00/01, allora l’uscita del timer sarà sempre al valore basso.

➤ Se il valore del duty cycle è modificato durante il normale funzionamento, la modifica avrà effetto dal successivo ciclo del PPG.

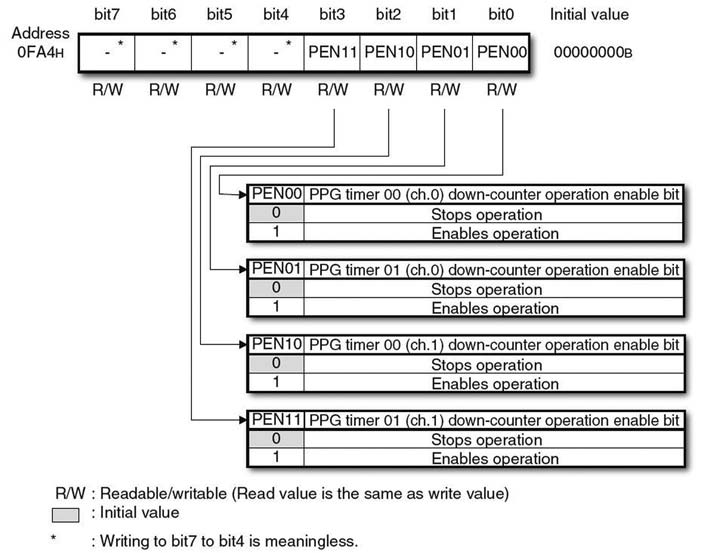

Figura 5: dettaglio dei singoli bit del registro per l’abilitazione dei timer (PPGS).

Il registro per l’impostazione del periodo (PPGS)

Il registro PPG Start ha il compito di avviare o arrestare il conteggio. Sono previsti quattro bit di abilitazione, per PPG presente nel chip (due generalmente) e per ogni canale PPG (due generalmente): PEN11, PEN10, PEN01 e PEN00. Tali bit sono raggruppati nel nibble basso del registro PPGS, come indicato in figura 7.

Il registro per l’impostazione del periodo (PPGS)

La periferica PPG offre anche la possibilità di controllare indipendentemente ogni singola uscita, tramite il registro REVC. Analogamente a quanto descritto per PPGS, ci sono 4 bit: REV11, REV10, REV01 e REV00.

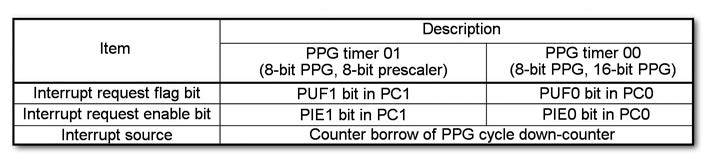

Gestione con interrupt

In figura 6 è riportato un dettaglio dei bit di controllo e delle sorgenti di interrupt del timer PPG. Quando il contatore (conteggio all’indietro) arriva a zero, il PPG imposta a 1 il bit per il rilevamento del borrow: tale bit è indicato con la sigla PUF, contenuto nel registro PC. Se il bit di abilitazione dell’interrupt (PIE) è impostato ad 1, allora sarà generata una richiesta di interrupt.

Figura 6: bit di controllo dell’interrupt PPG.

Descrizione operativa del timer PPG

Di seguito si riportano brevemente i passi di configurazione necessari per utilizzare la periferica PPG:

➤ impostazione delle porte di uscita (DDR2, DDR16);

➤ impostazione livello interrupt (ILR2, ILR3);

➤ selezione del clock, abilitazione dell’uscita e dell’interrupt (PC01);

➤ selezione del clock, abilitazione dell’uscita e dell’interrupt, selezione della modalità operativa (PC00);

➤ impostazione del periodo (PPS);

➤ impostazione del duty-cycle (PDS);

➤ impostazione della polarità (REVC);

➤ avvio del timer PPG (PPGS), Durante il normale funzionamento, per la gestione dell’interrupt bisogna seguire i seguenti passi:

➤ gestione interrupt;

➤ azzeramento del flag di richiesta (PC01:PUF1 e PC00:PUF0);

➤ avvio del timer (PPGS).

Nel listato 1 è riportato un esempio di codice C che mostra come configurare e gestire la periferica PPG.

#include “mb90340.h”

#define ppg_clock_div1 0x00 // 41.67ns @ 24MHz

#define ppg_clock_div2 0x01 // 83.33ns @ 24MHz

#define ppg_clock_div4 0x02 // 166.67ns @ 24MHz

#define ppg_clock_div8 0x03 // 333.33ns @ 24MHz

#define ppg_clock_div16 0x04 // 666.67ns @ 24MHz

#define ppg_clock_timebase 0x07 // timebase timer

volatile unsigned int i, p, x;

const int delay1 = 2000;

const int pause = 30000;

void Init8PPG0 (unsigned char LowDuration, unsigned char HighDuration, unsigned char clock)

{

PPGC0_PEN0 = 0; // stop PPG0

PPGC0_PE0 = 1; // enable PPG0 output

PPGC1_MD0 = 0; // set PPG01-mode to 2x 8bit

PPGC1_MD1 = 0;

PPGCS01_PCM = clock; // set clock select register channel 0

PRLL0 = LowDuration - 1; // set low duration in clock ticks

PRLH0 = HighDuration - 1; // set high duration in clock ticks

PPGC0_PEN0 = 1; // enable PPG0

}

void main(void)

{

ADER6 = 0x00; // input/output mode

TBTC = 0x80; // reset timebase timer, disable

// interrupt, intervall 1.024 ms @ 4 MHz

InitIrqLevels();

__set_il(7 // allow all levels

__EI // globaly enable interrupts

Init8PPG0(1, 2, ppg_clock_div1; //1 tick low, 2 ticks high, main clock/1

/*———— Onda triangolare (dimming) del canale 0 del PPG ————————-*/

while(1){

for (i=1; i<0xff; i++){

Init8PPG0(0xff-i, i, ppg_clock_div16); // “rising edge”

for (p=0; p<delay1; p++); // pause

}

for (x=0;x<pause;x++); // break

for (i=1; i<0xff; i++){

Init8PPG0(i, 0xff-i, ppg_clock_div16); // “falling edge”

for (p=0; p<delay1; p++); // pause

}

}

}

| Listato 1 |

In particolare, la funzione Init8PPG0() serve proprio per l’inizializzazione di tutti i registri descritti in precedenza e deve essere richiamata nel main prima di qualsiasi operazione sul timer. L’applicazione descritta serve per generare un’onda triangolare, che potrebbe essere utilizzata con funzione di dimmer. La funzione Init8PPG0() viene richiamata ripetutamente in due cicli separati che hanno il compito di generare la rampa di salita e quella di discesa dell’onda triangolare. Tali due cicli sono ripetuti all’infinito per generare un’onda periodica.

La possibilità di generare in uscita in modo molto semplice un segnale PWM è sicuramente una funzionalità utile in numerose applicazioni.